General Purpose list of instructions Processors Instructions are - PowerPoint PPT Presentation

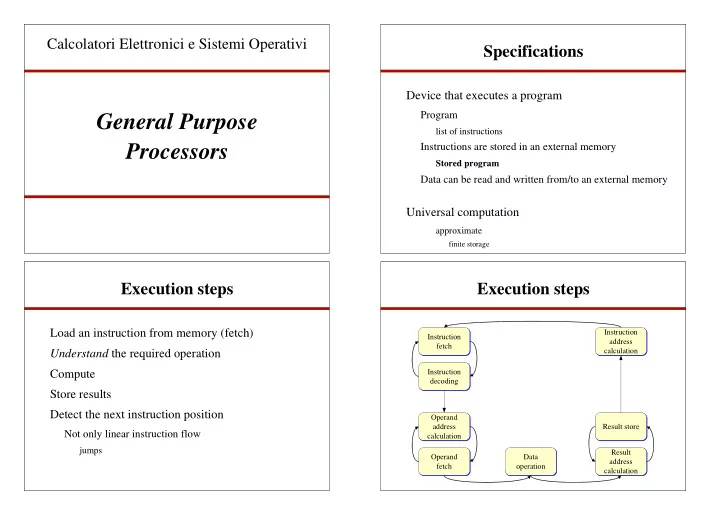

Calcolatori Elettronici e Sistemi Operativi Specifications Device that executes a program Program General Purpose list of instructions Processors Instructions are stored in an external memory Stored program Data can be read and written

Calcolatori Elettronici e Sistemi Operativi Specifications Device that executes a program Program General Purpose list of instructions Processors Instructions are stored in an external memory Stored program Data can be read and written from/to an external memory Universal computation approximate finite storage Execution steps Execution steps Load an instruction from memory (fetch) Instruction Instruction Instruction Instruction address address fetch fetch calculation Understand the required operation calculation Compute Instruction Instruction decoding decoding Store results Detect the next instruction position Operand Operand address Result store address Result store Not only linear instruction flow calculation calculation jumps Result Result Operand Data Operand Data address address fetch operation fetch operation calculation calculation

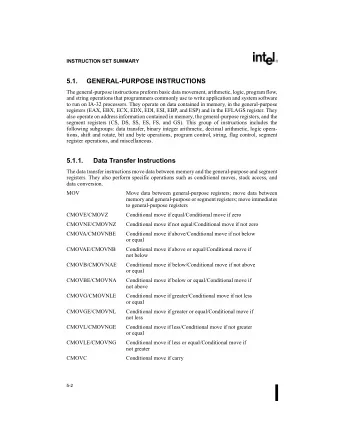

Execution steps Execution steps Instruction Fetch Operand address calculation Load instruction (portion) from memory Find operands position Instructions can have several formats and lenghts Register file Prefetch can hide memory latency and multiple lengths issue Memory Address can depend on register or memory content Decode More memory reads can be required Detect if other I-fetches are needed Operand fetch Decode instruction fields (operands, operation) Load operands from register file Load operands from memory Execution steps Instructions Data operation Data manipulation Perform computation through function unit Operation Result address computation Data transfer, Arithmetic, Logic, Shift Data type Find where result(s) must be stored Registers Integer Memory Binary, Decimal (BCD) Result store Floating point Save data Parallelism Instruction address calculation Scalar Vectorial Find position of the next instruction

Instructions Instructions Control flow Memory and IO access Transfer data to and from registers Conditional jumps Other instructions can have memory references Unconditional jumps Data instruction operands Return from function call Jump target Return from exception Other Exception generation Synchronization accesses Other Atomic read-modify-write Conditional storing Instruction repetition prefix Bus locking prefix Conditional execution Memory consistency model manipulation Memory and execution barriers Instructions Execution steps System management Instruction Instruction Instruction Instruction address address fetch fetch calculation Processor mode changes calculation Protection level Instruction Instruction Interrupt enabling/disabling decoding decoding Result store Result store Processor power state changes Operand and result Operand and result address address Memory model management calculation calculation Cache management System identification Operand Data Operand Data fetch operation fetch operation Special registers manipulation

ASM chart ASM chart RESET RESET PC <= START_ADDR PC <= START_ADDR General scheme INSTR 1 0 1 0 1 dp_ctrl_signals MEM[PC] = INSTR 1 MEM[PC] = INSTR 1 PC <= PC + incr PC <= PC + incr execution INSTR i Combinational: 0 1 Unconditional jump 0 1 dp_ctrl_signals MEM[PC] = INSTR i MEM[PC] = INSTR i PC <= PC + disp PC <= PC + disp execution MEM + DECODER INSTR j 0 1 0 1 MEM[PC] = INSTR j MEM[PC] = INSTR j dp_ctrl_signals execution 0 CONDITION 1 0 CONDITION 1 Conditional jump PC <= PC + incr PC <= PC + disp PC <= PC + incr PC <=PC + disp Structure Structure Timing: 1) dpREG � dpREG 2) PC � dpREG 3) PC � PC PC PC Control Signals Control Signals Status Flags Status Flags MEM MEM MEM MEM CTRL CTRL CONTROL UNIT DATAPATH CONTROL UNIT DATAPATH

ASM chart Structure RESET PC <= START_ADDR IR <= MEM[PC] 0 1 dp_ctrl_signals IR = INSTR 1 PC PC <= PC + incr Control Signals Combinational: IR 0 1 dp_ctrl_signals IR = INSTR i PC <= PC + disp DECODER Status Flags MEM MEM 0 1 IR = INSTR j CTRL dp_ctrl_signals 0 CONDITION 1 CONTROL UNIT DATAPATH PC <= PC + incr PC <=PC + disp Structure ASM chart RESET Timing: PC <= START_ADDR + incr Single cycle scheme 1) PC � IR IR <= MEM[ START_ADDR ] 2) dpREG � dpREG IR <= MEM[PC] 3) IR � dpREG 4) IR � PC 0 1 dp_ctrl_signals PC IR = INSTR 1 PC <= PC + incr Control Signals IR 0 1 dp_ctrl_signals Combinational: IR = INSTR i PC <= PC + disp DECODER Status Flags MEM MEM 0 1 IR = INSTR j CTRL dp_ctrl_signals CONDITION 0 1 CONTROL UNIT DATAPATH PC <= PC + incr PC <=PC + disp

ASM chart ASM chart RESET RESET Single cycle scheme Single cycle scheme PC <= START_ADDR + incr PC <= START_ADDR IR <= MEM[ START_ADDR ] with branch stall with branch stall IR <= MEM[PC] PC <= PC + incr IR <= MEM[PC] 0 1 dp_ctrl_signals 0 1 dp_ctrl_signals IR = INSTR 1 IR = INSTR 1 PC <= PC + incr PC <= PC + incr Wait state Wait state (for branches) (for branches) 0 1 dp_ctrl_signals 0 1 dp_ctrl_signals IR = INSTR i IR = INSTR i PC <= PC + disp PC <= PC + disp 0 1 0 1 IR = INSTR j IR = INSTR j dp_ctrl_signals dp_ctrl_signals 0 CONDITION 1 0 CONDITION 1 PC <= PC + incr PC <=PC + disp PC <= PC + incr PC <=PC + disp ASM chart ASM chart RESET RESET Multi-cycle scheme Multi-cycle scheme PC <= START_ADDR + incr PC <= START_ADDR IR <= MEM[ START_ADDR ] IR <= MEM[PC] IR <= MEM[PC] PC <= PC + incr Wait state Wait state (for branches) (for branches) 0 IR = INSTR 1 1 0 IR = INSTR 1 1 dp_ctrl_signals dp_ctrl_signals dp_ctrl_signals dp_ctrl_signals 0 1 0 1 IR = INSTR i IR = INSTR i PC <= PC + disp PC <= PC + disp 0 1 0 1 IR = INSTR j IR = INSTR j dp_ctrl_signals dp_ctrl_signals 0 CONDITION 1 0 CONDITION 1 PC <= PC + incr PC <=PC + disp PC <= PC + incr PC <=PC + disp 0 IR = INSTR i 1 0 IR = INSTR i 1 dp_ctrl_signals dp_ctrl_signals Multi-cycle instruction Multi-cycle instruction

Structure Multi-cycle control Pipeline Hard-wired control Control unit � FSM CTRL PC Control signals for MEM Datapath, PC, IR, other special registers IR Memories DEC Status signals (flags) from Control Signals Functional units Pipeline Flag registers MEM registers Memories Status Flags CONTROL UNIT DATAPATH Multi-cycle control Microprogrammed Processor IR Microprogrammed control Branch Control unit � microprogrammed FSM PC COMB1 µ-instruction MEM Control signals CAR +1 Datapath, PC, IR, other special registers Control Control Memories Store Store Next state info µ-instruction Control Conditions to check MEM Signals COMB3 Addresses for next µ-instructions COMB2 Status signals (flags) from Address generator Functional units Status Flags Flag registers CONTROL UNIT DATAPATH Memories

Microprogrammed Processor Microprogramming Next state � Simplify development state + 1 Decouples HW and ISA design branch from opcode Control design becomes SW development Control signals � Flexibility encoded Adaptable to changes in µ-architecture, timing, technology vertical µp not encoded Can make changes late in design cycle, or even in the field horizontal µp Can implement very powerful instruction sets PC just more control memory increment branch Microprogramming Microprogramming � Generality � Costly to implement Can implement multiple instruction sets on same machine Requires a fast control memory Can tailor instruction set to application � Compatibility � Slow Many micro-architectures, same instruction set

Microprogramming Microprogramming Horizontal microprogram Enhancements � no decoding µ-instructions are buffered and executed out-of-order � larger words ( � larger control store) Instructions are fetched and translated in µ-instructions Translation and execution no more in lock-step Vertical microprogram µ-instructions are cached in a special cache � smaller memory Special instructions sequences are recognized � need decoding Translated in special (optimized) µ-instructions sequences Some instructions are translated through random logic Hybrid HW decoders vs Memory “Diagonal” Microprogramming CPU - interface – Von Neumann Microprogrammed architectures examples IBM System/360 series (some: M30, M40, M50, M65) CTRL DP DEC PDP-11 DEC VAX-11 Zilog Z80 Motorola 68000 Intel x86 INSTR/DATA

CPU - interface – Harvard Datapath Register file symmetric CTRL DP Rz <= Rx op Ry � x, y, z, op asymmetric Function Units Adder, Multiplier, Divider, Logic functions, Shifter, ... cost, computational power, software complexity INSTR DATA Datapath Instruction Set Architecture Memory and registers model Size and meaning of registers Acc General purpose registers Reg Reg Special purpose registers File File Floating Point registers How registers can be used by operations ALU ALU Available instructions (Instruction Set) formats, operations, data types, addressing modes Accumulator Symmetric Operating modes architecture architecture standard, protection levels, special modes op Rx op Rd , Rs 1 , Rs 2

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.