Nanometer-Scale I nGaAs Field-Effect Transistors for THz and CMOS - PowerPoint PPT Presentation

Nanometer-Scale I nGaAs Field-Effect Transistors for THz and CMOS Technologies J. A. del Alamo Microsystems Technology Laboratories, MIT ESSDERC-ESSCIRC 2013 Bucharest, Romania, September 16-20, 2013 Acknowledgements: D. Antoniadis, A.

Nanometer-Scale I nGaAs Field-Effect Transistors for THz and CMOS Technologies J. A. del Alamo Microsystems Technology Laboratories, MIT ESSDERC-ESSCIRC 2013 Bucharest, Romania, September 16-20, 2013 Acknowledgements: • D. Antoniadis, A. Guo, D.-H. Kim, T.-W. Kim, D. Jin, J. Lin, N. Waldron, L. Xia • Sponsors: Intel, FCRP-MSD, ARL, SRC • Labs at MIT: MTL, NSL, SEBL 1

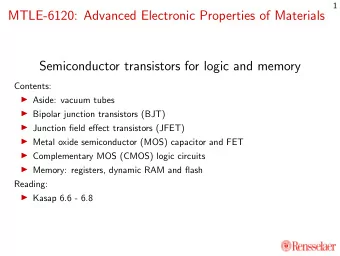

Outline 1. InGaAs HEMT today 2. InGaAs HEMTs towards THz operation 3. InGaAs MOSFETs: towards sub-10 nm CMOS 2

A bit of perspective… • Invention of AlGaAs/GaAs HEMT: Fujitsu Labs. 1980 • First InAlAs/InGaAs HEMT on InP: Bell Labs. 1982 • First AlGaAs/InGaAs Pseudomorphic HEMT: U. Illinois 1985 • Main attraction of InGaAs: RT μ e = 6,000~30,000 cm 2 /V.s Ketterson, EDL 1985 Mimura, JJAPL 1980 Chen, EDL 1982 3

I nGaAs Electronics Today UMTS-LTE PA module Chow, MTT-S 2008 40 Gb/s modulator driver 77 GHz transceiver Carroll, MTT-S 2002 Tessmann, GaAs IC 1999 Bipolar/E-D PHEMT process Single-chip WLAN MMIC, Morkner, RFIC 2007 Henderson, Mantech 2007 4

I nGaAs High Electron Mobility Transistor (HEMT) Modulation doping: 2-Dimensional Electron Gas at InAlAs/InGaAs interface 5

I nGaAs HEMT: high-frequency record vs. time Teledyne/MIT: f T =710 GHz 800 f T =688 GHz, f max =800 GHz f max =478 GHz 700 Chang, APEX 2013 600 (NCTU ) 500 on InP f T (GHz) substrate 400 Devices 300 fabricated at MIT 200 on GaAs substrate 100 0 1980 1990 2000 2010 Year • Highest f T of any FET on any material system • Best balanced f T and f max of any transistor on any material 6

I nGaAs HEMTs: circuit demonstrations 80 Gb/s multiplexer IC 10-stage 670 GHz LNA Wurfl, GAAS 2004 Leong, IPRM 2012 6-stage 600 GHz LNA Sarkozy, IPRM 2013 Tessmann, CSICS 2012 7

I nGaAs HEMTs on I nP used to map infant universe WMAP= Wilkinson Microwave Anisotropy Probe Launched 2001 Full-sky map of Cosmic Microwave Background radiation (oldest light in Universe) age of Universe: 13.73B years (±1%) 0.1 µm InGaAs HEMT LNA http://map.gsfc.nasa.gov/ Pospieszalski, MTT-S 2000 8

A closer look: I nGaAs HEMTs at MI T - QW channel (t ch = 10 nm): • InAs core • InGaAs cladding e = 13,200 cm 2 /V-sec - InAlAs barrier (t ins = 4 nm) - L g = 30 nm Kim, EDL 2010 9 9

L g = 30 nm I nGaAs HEMT V GS = 0.8 0.4 V Kim, EDL 2010 40 3 0.6 I D [mA/ m] 0.2 V H 21 0.4 2.0 0.2 30 2 U g 0 V 0.0 1.5 0.0 0.2 0.4 0.6 0.8 Gains [dB] V DS [V] MSG/MAG 20 1 g m [mS/ m] K 1.0 10 0 K 0.5 V DS =0.5 V, V GS =0.2 V V DS = 0.5 V 0 -1 0.0 9 10 11 12 10 10 10 10 -0.6 -0.4 -0.2 0.0 0.2 V GS [V] Frequency [Hz] • High transconductance: g m = 1.9 mS/ μ m at V DD =0.5 V • First transistor of any kind with both f T and f max > 640 GHz 10 10 10 10

How to reach f T = 1 THz? 1200 1000 30% reduction 1 THz in all the parasitics 800 600 f T [GHz] 400 V DS = 0.6 V Measured f T Modeled f T Model Projection 200 30 100 Kim, IEDM 2011 L g [nm] f T = 1 THz feasible by: scaling to L g ≈ 25 nm ~30% R and C parasitic reduction 11

Record f T I nGaAs HEMTs: megatrends x=0.53 • Over time: L g ↓ , In x Ga 1-x As channel x InAs ↑ • L g , x InAs saturated no more progress possible? 12

Record f T I nGaAs HEMTs: megatrends • Over time: t ch ↓ , t ins ↓ • t ch , t ins saturated no more progress possible? 13

Limit to HEMT barrier scaling: gate leakage current InGaAs HEMTs L g =40 nm V DS =0.5 V Kim, EDL 2013 At L g =30-40 nm, modern HEMTs are at the limit of scaling! 14

Solution: MOS gate! InGaAs HEMTs 10 -5 x! Al 2 O 3 (3 nm)/InP (2 nm)/InGaAs MOSFET L g =40 nm V DS =0.5 V Kim, EDL 2013 Need high-K gate dielectric: HEMT MOSFET! 15

I nGaAs MOSFETs with f T = 370 GHz (Teledyne/ MI T/ I ntelliEpi/ Sematech) Kim, APL 2012 50 H 21 40 H 21 • Channel: 10 nm In 0.7 Ga 0.3 As U g 30 Gains [dB] f T =370 GHz • Barrier: 1 nm InP + 2 nm Al 2 O 3 f T = 370 GHz MSG 20 • L g = 60 nm 10 f max = 280 GHz • g m = 2 mS/ μ m V DS =0.5 V 0 • R ON = 220 Ω . μ m 9 10 11 10 10 10 Frequency [Hz] 16

Historical evolution: I nGaAs MOSFETs vs. HEMTs Lin, IEDM 2013 Radosavljevic, IEDM 2009 Wieder, EDL 1981 Ren, EDL 1998 Progress reflects improvements in oxide/III-V interface 17

What made the difference? Oxide/ I I I -V interfaces with unpinned Fermi level by ALD ALD eliminates surface oxides that pin Fermi level: – First observed with Al 2 O 3 , then with other high-K dielectrics – First seen in GaAs, then in other III-Vs “Self cleaning” Clean, smooth interface without surface oxides Huang, APL 2005 18

I nterface quality: Al 2 O 3 / I nGaAs vs. Al 2 O 3 / Si Al 2 O 3 /Si Al 2 O 3 /InGaAs E v E c E v E c Brammertz, APL 2009 Werner, JAP 2011 Close to E c , Al 2 O 3 /InGaAs comparable D it to Al 2 O 3 /Si interface 19

I nGaAs n-MOSFET: best candidate for post-Si CMOS Si CMOS scaling seriously stressed Moore’s law threatened ? Intel microprocessors 20

21

CMOS scaling in the 21 st century Si CMOS has entered era of “power-constrained scaling”: Microprocessor power density saturated at ~100 W/cm 2 Pop, Nano Res 2010 Future scaling demands V DD ↓ 22

How to enable further V DD reduction? • Transistor is switch: • Goals of scaling: – reduce transistor footprint – reduce V DD – extract maximum I ON for given I OFF • The path forward: – increase electron velocity I ON ↑ use InGaAs! – tighten electron confinement S ↓ 23

Electron injection velocity: I nGaAs vs. Si Measurements of electron injection velocity in HEMTs: v inj E C E V Kim, IEDM 2009 Liu, Springer 2010 Khakifirooz, TED 2008 del Alamo, Nature 2011 • v inj (InGaAs) increases with InAs fraction in channel • v inj (InGaAs) > 2v inj (Si) at less than half V DD • ~100% ballistic transport at L g ~30 nm 24

L g = 30 nm I nGaAs HEMT – Subthreshold characteristics -3 10 V DS = 0.5 V Kim, EDL 2010 L g =30 nm -4 10 V DS = 0.05 V I D -5 10 I D , I G [A/ m] -6 10 V DS = 0.5 V -7 10 I G -8 10 V DS = 0.05 V -9 10 -1.0 -0.8 -0.6 -0.4 -0.2 0.0 0.2 0.4 V GS [V] • S = 74 mV/dec • Sharp subthreshold behavior due to tight electron confinement in quantum well 25

L g = 30 nm I nGaAs HEMT – Subthreshold characteristics I ON =0.52 mA/ μ m -3 10 V DS = 0.5 V Kim, EDL 2010 -4 10 V DS = 0.05 V I D -5 10 I D , I G [A/ m] -6 10 V DS = 0.5 V I OFF =100 nA/ μ m -7 10 I G -8 10 V DS = 0.05 V -9 10 -1.0 -0.8 -0.6 -0.4 -0.2 0.0 0.2 0.4 V GS [V] 0.5 V • S = 74 mV/dec • At I OFF =100 nA/ μ m and V DD =0.5 V, I ON =0.52 mA/ μ m 26

I nGaAs HEMTs: Benchmarking with Si FOM that integrates short-channel effects and transport: I ON @ I OFF =100 nA/µm, V DD =0.5 V Kim EDL 2010 InGaAs HEMT (MIT) IEDM 2008 del Alamo, Nature 2011 InGaAs HEMTs: higher I ON for same I OFF than Si 27

I nGaAs MOSFET: possible designs n + n + Recessed S/D QW-MOSFET Regrown S/D QW-MOSFET Nanowire MOSFET Trigate MOSFET 28

Self-Aligned I nGaAs QW-MOSFETs (MI T) • Scaled barrier (InP: 1 nm + HfO 2 : 2 nm) • 10 nm thick channel with InAs core • Tight S/D spacing (L side ~30 nm) • Process designed to be compatible with Si fab Lin, IEDM 2012 29

L g = 30 nm Self-aligned QW-MOSFET -3 320 10 L g =30 nm 280 -4 At V DS = 0.5 V: 10 240 S (mV/dec) I D (A/ m) -5 V DS =0.5 V 10 • g m = 1.4 mS/µm 200 -6 10 160 • S = 114 mV/dec -7 10 120 • R ON = 470 m 80 50 mV -8 10 -0.4 -0.2 0.0 0.2 V GS (V) Lin, IEDM 2012 30

Scaling and benchmarking 500 160 III-V FETs V DS = 0.5 V MIT HEMT 400 140 S min (mV/dec) Planar I on ( A/ m) Trigate This work 300 120 III-V FETs 200 100 MIT HEMT Planar I off =100 nA/ m 100 80 Trigate V DD =0.5 V This work 0 60 40 80 120 160 40 80 120 160 L g (nm) L g (nm) Lin, IEDM 2012 • Superior behavior to any planar III-V MOSFET to date • Matches performance of Intel’s InGaAs Trigate MOSFETs [Radosavljevic, IEDM 2011] 31

Sharp Subthreshold Characteristics From: • Aggressively scaled barrier • High quality interface: gate last process Barrier: InP (1 nm) + Al 2 O 3 (0.4 nm) + HfO 2 (2 nm) Lin, IEDM 2012 • S = 69 mV/dec at V DS = 50 mV • Close to lowest S reported in any III-V MOSFET: 66 mV/dec [Radosavljevic, IEDM 2011] 32

Regrown source/ drain I nGaAs QW-MOSFET on Si (HKUST) • MOCVD epi growth on Si wafer • n + -InGaAs raised source/drain • Self-aligned to gate • Composite barrier: InAlAs (10 nm) + Al 2 O 3 (4.6 nm) Zhou, IEDM 2012 33

Characteristics of L g = 30 nm MOSFET At V DS =0.5 V: • g m = 1.7 mS/µm • S = 186 mV/dec • R ON = 157 Ω .µm Zhou, IEDM 2012 34

Multiple-gate MOSFETs # gates ↑ improved electrostatics enhanced scalability FinFET Trigate Nanowire Chen, ICSICT 2008 35

I nGaAs Trigate MOSFET (I ntel) H FIN =40 nm Radosavljevic, IEDM 2011 Improved S over planar MOSFET on same heterostructure 36

I nGaAs Nanowire MOSFETs D = 30 nm D = 20 nm D = 28 nm Gu, IEDM 2012 Persson, DRC 2012 Zhao, IEDM 2013 37

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.