Low Frequency Noise in Advanced MOS Transistors Chia Yu Chen - PowerPoint PPT Presentation

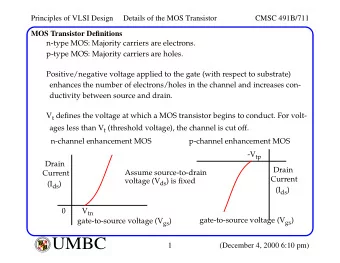

Low Frequency Noise in Advanced MOS Transistors Chia Yu Chen Department of Electrical Engineering Stanford University UC Berkeley EE298 12 Solid State Technology and Device Seminar 2010 11 19 Motivation Low Frequency Noise becomes

Gate bias • Dual ‐ channel behavior 0.006 Si/SiGe/Si p-HMOS Surf. charge Charge Density ( C/m 2 ) 1 E -1 8 S i: T C A D S i: T C A D Buried charge S i: m e a s . S i: m e a s . 1 E -1 7 S i/S iG e /S i: T C A D S i/S iG e /S i: T C A D Vd=-0.1V 1 E -1 9 S i/S iG e /S i: m e a s . 0.004 S i/S iG e /S i: m e a s . S id (A 2 /Hz) Sid ( A2/Hz ) 1 E -1 8 1 E -2 0 W /L = 1 0 u m /1 u m 1 E -1 9 W /L = 1 0 u m /1 u m 1 E -2 1 0.002 V d = -0 .5 V V d = -0 .5 V |V g |-|V th |= 0 .3 V V o v = 2 V 1 E -2 2 1 E -2 0 1 1 0 1 0 0 1 0 0 0 1 0 0 0 0 1 1 0 1 0 0 1 0 0 0 F re q u e n c y (H z ) F re q u e n c y (H z ) 0.000 -2.5 -2.0 -1.5 -1.0 -0.5 0.0 0.5 Gate voltage (V) – When buried channel dominant LF noise is reduced. 11/19/2010 C. ‐ Y. Chen UCB EE298 ‐ 12 Seminar 35

Gate bias • V g dependence Δμ 1E-7 SiGe p-HMOS Number fluc. 1E-8 Mobility fluc. Total noise S id /I d2 (1/Hz) 1E-9 Measurements Vd=-0.1V 1E-10 Δ N 1E-11 Δ N 1E-12 -2.5 -2.0 -1.5 -1.0 -0.5 0.0 0.5 Gate Voltage (V) – Weak inversion: Δμ – Medium/strong inversion: Δ N 11/19/2010 C. ‐ Y. Chen UCB EE298 ‐ 12 Seminar 36

Gate bias • I d dependence -7 7 10 10 Δμ SiGe p-HMOS -8 6 10 10 Vd=-0.1V -9 5 10 10 S id /I d2 ( 1/Hz ) ( gm/Id ) 2 (V -2 ) -10 4 10 10 Δ N -11 3 10 10 -12 2 10 10 -13 1 10 10 -14 0 10 10 -15 -1 10 10 -16 -2 10 10 1E-9 1E-8 1E-7 1E-6 1E-5 1E-4 Drain Currrent (A) – Weak inversion: Δμ – Medium/strong inversion: Δ N 11/19/2010 C. ‐ Y. Chen UCB EE298 ‐ 12 Seminar 37

Outline • Introduction • Methodology • SiGe channel Device schematic Gate bias Body bias • Size effect • Conclusions 11/19/2010 C. ‐ Y. Chen UCB EE298 ‐ 12 Seminar 38 38

Body bias • SiGe p ‐ HFET SiGe p-HMOS Vov=-0.3V 1E-20 Vd=-0.5V reverse S id (A 2 /Hz) 1E-21 1E-22 TCAD Mea. Vb=-0.4V Vb=-0.4V Vb=-0.2V Vb=-0.2V forward Vb=0V Vb=0V 1E-23 Vb=0.2V Vb=0.2V 10 100 1000 Frequency (Hz) SISPAD 2007, C. ‐ Y. Chen – LF noise in SiGe p ‐ HFET has strong body bias dependence. 11/19/2010 C. ‐ Y. Chen UCB EE298 ‐ 12 Seminar 39

Body bias • SiGe p ‐ HFET Si/SiGe/Si p-HM OS Hole density (cm -2 ) TCA D sim ulation 1E15 Surf.Buried Surf.Buried Vov=-0.3V 1E14 Vd=-0.5V Si cap layer SiGe channel 1E13 -0.4 -0.3 -0.2 -0.1 0.0 0.1 0.2 forward Body bias (V) reverse – Body bias changes carrier distribution in dual channels T ‐ ED 2008, C. ‐ Y. Chen 11/19/2010 C. ‐ Y. Chen UCB EE298 ‐ 12 Seminar 40

Body bias • SiGe p ‐ HFET Surface carrier density (cm -2 ) 1E16 Si/SiGe/Si p-HM OS Vov=-0.3V 1E-20 Vd=-0.5V Sid (A2/Hz) 1E15 less noisy more noisy 1E-21 Si cap layer hole density Sim ulated Sid M easured Sid 1E-22 1E14 -0.4 -0.3 -0.2 -0.1 0.0 0.1 0.2 forward Body bias (V) reverse – FL noise is mainly from surface channel. T ‐ ED 2008, C. ‐ Y. Chen 11/19/2010 C. ‐ Y. Chen UCB EE298 ‐ 12 Seminar 41

Body bias • Si p ‐ FET TCAD Mea. V b =-0.4V V b =-0.4V V b =-0.2V V b =-0.2V 1E-19 V b =0V V b =0V S id (A 2 /Hz) V b =0.2V V b =0.2V reverse Si pMOS 1E-20 Vov=-0.3V Vd=-0.5V 1E-21 forward 10 100 1000 Frequency (Hz) SISPAD 2007, C. ‐ Y. Chen – Si p ‐ MOS does not show body bias dependence. 11/19/2010 C. ‐ Y. Chen UCB EE298 ‐ 12 Seminar 42

Outline • Introduction • Methodology • SiGe channel • Size effect Device schematic Mechanism Gate bias • Conclusions 11/19/2010 C. ‐ Y. Chen UCB EE298 ‐ 12 Seminar 43 43

Device schematic • Scaled MOSFETs (small gate area) Cross view Top view L/W=40nm/70nm α oxide thickness~2.5nm Devices from G ‐ foundries – Only a few traps are involved. – Δ N predicts RTN; Δμ shows 1/f noise. 11/19/2010 C. ‐ Y. Chen UCB EE298 ‐ 12 Seminar 44

Outline • Introduction • Methodology • SiGe channel • Size effect Device schematic Mechanism Gate bias • Conclusions 11/19/2010 C. ‐ Y. Chen UCB EE298 ‐ 12 Seminar 45 45

Mechanism • Ig ‐ / Id ‐ RTN Ig A few trap/de ‐ trap Time G s D Id N+ N+ Time – Two types: Ig ‐ RTN and Id ‐ RTN. 11/19/2010 C. ‐ Y. Chen UCB EE298 ‐ 12 Seminar 46

Mechanism • Where are traps? 320 High-k metal gate nMOSFET (HfO2/TiN) 2 /Vs) 280 Electron mobility (cm 240 SiON 200 xx x 160 HfO 2 channel 120 gate 0.4 0.8 1.2 1.6 2.0 2.4 Interfacial layer thickness (nm) – Traps should be inside high ‐ κ oxide. 11/19/2010 C. ‐ Y. Chen UCB EE298 ‐ 12 Seminar 47

Mechanism • Trap/de ‐ trap charge trap charge de-trap (capture) (emission) 7.40E-012 I g (A) 7.20E-012 7.00E-012 Ef Et trapped de-trapped state state 1.60E-006 I d (A) 1.58E-006 1.56E-006 Track each other 0 10 20 30 Time (s) and TAT increase I d – Capture: V th and I g and TAT decrease I d – Emission: V th and I g 11/19/2010 C. ‐ Y. Chen UCB EE298 ‐ 12 Seminar 48

Mechanism • PBTI and RTN 1E-5 1E-7 Id (A) or Ig (A) Before stress Id Positive stress Negative stress 1E-9 Ig 1E-11 1E-13 -0.4 -0.2 0.0 0.2 0.4 0.6 0.8 1.0 Vg (V) – Consistent with RTN results. 11/19/2010 C. ‐ Y. Chen UCB EE298 ‐ 12 Seminar 49

Outline • Introduction • Methodology • SiGe channel • Size effect Device schematic Mechanism Gate bias • Conclusions 11/19/2010 C. ‐ Y. Chen UCB EE298 ‐ 12 Seminar 50 50

Gate bias • I g ‐ RTN Vg=1V - 1 1 6 .4 x 1 0 - 1 1 6 .0 x 1 0 - 1 1 5 .6 x 1 0 Ig (A) - 1 1 5 .2 x 1 0 Vg=0.9V Ef - 1 1 3 .6 x 1 0 Et - 1 1 3 .2 x 1 0 - 1 1 2 .0 x 1 0 Vg=0.8V - 1 1 1 .8 x 1 0 - 1 1 1 .6 x 1 0 0 5 1 0 1 5 2 0 2 5 Time (s) – V g increases: Time in high ‐ I g state increases. 11/19/2010 C. ‐ Y. Chen UCB EE298 ‐ 12 Seminar 51

Gate bias • I d ‐ RTN: Low Vg 2.30E-009 1E-19 2.25E-009 1E-20 Sid (A2/Hz) 2.20E-009 1/f 1E-21 Id (A) 2.15E-009 Vg=0.2V 1E-22 Vd=20m V 2.10E-009 Scaled nMOSFET 1E-23 L=50nm Vd=10mV Vg=0.2V 2.05E-009 W =70nm 1E-24 150 155 160 165 170 0.01 0.1 1 10 Time (s) Frequency (Hz) – Measurement still shows 1/f noise; Δμ model is dominant. 11/19/2010 C. ‐ Y. Chen UCB EE298 ‐ 12 Seminar 52

Gate bias • I d ‐ RTN: High gm bias condition 1E-15 Vd=10m V Vg=570m V 4.80E-007 1E-16 4.75E-007 Sid (A2/Hz) 1E-17 Vd=10m V Id (A) 1/f2 4.70E-007 Vg=570m V 1E-18 Scaled nM OSFET L=50nm 4.65E-007 1E-19 W =70nm 1E-20 4.60E-007 0.1 1 10 20 25 30 35 Tim e (s) Frequency (Hz) – RTN and Lorentzian shape are observed in high gm region. 11/19/2010 C. ‐ Y. Chen UCB EE298 ‐ 12 Seminar 53

Gate bias • I d ‐ RTN: High Vg 8.42E -007 V d=10m V V g=750m V 8.40E -007 1E-16 8.38E -007 Sid (A2/Hz) 1E-17 8.36E -007 Id(A) 8.34E -007 Vd=10m V 1/f 1E-18 8.32E -007 Vg=750m V 8.30E -007 1E-19 Scaled nM O SFET 8.28E -007 L=50nm 1E-20 W =70nm 8.26E -007 0 10 20 30 40 0.1 1 10 Frequency (Hz) Tim e (s) – 1/f noise is shown in a very scaled MOSFET: Δμ is dominant. 11/19/2010 C. ‐ Y. Chen UCB EE298 ‐ 12 Seminar 54

Gate bias • I d ‐ RTN: summary Δ N -6 2.0x10 Vd=10mV -6 Scaled nMOS 1.6x10 RTN L/W=50nm/70nm gm (1/ohm) -6 1.2x10 -7 8.0x10 1/f -7 4.0x10 0.0 -0.4 0.0 0.4 0.8 1.2 Δμ Δμ Vg (V) 1/f – RTN should be considered especially in high gm region. 11/19/2010 C. ‐ Y. Chen UCB EE298 ‐ 12 Seminar 55

Gate bias Sid/Id 2 • I d ‐ RTN: summary Δ N Lorentzian -6 2.0x10 Vd=10mV 1/f -6 Scaled nMOS 1.6x10 L/W=50nm/70nm gm (1/ohm) -6 1.2x10 Freq Sid/Id 2 -7 8.0x10 Sid/Id 2 -7 4.0x10 1/f 1/f 0.0 -0.4 0.0 0.4 0.8 1.2 Δμ Δμ Vg (V) Freq Freq – RTN should be considered especially in high gm region. 11/19/2010 C. ‐ Y. Chen UCB EE298 ‐ 12 Seminar 56

Outline • Introduction • The origin of LF noise • Methodology • SiGe channel • Size effect • Conclusions Summary Contributions Future work 11/19/2010 C. ‐ Y. Chen UCB EE298 ‐ 12 Seminar 57 57

Summary Bias SiGe H ‐ MOS (Lg~1um) Scaled MOS (Lg~40nm) Δμ Δμ Weak inversion model is dominant. model is dominant. Δ N model is important; Δ N model becomes High gm region (~ V dd /2) LF noise is mostly surface important; RTN should be effect. considered. Δ N is dominant in our Δμ model is dominant High V g condition device, but in general it can be technology dependence. 11/19/2010 C. ‐ Y. Chen UCB EE298 ‐ 12 Seminar 58

Summary Δ N model and (2) Δμ The origin of LF noise: (1) model. Methodology: TCAD simulations and noise measurements SiGe channel: Dual ‐ channel is important to explain the low frequency noise performance. Size effect: I g ‐ RTN is directly related to physical trapping or de ‐ trapping and the I d ‐ RTN reflects sensitivity to charge trapping as determined by g m . CMOS scaling: provides a new opportunity for LF noise study. 11/19/2010 C. ‐ Y. Chen UCB EE298 ‐ 12 Seminar 59

Contributions Detailed LF noise mechanisms in SiGe p ‐ HFET are proposed. LF noise mechanisms in scaled MOSFETs are measured and analyzed. Other parts: (1) LF noise mechanisms in high ‐ κ MOSFET, (2) A LF noise compact model in SiGe p ‐ HFET, (3) linearity of asymmetric channel doping for LDMOS, (4) linearity in GaN HEMTs, and (5) asymmetric FET scaling. 11/19/2010 C. ‐ Y. Chen UCB EE298 ‐ 12 Seminar 60

Future work Rethink “device noise” “distortion” and “reliability” 11/19/2010 C. ‐ Y. Chen UCB EE298 ‐ 12 Seminar 61

Publications [1] C. ‐ Y. Chen , Q. Ran, H. ‐ J. Cho, A. Kerber, Y. Liu, M. ‐ R. Lin, and R. W. Dutton, IRPS, 2011. [2] C. ‐ Y. Chen , C. ‐ C. Wang, Y. Ye, Y. Liu, Y. Cao, and R. W. Dutton, SASIMI, 2010. [3] C. ‐ Y. Chen , O. Tornblad, R. W. Dutton, IEEE Trans. on Microwave Theory and Techniques , Dec. 2009. [4] C. ‐ Y. Chen and R. W. Dutton, IEEE Design & Test of Computers , 2009. [5] C. ‐ Y. Chen , Y. Liu, J. Kim, R. W. Dutton, SISPAD 2009, Sept. 2009. [6] C. ‐ Y. Chen , O. Tornblad, R. W. Dutton, IEEE MTT ‐ S International Microwave Symposium Dig. (IMS), pp. 601 ‐ 604, 2009. [7] C. ‐ Y. Chen , Y. Liu, R. W. Dutton, J. Sato ‐ Iwanaga, A. Inoue, H. Sorada, SASIMI 2009, Sapporo, Japan, pp. 405 ‐ 409, March 2009. [8] C. ‐ Y. Chen , Y. Liu, R. W. Dutton, J. Sato ‐ Iwanaga, A. Inoue, H. Sorada, IEEE Trans. Electron Devices , July, 2008. [9] J. Kim, C. ‐ Y. Chen and R. W. Dutton, Journal of Computational Electronics, Jan. 2008. [10] C. ‐ Y. Chen , Y. Liu, R. W. Dutton, J. Sato ‐ Iwanaga, A. Inoue, H. Sorada, SASIMI , Sapporo, Japan, pp. 238 ‐ 241, Oct. 2007. [11] C. ‐ Y. Chen , Y. Liu, R. W. Dutton, J. Sato ‐ Iwanaga, A. Inoue, H. Sorada, Workshop on Compact Modeling (WCM) 2007 , San Jose, USA, March 2007. [12] J. Kim, C. ‐ Y. Chen , R. W. Dutton, SISPAD , Nov. 2007. [13] J. Kim, C. ‐ Y. Chen , R. W. Dutton, Proc. of 12th International Workshop on Computational Electronics (IWCE) , Oct. 2007. 11/19/2010 C. ‐ Y. Chen UCB EE298 ‐ 12 Seminar 62

Backup: Linearity analysis of lateral channel doping in RF power MOSFETs Chia ‐ Yu Chen Department of Electrical Engineering Stanford University UC Berkeley EE298 ‐ 12 Solid State Technology and Device Seminar 2010 ‐ 11 ‐ 19

Backup: Outline • Introduction • Quasi ‐ 1D structure • Realistic LDMOS structure • Conclusions Slide 64

Backup: Introduction (1 of 2) Linearity: ω ω Low distortion is one of the most important concerns for wireless communication systems. Analysis of the distortion generated by the device itself has been fairly limited. Slide 65

Backup: Introduction (2 of 2) Harmonic balance device simulations: A unique harmonic balance (HB) device simulator with the capability of including external circuitry is used. In the HB simulations, variations in device parameters are directly reflected in the final large signal RF performance. Slide 66

Backup: Quasi ‐ 1D structure (1 of 3) Device schematic: 0.5um gate length, 30nm oxide thickness. -3 uniform 8e16 cm Avoid 2D-effects. -3 1E18 uniform 2e17 cm Channel doping (cm -3 ) char. length 0.2um Very high source and drain char. length 0.3um dopings to avoid compensation effects at source and drain junctions. 1E17 Gate 4 cases: 2 uniform doping and 2 laterally graded. Graded Source Drain channel Test circuit consisting of bias 1E16 doping feeds and blocking capacitors on 0.0 0.1 0.2 0.3 0.4 0.5 input and output. Lateral location (um ) Slide 67

Backup: Quasi ‐ 1D structure (2 of 3) gm3/gm: IM3: -3 uniform 8e16cm -25 -3 uniform 2e17cm -30 char. length 0.3um char. length 0.2um 0 -35 Freq.=10MHz -40 Gm 3 /Gm IM3dBc -45 -50 uniform 8e16cm -3 -55 uniform 2e17cm -3 -60 char. length 0.3um char. length 0.2um -65 1.5 2.0 2.5 3.0 3.5 -1.5 -1.0 -0.5 0.0 Gate voltage (V) Log 10 ( V in ) First data point correlates to Different gm3/gm magnitudes for magnitude of gm3/gm minima. different cases. Shorter char. length / lower Devices were biased at gm3/gm uniform doping: higher IM3 at minima, close to overall best low input power lower IM3 at linearity. high input power. Slide 68

Backup: Quasi ‐ 1D structure (3 of 3) Field distribution: 5 4x10 Graded cases more uniform -3 unifrom 8e16cm field. Lateral electrical field (V/cm) -3 5 uniform 2e17cm 3x10 char. length 0.3um char. length 0.2um Smaller uniform doping more 5 2x10 Vg at gm 3/gm m in. uniform field. Vd: 2.0V 5 1x10 Uniform lateral field better linearity at higher power. 0 0.0 0.1 0.2 0.3 0.4 0.5 Lateral channel position (um ) Slide 69

Backup: Realistic LDMOS (1 of 4) Device schematic (based on Infineon 7 th generation design): Two different lightly doped drain 1 E 2 0 Lateral channel doping ( cm-3 ) regions: optimize on-resistance and breakdown voltage. 1 E 1 9 1 E 1 8 Source doping and lightly doped drain kept the same for all cases. 1 E 1 7 1 E 1 6 Four different lateral grading cases in c h a r. le n g th 0 .0 5 2 5 u m channel, defined through analytical 1 E 1 5 c h a r. le n g th 0 .0 6 2 5 u m expressions. c h a r. le n g th 0 .0 7 2 5 u m 1 E 1 4 c h a r. le n g th 0 .0 9 2 5 u m 0 .4 0 .6 0 .8 L a te ra l c h a n n e l lo c a tio n (u m ) Slide 70

Backup: Realistic LDMOS (2 of 4) gm3/gm: Test circuitry: 1.5 char. length 0.0525um char. length 0.0625um 1.0 char. length 0.0725um char. length 0.0925um 0.5 Gm3/Gm1 0.0 -0.5 -1.0 -1.5 -2.0 6.0 6.3 6.6 6.9 7.2 7.5 Gate voltage (V) Circuitry with internal and external matching and bias. Bias-point at gm3/gm minima. Infineon product PTF210451. Slide 71

Backup: Realistic LDMOS (3 of 4) IM3 at 2.14GHz: -30 -30 char. length 0.0525um char. length 0.0525um char. length 0.0625um char. length 0.0625um char. length 0.0725um char. length 0.0725um char. length 0.0925um char. length 0.0925um -40 -40 Freq. = 2.14GHz Freq. = 2.14GHz IM3dBc IM3dBc -50 -50 -60 -60 20 25 30 35 40 0.0 0.5 IM1 Log10(Vin) Effect of graded doping is significant the nonlinearities in capacitances will not swamp the studied effects at high frequency. More graded channel profile shows better linearity in the intermediate power regime. Slide 72

Backup: Realistic LDMOS (4 of 4) Vgs shifts from gm3/gm: char. 0.0525um ; shift 50m v Vgs shifts from gm3/gm -30 char. 0.0925um ; shift -30m v minima IM3 change is char. 0.0525um ; shift 0m v quite sensitive. char. 0.0925um ; shift -100m v Freq. = 2.14G H z -40 IM3dBc Different device designs give different IM3 that cannot be compensated for -50 by simply changing Vgs bias (Idq setting). -60 20 25 30 35 IM 1 Slide 73

Backup: Conclusions • A graded channel has better linearity for intermediate to high powers. By contrast, for increased back ‐ off, the situation is reversed. • Nonlinearities in intrinsic capacitances will not swamp the effect of graded channel doping at high frequency. • The effect of graded channel doping cannot be fully compensated for by adjusting the Idq bias point. • The analysis lays ground ‐ work for RF device optimization for improved linearity. Slide 74

Backup: Additional information (1 of 4) Quasi-1D structure: IdVgs -4 2.0x10 -3 1E-4 unifrom 8e16cm Drain current, linear scale (A/um) -4 1.8x10 -3 unifrom 2e17cm Drain current, log scale (A/um) 1E-5 char. length 0.3um -4 1.6x10 char. length 0.2um 0 1E-6 Vd=2.0V -4 1.4x10 1E-7 -4 1.2x10 Gm 3 /Gm -4 1E-8 1.0x10 -5 8.0x10 1E-9 uniform 8e16cm -3 -5 6.0x10 1E-10 uniform 2e17cm -3 -5 4.0x10 char. length 0.3um 1E-11 -5 2.0x10 char. length 0.2um 1E-12 0.0 0 1 2 3 4 1.5 2.0 2.5 3.0 3.5 Gate voltage (V) Gate voltage (V) Clearly different gm3/gm magnitudes for different cases. Shorter characteristic length and lower doping give larger gm3/gm magnitudes. Devices were biased at gm3/gm minima, close to overall best linearity for many applications. Slide 75

Backup: Additional information (2 of 4) Quasi-1D structure: velocity saturation: -30 0.0 -40 -0.5 Gm3/Gm IM3dBc -50 -1.0 -60 Uniform doping 2e17cm -3 -1.5 Uniform doping 2e17cm -3 w/ Vsat model -70 w/ Vsat model w/o Vsat model w/o Vsat model -2.0 -80 2.6 2.8 3.0 3.2 3.4 3.6 -25 -20 -15 -10 -5 0 5 10 Gate voltage (V) IM1 When Vsat model is not included: 1. gm3/gm shifts to a smaller magnitude. 2. IM3 is much lower, both initially and for high powers. Slide 76

Backup: Additional information (3 of 4) Realistic LDMOS: IM3 at 10MHz -30 -30 Freq.=10MHz Freq.=10MHz -35 -35 -40 -40 -45 -45 IM3dBc IM3dBc -50 -50 char. length 0.0525um char. length 0.0525um -55 -55 char. length 0.0625um char. length 0.0625um char. length 0.0725um char. length 0.0725um -60 -60 char. length 0.0925um char. length 0.0925um -65 -65 -10 -5 0 5 10 15 20 -1.4 -1.2 -1.0 -0.8 -0.6 -0.4 -0.2 0.0 IM1 Log10(Vin) First, separate nonlinearities in static IV from capacitive effects low freq. 10MHz. More graded channel profile shows better linearity in intermediate power regime. Slide 77

Backup: Additional information (4 of 4) Realistic LDMOS: two sweet spots -20 At high power, the compressing Shift -50m V from gm 3/gm m in. non-linearity along the load-line -30 gm 3/gm m in. will dominate; the curves merge. -40 Lower Vgs two sweet-spots appear. IM3dBc -50 -60 Ids (A) -70 -80 -90 -10 -5 0 5 10 15 20 Vds (V) IM 1 Slide 78

Backup: GaN HEMT structure GaN HEMT structure Lg=0.5um 11/23/2010 GaN HEMT project 79

Backup: Id ‐ Vgs, GaN HEMT TCAD simulation results 0.0012 1E-3 w/o Hydrodynamics w/ Hydrodynamics 0.0010 1E-4 0.0008 Id (A/um) Id (A/um) 0.0006 1E-5 w/o Hydrodynamics w/ Hydrodynamics 0.0004 1E-6 0.0002 0.0000 1E-7 -7 -6 -5 -4 -3 -2 -1 0 1 -5 -4 -3 -2 -1 0 1 Vg (V) Vg (V) 11/23/2010 GaN HEMT project 80

Backup: Gm3/Gm1, GaN HEMT 40 20 Gm3/Gm1 w/o Hydrodynamics w/ Hydrodynamics 0 Gm3/Gm1 min.:Vg=-4.9047V -20 -5 -4 -3 -2 Vg (V) 11/23/2010 GaN HEMT project 81

Backup: Linearity, GaN HEMT 1E-8 Id1 at f1 1E-10 Id3 at 2f1-f2 GaN HEMT Id(A) Vd=28V 1E-12 Vg=-4.91V (Gm3/Gm1 min.) 1E-14 1E-16 0.01 0.1 Vg(V) 11/23/2010 GaN HEMT project 82

Backup: The origin of LF noise • Δ N model Id time: one trap RTN Time Sid/Id 2 freq.: Δ N Freq Id time: a lot of traps 1/f noise Time Sid/Id 2 freq.: Freq 11/19/2010 C. ‐ Y. Chen UCB EE298 ‐ 12 Seminar 83 83

Backup: Statistics • Statistical results About 12% MOSFETs show RTN: 9% Ig ‐ RTN, 2% I d ‐ RTN, ‐ /I d ‐ RTN. and 1% I g The statistical results are from 1000 devices with the same technology and structures. 11/19/2010 C. ‐ Y. Chen UCB EE298 ‐ 12 Seminar 84

Backup: Gate bias • I g ‐ RTN Vg=1V - 1 1 6 .4 x 1 0 - 1 1 6 .0 x 1 0 10 - 1 1 5 .6 x 1 0 Ig (A) - 1 1 5 .2 x 1 0 Vg=0.9V - 1 1 3 .6 x 1 0 1 - 1 1 3 .2 x 1 0 D ev ice 1 0.1 - 1 1 D ev ice 2 2 .0 x 1 0 Vg=0.8V D ev ice 3 - 1 1 1 .8 x 1 0 D ev ice 4 0.01 - 1 1 1 .6 x 1 0 0.6 0.7 0.8 0.9 1.0 1.1 1.2 0 5 1 0 1 5 2 0 2 5 Time (s) V g (V ) – V g increases: Time in high ‐ I g state increases. 11/19/2010 C. ‐ Y. Chen UCB EE298 ‐ 12 Seminar 85

Backup: TCAD • I d ‐ RTN: High gm bias condition Trap/de-trap – TCAD simulations confirm the origin of RTN can be from one ‐ trap/de ‐ trap. 11/19/2010 C. ‐ Y. Chen UCB EE298 ‐ 12 Seminar 86

Backup: Motivation Integrated sensors Bio ‐ implant system Portable electronics Device Noise Ultra ‐ low power circuits Bio/silicon interfaces Transistor reliability SRAM yield Noise: key issue for the future electronic system development. 11/09/2010 C. ‐ Y. Chen UCB seminar 87

Backup: Trap distribution (1 of 2) U-shape Energy (eV) L/H H/L Space (um) – Space: from gate to Si can be low-high or high-low. – Energy: distribution is a U-shape in log-scale. R. Jayaraman et al . IEEE T-ED , vol.36, no. 9, pp. 1773-1782, Sept., 1989. H. Wong et al . IEEE T-ED , vol.37 no. 7, pp. 1743-1749, July, 1990. 11/19/2010 C. ‐ Y. Chen UCB EE298 ‐ 12 Seminar 88

Backup: Trap distribution (2 of 2) • V g dependence flat ∝ 1/V ov 2 – V g dependence shows flat region in weak inversion regime. – In the U-shape distribution V g dependence is less sensitive compared with uniform distribution. K. K. Hung et al . IEEE T-ED , vol.37, no. 5, pp. 1323-1333, May, 1990. Y. Liu et al . SISPAD 2006 , pp. 99-102, 2006. 11/19/2010 C. ‐ Y. Chen UCB EE298 ‐ 12 Seminar 89

Backup: Numerical method (1 of 2) – Physical model – Impedance field method (IMF) Current fluctuatio n at kth electrode A k r Injected current at r in the device 2 ( s ) S A r S r dv in [5] A. McWhorter, Semiconductor Surface Physics , PA, Univ. Pennsylvania Press,1957, pp. 207-208. [6] W. Shockley et al., Quantum Theory of Atoms, Molecules and Solid State , NY: Academic, 1966, pp. 537-563. 11/19/2010 C. ‐ Y. Chen UCB EE298 ‐ 12 Seminar 90

Backup: Numerical method (2 of 2) • Hooge mobility fluctuation ( Δμ model) – Bulk phonon scattering – Empirical equation – Numerical approach: Post process Hooge model is empirical the post process with simulated parameters/reasonable α H is used. [7] F. N. Hooge, IEEE T-ED , vol.41, no. 11, pp. 1926-1935, Nov., 1994. 11/19/2010 C. ‐ Y. Chen UCB EE298 ‐ 12 Seminar 91

Backup: Unified model (1 of 4) The fluctuating oxide charge density △ Q ox is equivalent to a variation in the flat-band voltage The fluctuation in the drain current yields Fluctuation of Num. Fluctuation of correlated mobility The first term in the parentheses is due to fluctuating number of inversion carriers and the second term to correlated mobility fluctuations. 11/19/2010 C. ‐ Y. Chen UCB EE298 ‐ 12 Seminar 92

Backup: Unified model (2 of 4) The power spectral density of the flat-band voltage fluctuations is calculated by summing the contributions from all traps in the gate oxide. Fermi ‐ Dirac distribution z x y Semiconductor 11/19/2010 C. ‐ Y. Chen UCB EE298 ‐ 12 Seminar 93

Backup: Unified model (3 of 4) The product f (E)(1- f (E)) is sharply peaked around the quasi- Fermi level If the Fermi-level is far above or below the trap level, the trap will be filled or empty. All empty f(E) 1-f(E) Fluctuations All filled 11/19/2010 C. ‐ Y. Chen UCB EE298 ‐ 12 Seminar 94

Backup: Unified model (4 of 4) Lorentzian spectrum The trapping time constant (quantum tunneling) Tunneling attenuation length 11/19/2010 C. ‐ Y. Chen UCB EE298 ‐ 12 Seminar 95

Backup: High ‐ κ f=1Hz • Numerical approach High- κ SiON Si f=1e4Hz j Different affinities and tunneling are considered : 1 × 10 -8 cm SiO 2 : 2. 1 × 10 -8 cm 1/ γ HfO 2 [9] Y. Liu et al . SISPAD 2006 , pp. 99-102, 2006. 11/19/2010 C. ‐ Y. Chen UCB EE298 ‐ 12 Seminar

Backup: Noise scaling (1 of 2) • Scaling trend: general trend – SiO 2 trap density is much smaller than that of HfO 2 . – 1/f noise increases much faster than the thermal noise when size scales down. 11/19/2010 C. ‐ Y. Chen UCB EE298 ‐ 12 Seminar 97

Backup: Noise scaling (2 of 2) • Scaling trend: traps at gate edge – High trap density in the gate edge region. – In the scaled devices traps in the gate edge becomes 2 increases significantly. important so S id /I d [14] Y. Yasuda et al., IEEE T-ED , vol.55, no. 1, pp. 417-422, Jan., 2008. 11/19/2010 C. ‐ Y. Chen UCB EE298 ‐ 12 Seminar 98

Backup: Halo doping – Halo doping profiles suppress the short channel effect. – The same amount of electrons greater Δ I d in halo. – Reduced inversion carrier density in the halo regions. [8] Y. Liu et al . SISPAD 2006 , pp. 99-102, 2006. 11/19/2010 C. ‐ Y. Chen UCB EE298 ‐ 12 Seminar 99

Backup: Metal gate + - + - Poly SiGe High- κ (TiN) – The lowering of the 1/f noise: observed in the strong inversion regime. – Traps and charges at the gate dielectric interface: better screened by a metal gate alleviate remote phonon scattering. [15] E. Simoen et al., IEEE T-ED , vol.40, pp. 2054-2059, 1993. 11/19/2010 C. ‐ Y. Chen UCB EE298 ‐ 12 Seminar 100

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.