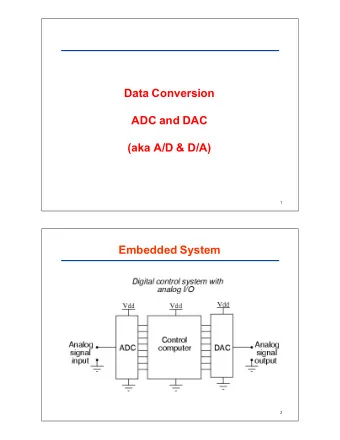

Introduction M. B. Patil, IIT Bombay Introduction * Real signals - PowerPoint PPT Presentation

Introduction M. B. Patil, IIT Bombay Introduction * Real signals (e.g., a voltage measured with a thermocouple or a speech signal recorded with a microphone) are analog quantities, varying continuously with time. M. B. Patil, IIT Bombay

DAC using binary-weighted resistors: Example (from Gopalan) I 7 V R A 7 R 7 = R I 1 A 1 R f R 1 = 2 6 R I 0 I A 0 R 0 = 2 7 R V A * If R f = R , what is the resolution (i.e., ∆ V A corresponding to the input LSB changing from 0 to 1 with other input bits constant)? R f S 7 2 7 + · · · + S 1 2 1 + S 0 2 0 � � V A = − V R 2 N − 1 R M. B. Patil, IIT Bombay

DAC using binary-weighted resistors: Example (from Gopalan) I 7 V R A 7 R 7 = R I 1 A 1 R f R 1 = 2 6 R I 0 I A 0 R 0 = 2 7 R V A * If R f = R , what is the resolution (i.e., ∆ V A corresponding to the input LSB changing from 0 to 1 with other input bits constant)? R f S 7 2 7 + · · · + S 1 2 1 + S 0 2 0 � � V A = − V R 2 N − 1 R 5 V 5 V R R f → ∆ V A = R = 2 8 − 1 × 1 = 128 = 0 . 0391 V . 2 N − 1 M. B. Patil, IIT Bombay

DAC using binary-weighted resistors: Example (from Gopalan) I 7 V R A 7 R 7 = R I 1 A 1 R f R 1 = 2 6 R I 0 I A 0 R 0 = 2 7 R V A M. B. Patil, IIT Bombay

DAC using binary-weighted resistors: Example (from Gopalan) I 7 V R A 7 R 7 = R I 1 A 1 R f R 1 = 2 6 R I 0 I A 0 R 0 = 2 7 R V A * What is the maximum output voltage (in magnitude)? M. B. Patil, IIT Bombay

DAC using binary-weighted resistors: Example (from Gopalan) I 7 V R A 7 R 7 = R I 1 A 1 R f R 1 = 2 6 R I 0 I A 0 R 0 = 2 7 R V A * What is the maximum output voltage (in magnitude)? V A = − V R R f S 7 2 7 + · · · + S 1 2 1 + S 0 2 0 � � . 2 N − 1 R M. B. Patil, IIT Bombay

DAC using binary-weighted resistors: Example (from Gopalan) I 7 V R A 7 R 7 = R I 1 A 1 R f R 1 = 2 6 R I 0 I A 0 R 0 = 2 7 R V A * What is the maximum output voltage (in magnitude)? V A = − V R R f S 7 2 7 + · · · + S 1 2 1 + S 0 2 0 � � . 2 N − 1 R Maximum V A (in magnitude) is obtained when the input is 1111 1111 . M. B. Patil, IIT Bombay

DAC using binary-weighted resistors: Example (from Gopalan) I 7 V R A 7 R 7 = R I 1 A 1 R f R 1 = 2 6 R I 0 I A 0 R 0 = 2 7 R V A * What is the maximum output voltage (in magnitude)? V A = − V R R f S 7 2 7 + · · · + S 1 2 1 + S 0 2 0 � � . 2 N − 1 R Maximum V A (in magnitude) is obtained when the input is 1111 1111 . 5 5 = 5 × 255 | V A | max = � 2 0 + 2 1 + · · · + 2 7 � � 2 8 − 1 � 128 × 1 × = 128 × 128 = 9 . 961 V . M. B. Patil, IIT Bombay

DAC using binary-weighted resistors: Example (from Gopalan) I 7 V R A 7 R 7 = R I 1 A 1 R f R 1 = 2 6 R I 0 I A 0 R 0 = 2 7 R V A M. B. Patil, IIT Bombay

DAC using binary-weighted resistors: Example (from Gopalan) I 7 V R A 7 R 7 = R I 1 A 1 R f R 1 = 2 6 R I 0 I A 0 R 0 = 2 7 R V A * Find the output voltage corresponding to the input 1010 1101 . M. B. Patil, IIT Bombay

DAC using binary-weighted resistors: Example (from Gopalan) I 7 V R A 7 R 7 = R I 1 A 1 R f R 1 = 2 6 R I 0 I A 0 R 0 = 2 7 R V A * Find the output voltage corresponding to the input 1010 1101 . V A = − V R R f � S 7 2 7 + · · · + S 1 2 1 + S 0 2 0 � . 2 N − 1 R M. B. Patil, IIT Bombay

DAC using binary-weighted resistors: Example (from Gopalan) I 7 V R A 7 R 7 = R I 1 A 1 R f R 1 = 2 6 R I 0 I A 0 R 0 = 2 7 R V A * Find the output voltage corresponding to the input 1010 1101 . V A = − V R R f � S 7 2 7 + · · · + S 1 2 1 + S 0 2 0 � . 2 N − 1 R = − 5 = − 5 × 173 2 7 + 2 5 + 2 3 + 2 2 + 2 0 � � 128 × 1 × 128 = − 6 . 758 V . M. B. Patil, IIT Bombay

DAC using binary-weighted resistors: Example (from Gopalan) I 7 V R A 7 R 7 = R I 1 A 1 R f R 1 = 2 6 R I 0 I A 0 R 0 = 2 7 R V A M. B. Patil, IIT Bombay

DAC using binary-weighted resistors: Example (from Gopalan) I 7 V R A 7 R 7 = R I 1 A 1 R f R 1 = 2 6 R I 0 I A 0 R 0 = 2 7 R V A * If the resistors are specified to have a tolerance of 1 %, what is the range of | V A | corresponding to input 1111 1111 ? M. B. Patil, IIT Bombay

DAC using binary-weighted resistors: Example (from Gopalan) I 7 V R A 7 R 7 = R I 1 A 1 R f R 1 = 2 6 R I 0 I A 0 R 0 = 2 7 R V A * If the resistors are specified to have a tolerance of 1 %, what is the range of | V A | corresponding to input 1111 1111 ? | V A | is maximum when (a) currents I 0 , I 1 , etc. assume their maximum values, with R k = R 0 k × (1 − 0 . 01) and (b) R f is maximum, R f = R 0 f × (1 + 0 . 01). (The superscript ‘0’ denotes nominal value.) M. B. Patil, IIT Bombay

DAC using binary-weighted resistors: Example (from Gopalan) I 7 V R A 7 R 7 = R I 1 A 1 R f R 1 = 2 6 R I 0 I A 0 R 0 = 2 7 R V A * If the resistors are specified to have a tolerance of 1 %, what is the range of | V A | corresponding to input 1111 1111 ? | V A | is maximum when (a) currents I 0 , I 1 , etc. assume their maximum values, with R k = R 0 k × (1 − 0 . 01) and (b) R f is maximum, R f = R 0 f × (1 + 0 . 01). (The superscript ‘0’ denotes nominal value.) max 11111111 = V R × 255 128 × R f � = 5 × 255 128 × 1 . 01 → | V A | max � 0 . 99 = 10 . 162 V . � R � M. B. Patil, IIT Bombay

DAC using binary-weighted resistors: Example (from Gopalan) I 7 V R A 7 R 7 = R I 1 A 1 R f R 1 = 2 6 R I 0 I A 0 R 0 = 2 7 R V A * If the resistors are specified to have a tolerance of 1 %, what is the range of | V A | corresponding to input 1111 1111 ? | V A | is maximum when (a) currents I 0 , I 1 , etc. assume their maximum values, with R k = R 0 k × (1 − 0 . 01) and (b) R f is maximum, R f = R 0 f × (1 + 0 . 01). (The superscript ‘0’ denotes nominal value.) max 11111111 = V R × 255 128 × R f � = 5 × 255 128 × 1 . 01 → | V A | max � 0 . 99 = 10 . 162 V . � R � 11111111 = 5 × 255 128 × 0 . 99 Similarly, | V A | min 1 . 01 = 9 . 764 V . M. B. Patil, IIT Bombay

DAC using binary-weighted resistors: Example (from Gopalan) I 7 V R A 7 R 7 = R I 1 A 1 R f R 1 = 2 6 R I 0 I A 0 R 0 = 2 7 R V A M. B. Patil, IIT Bombay

DAC using binary-weighted resistors: Example (from Gopalan) I 7 V R A 7 R 7 = R I 1 A 1 R f R 1 = 2 6 R I 0 I A 0 R 0 = 2 7 R V A * ∆ V A for input 1111 1111 = 10 . 162 − 9 . 764 ≈ 0 . 4 V which is larger than the resolution (0.039 V) of the DAC. This situation is not acceptable. M. B. Patil, IIT Bombay

DAC using binary-weighted resistors: Example (from Gopalan) I 7 V R A 7 R 7 = R I 1 A 1 R f R 1 = 2 6 R I 0 I A 0 R 0 = 2 7 R V A * ∆ V A for input 1111 1111 = 10 . 162 − 9 . 764 ≈ 0 . 4 V which is larger than the resolution (0.039 V) of the DAC. This situation is not acceptable. * The output voltage variation can be reduced by using resistors with a smaller tolerance. However, it is difficult to fabricate an IC with widely varying resistance values (from R to 2 N − 1 R ) and each with a small enough tolerance. M. B. Patil, IIT Bombay

DAC using binary-weighted resistors: Example (from Gopalan) I 7 V R A 7 R 7 = R I 1 A 1 R f R 1 = 2 6 R I 0 I A 0 R 0 = 2 7 R V A * ∆ V A for input 1111 1111 = 10 . 162 − 9 . 764 ≈ 0 . 4 V which is larger than the resolution (0.039 V) of the DAC. This situation is not acceptable. * The output voltage variation can be reduced by using resistors with a smaller tolerance. However, it is difficult to fabricate an IC with widely varying resistance values (from R to 2 N − 1 R ) and each with a small enough tolerance. → use R − 2 R ladder network instead. M. B. Patil, IIT Bombay

R-2R ladder network R R R 2R 2R 2R 2R 2R A 0 A 1 A 2 A 3 LSB MSB Node A k is connected to V R if input bit S k is 1; else, it is connected to ground.

R-2R ladder network R R R 2R 2R 2R 2R 2R A 0 A 1 A 2 A 3 LSB MSB Node A k is connected to V R if input bit S k is 1; else, it is connected to ground. The original network is equivalent to R R R 2R 2R 2R 2R 2R S 0 V R S 1 V R S 2 V R S 3 V R M. B. Patil, IIT Bombay

R-2R ladder network: Thevenin resistance R R R 2R 2R 2R 2R 2R

R-2R ladder network: Thevenin resistance R R R 2R 2R 2R 2R 2R

R-2R ladder network: Thevenin resistance R R R 2R 2R 2R 2R 2R R R R R 2R 2R 2R

R-2R ladder network: Thevenin resistance R R R 2R 2R 2R 2R 2R R R R R 2R 2R 2R

R-2R ladder network: Thevenin resistance R R R 2R 2R 2R 2R 2R R R R R 2R 2R 2R R R R 2R 2R

R-2R ladder network: Thevenin resistance R R R 2R 2R 2R 2R 2R R R R R 2R 2R 2R R R R 2R 2R

R-2R ladder network: Thevenin resistance R R R 2R 2R 2R 2R 2R R R R R 2R 2R 2R R R R 2R 2R R R 2R

R-2R ladder network: Thevenin resistance R R R 2R 2R 2R 2R 2R R R R R 2R 2R 2R R R R 2R 2R R R 2R

R-2R ladder network: Thevenin resistance R R R 2R 2R 2R 2R 2R R R R R 2R 2R 2R R R R 2R 2R R R 2R R Th = R M. B. Patil, IIT Bombay

R-2R ladder network: R R R V Th for S 0 = 1 2R 2R 2R 2R 2R V R

R-2R ladder network: R R R V Th for S 0 = 1 2R 2R 2R 2R 2R V R

R-2R ladder network: R R R V Th for S 0 = 1 2R 2R 2R 2R 2R V R R R R R 2R 2R 2R V R 2

R-2R ladder network: R R R V Th for S 0 = 1 2R 2R 2R 2R 2R V R R R R R 2R 2R 2R V R 2

R-2R ladder network: R R R V Th for S 0 = 1 2R 2R 2R 2R 2R V R R R R R 2R 2R 2R V R 2 R R R 2R 2R V R 4

R-2R ladder network: R R R V Th for S 0 = 1 2R 2R 2R 2R 2R V R R R R R 2R 2R 2R V R 2 R R R 2R 2R V R 4

R-2R ladder network: R R R V Th for S 0 = 1 2R 2R 2R 2R 2R V R R R R R 2R 2R 2R V R 2 R R R 2R 2R V R 4 R R 2R V R 8

R-2R ladder network: R R R V Th for S 0 = 1 2R 2R 2R 2R 2R V R R R R R 2R 2R 2R V R 2 R R R 2R 2R V R 4 R R 2R V R 8

R-2R ladder network: R R R V Th for S 0 = 1 2R 2R 2R 2R 2R V R R R R R 2R 2R 2R V R 2 R R R 2R 2R V R 4 R R 2R V Th = V R 16 V R 8 M. B. Patil, IIT Bombay

R-2R ladder network: R R R V Th for S 1 = 1 2R 2R 2R 2R 2R V R

R-2R ladder network: R R R V Th for S 1 = 1 2R 2R 2R 2R 2R V R

R-2R ladder network: R R R V Th for S 1 = 1 2R 2R 2R 2R 2R V R R R 2R 2R 2R 2R V R

R-2R ladder network: R R R V Th for S 1 = 1 2R 2R 2R 2R 2R V R R R 2R 2R 2R 2R V R

R-2R ladder network: R R R V Th for S 1 = 1 2R 2R 2R 2R 2R V R R R 2R 2R 2R 2R V R R R R 2R 2R V R 2

R-2R ladder network: R R R V Th for S 1 = 1 2R 2R 2R 2R 2R V R R R 2R 2R 2R 2R V R R R R 2R 2R V R 2

R-2R ladder network: R R R V Th for S 1 = 1 2R 2R 2R 2R 2R V R R R 2R 2R 2R 2R V R R R R 2R 2R V R 2 R R 2R V R 4

R-2R ladder network: R R R V Th for S 1 = 1 2R 2R 2R 2R 2R V R R R 2R 2R 2R 2R V R R R R 2R 2R V R 2 R R 2R V R 4

R-2R ladder network: R R R V Th for S 1 = 1 2R 2R 2R 2R 2R V R R R 2R 2R 2R 2R V R R R R 2R 2R V R 2 R R 2R V Th = V R 8 V R 4 M. B. Patil, IIT Bombay

R-2R ladder network: R R R V Th for S 2 = 1 2R 2R 2R 2R 2R V R

R-2R ladder network: R R R V Th for S 2 = 1 2R 2R 2R 2R 2R V R

R-2R ladder network: R R R V Th for S 2 = 1 2R 2R 2R 2R 2R V R R 2R 2R 2R V R

R-2R ladder network: R R R V Th for S 2 = 1 2R 2R 2R 2R 2R V R R 2R 2R 2R V R

R-2R ladder network: R R R V Th for S 2 = 1 2R 2R 2R 2R 2R V R R 2R 2R 2R V R R R 2R V R 2

R-2R ladder network: R R R V Th for S 2 = 1 2R 2R 2R 2R 2R V R R 2R 2R 2R V R R R 2R V R 2

R-2R ladder network: R R R V Th for S 2 = 1 2R 2R 2R 2R 2R V R R 2R 2R 2R V R R R 2R V Th = V R 4 V R 2 M. B. Patil, IIT Bombay

R-2R ladder network: R R R V Th for S 3 = 1 2R 2R 2R 2R 2R V R

R-2R ladder network: R R R V Th for S 3 = 1 2R 2R 2R 2R 2R V R

R-2R ladder network: R R R V Th for S 3 = 1 2R 2R 2R 2R 2R V R 2R 2R V R

R-2R ladder network: R R R V Th for S 3 = 1 2R 2R 2R 2R 2R V R 2R 2R V Th = V R 2 V R M. B. Patil, IIT Bombay

R-2R ladder network: R Th and V Th R R R 2R 2R 2R 2R 2R R Th V Th S 0 V R S 1 V R S 2 V R S 3 V R M. B. Patil, IIT Bombay

R-2R ladder network: R Th and V Th R R R 2R 2R 2R 2R 2R R Th V Th S 0 V R S 1 V R S 2 V R S 3 V R * R Th = R . M. B. Patil, IIT Bombay

R-2R ladder network: R Th and V Th R R R 2R 2R 2R 2R 2R R Th V Th S 0 V R S 1 V R S 2 V R S 3 V R * R Th = R . * V Th = V ( S 0) + V ( S 1) + V ( S 2) + V ( S 3) Th Th Th Th = V R S 0 2 0 + S 1 2 1 + S 2 2 2 + S 3 2 3 � � . 16 M. B. Patil, IIT Bombay

R-2R ladder network: R Th and V Th R R R 2R 2R 2R 2R 2R R Th V Th S 0 V R S 1 V R S 2 V R S 3 V R * R Th = R . * V Th = V ( S 0) + V ( S 1) + V ( S 2) + V ( S 3) Th Th Th Th = V R S 0 2 0 + S 1 2 1 + S 2 2 2 + S 3 2 3 � � . 16 * We can use the R -2 R ladder network and an op-amp to make up a DAC → next slide. M. B. Patil, IIT Bombay

DAC with R-2R ladder R f R f R Th R R R 2R 2R 2R 2R 2R V o V o V Th S 0 V R S 1 V R S 2 V R S 3 V R M. B. Patil, IIT Bombay

DAC with R-2R ladder R f R f R Th R R R 2R 2R 2R 2R 2R V o V o V Th S 0 V R S 1 V R S 2 V R S 3 V R * V o = − R f V Th = − R f V R � S 0 2 0 + S 1 2 1 + S 2 2 2 + S 3 2 3 � . 16 R Th R Th M. B. Patil, IIT Bombay

DAC with R-2R ladder R f R f R Th R R R 2R 2R 2R 2R 2R V o V o V Th S 0 V R S 1 V R S 2 V R S 3 V R * V o = − R f V Th = − R f V R � S 0 2 0 + S 1 2 1 + S 2 2 2 + S 3 2 3 � . 16 R Th R Th N − 1 * For an N-bit DAC, V o = − R f V Th = − R f V R S k 2 k . � R Th R Th 2 N 0 M. B. Patil, IIT Bombay

DAC with R-2R ladder R f R f R Th R R R 2R 2R 2R 2R 2R V o V o V Th S 0 V R S 1 V R S 2 V R S 3 V R * V o = − R f V Th = − R f V R � S 0 2 0 + S 1 2 1 + S 2 2 2 + S 3 2 3 � . 16 R Th R Th N − 1 * For an N-bit DAC, V o = − R f V Th = − R f V R S k 2 k . � R Th R Th 2 N 0 * 6- to 20-bit DACs based on the R-2R ladder network are commercially available in monolithic form (single chip). M. B. Patil, IIT Bombay

DAC with R-2R ladder R f R f R Th R R R 2R 2R 2R 2R 2R V o V o V Th S 0 V R S 1 V R S 2 V R S 3 V R * V o = − R f V Th = − R f V R � S 0 2 0 + S 1 2 1 + S 2 2 2 + S 3 2 3 � . 16 R Th R Th N − 1 * For an N-bit DAC, V o = − R f V Th = − R f V R S k 2 k . � R Th R Th 2 N 0 * 6- to 20-bit DACs based on the R-2R ladder network are commercially available in monolithic form (single chip). * Bipolar, CMOS, or BiCMOS technology is used for these DACs. M. B. Patil, IIT Bombay

DAC: home work R f r V o 8R 4R 2R 8R 4R 2R R R S 0 V R S 1 V R S 2 V R S 3 V R S 4 V R S 5 V R S 6 V R S 7 V R Combination of weighted−resistor and R−2R ladder networks M. B. Patil, IIT Bombay

DAC: home work R f r V o 8R 4R 2R 8R 4R 2R R R S 0 V R S 1 V R S 2 V R S 3 V R S 4 V R S 5 V R S 6 V R S 7 V R Combination of weighted−resistor and R−2R ladder networks * Find the value of r for the circuit to work as a regular (i.e., binary to analog) DAC. M. B. Patil, IIT Bombay

DAC: home work R f r V o 8R 4R 2R 8R 4R 2R R R S 0 V R S 1 V R S 2 V R S 3 V R S 4 V R S 5 V R S 6 V R S 7 V R Combination of weighted−resistor and R−2R ladder networks * Find the value of r for the circuit to work as a regular (i.e., binary to analog) DAC. * Find the value of r for the circuit to work as a BCD to analog DAC. M. B. Patil, IIT Bombay

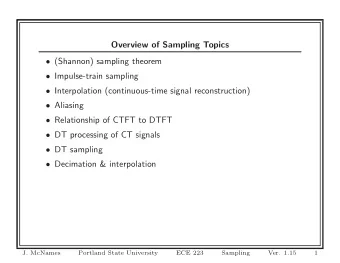

DAC: settling time V R V A D N − 1 final value N-bit analog digital V A initial output input value D 2 D 1 D 0 t ground M. B. Patil, IIT Bombay

DAC: settling time V R V A D N − 1 final value N-bit analog digital V A initial output input value D 2 D 1 D 0 t ground * When there is a change in the input binary number, the output V A takes a finite time to settle to the new value. M. B. Patil, IIT Bombay

DAC: settling time V R V A D N − 1 final value N-bit analog digital V A initial output input value D 2 D 1 D 0 t ground * When there is a change in the input binary number, the output V A takes a finite time to settle to the new value. * The finite settling time arises because of stray capacitances and switching delays of the semiconductor devices used within the DAC chip. M. B. Patil, IIT Bombay

DAC: settling time V R V A D N − 1 final value N-bit analog digital V A initial output input value D 2 D 1 D 0 t ground * When there is a change in the input binary number, the output V A takes a finite time to settle to the new value. * The finite settling time arises because of stray capacitances and switching delays of the semiconductor devices used within the DAC chip. * Example: 500 ns to 0.2 % of full scale. M. B. Patil, IIT Bombay

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.