Ferroelectric Memory and Negative Capacitance T.P. Ma Yale - PowerPoint PPT Presentation

Ferroelectric Memory and Negative Capacitance T.P. Ma Yale University Ferroelectrics: The Basics Example: PZT A class of ionic crystals that exhibit spontaneous polarization, switchable by external electric fields Must be below the

Ferroelectric Memory and Negative Capacitance T.P. Ma Yale University

Ferroelectrics: The Basics Example: PZT • A class of ionic crystals that exhibit spontaneous polarization, switchable by external electric fields • Must be below the ‘ Curie ’ temperature

Ferroelectric Polarization P-E hysteresis V P P s Electrode P r + + + + - - - - -P 0’ d f , f ,P(E) E 0 +P + + + + E c - - - - Electrode

The 1T-1C Memory Cell based on Metal/Ferro/Metal (MFM) capacitor (the current commercial products) Word Line Bit Line MFM capacitor Similar to DRAM Cell Str ucture

The Single-Transistor (FeFET) Memory Cell Similar to Flash Cell Str ucture

Operating Principle of FeFET I D I D ~0 + + + + + - - - - - V D V D - - - - - + + + + + + + + + + - - - - - n + n + n + n + P P Programming: - - (FE) on "1" (FE) off "0" + + Read out: (@ Vg=0) I D 0 "0" Large I D "1"

Id-Vg Hysteresis of FeFET 10 Pt/SBT/Y 2 O 3 /Si 1 W/L(um)=40/2 0.1 I d (uA) Memory Window 0.01 1E-3 5 1E-4 1E-5 -2 -1 0 1 2 3 4 V g (V)

The Obstacles that have so far Prevented the Commercialization of FeFET - Problems with Previously Available Ferroelectrics (PZT and SBT) - There are Tremendous Difficulties in • CMOS Compatibility • Thermal Budget; Process Integration • Scaling Below 0.1 µm Node

Representative Memory Window Retention Characteristics 3.0 t PZT FeFET log( ) 4 2.7 10 2.5 Leakage t log( ) V g (V) 2.0 2.39 Depolarization 1.5 t log( ) 1.15 t 1.0 log( ) 4 1.2 10 1 10 100 Time(s)

What Limits the Retention Time? • Depolarization Field • Gate Leakage/Trapping T.P. Ma and Jin-Ping Han, IEEE Electron Device Letters, 23(7), p.386 (2002).

Depolarization Field Comes from Incomplete Charge Compensation For Ideal M-F-M Structure with Complete Charge Compensation, There is NO Depolarization Field Electrode Compensating + + + + – - - - - Charge P P Compensating + + + + + - - - - Charge Electrode

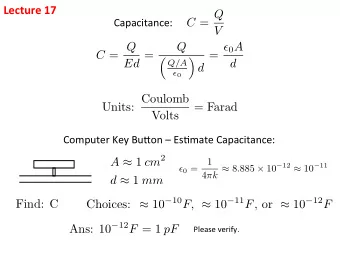

Depolarization Field Comes from Finite MIS Capacitance For FEDRAM, the finite insulator/semiconductor capacitance, C IS , causes incomplete charge compensation. Gate voltage V induces polarization P, and voltage across ferroelectric V F = C IS V/(C IS + C F ) – P/(C IS + C F ). When V goes to 0, V F + V IS = (Q F – P)/C F + Q IS /C IS = 0, which reduces to Q F = PC IS /(C IS + C F ), leading to a depolarization field E dp = PC F / (C IS + C F ).

Gate Leakage/Trapping Causes Memory Loss - J i (E i ) J f (E f , t) - J i (E i ) - J f (E f , t) + - - + - + + - - + “OFF” + + “ON” + M F I p-Si M F I p-Si Electron (or Hole) Injection Followed by Trapping Leads to Local Charge Compensation and Gradually Diminished Effect of Polarization.

FeFET Memory Retention Loss Mechanisms 3.0 t PZT FeFET log( ) 4 2.7 10 2.5 Leakage t log( ) V g (V) 2.0 2.39 Depolarization 1.5 t log( ) 1.15 t 1.0 log( ) 4 1.2 10 1 10 100 Time(s)

The Game Changer: HfO 2 -Based Ferroelectrics • CMOS Compatible Materials and Processes • Desirable Combination of Dielectric Constant, Remnant Polarization, and Coercive Field • Scalability: Same as CMOS Gate Dielectric J. Müller et al., IEEE IEDM Technical Digest pp.10.8.4-10.8.5. (2013)

Retention Time For HfO2-Based FeFET • Depolarization Field E dp (HfO 2 ) < E c (HfO 2 ) [~1MV/cm]: Nearly No Rentention Loss Due to Depolarization Field • Gate Leakage/Trapping Trap Density in HfO 2 is 2 Orders of Magnitude Lower Than those in PZT and SBT

Calculation of E d ep Parameters affecting E dep E dep = PC F /[ F (C IS + C F )] • Polarization, F and C F • Series comb. C IS • IL cap. C IL C IS =C IL C S /(C IL +C S ) • Semi cap. C S C IL C S_min /(C IL +C S_min )<C IS <C IL N. Gong, and T.P. Ma, SISC 2016

Comparison of E dep /E c for HfO 2 , PZT, SBT (Fixed MW) PZT SBT FE-HfO 2 E c 31 kV/cm 90 kV/cm 1 MV/cm • E dep /E c (HfO 2 ) is smallest HfO 2 MW d F E c • Least retention loss largest E c Fixed, the HfO 2 thinnest Less I d same MW Scaling adv. Retention Loss Fixed What about MW HfO 2 is most scalable retention of & has longest retention scaled PZT/SBT? Time Why E dep /E c (HfO 2 ) is smallest? [1] W. Shih, et al., J. Appl. Phys. vol. 103, 2008. [2] S. Lee, et al., J. Appl. Phys. vol. 91, , 2002. [3] J. Müller, et al., ECS J. Solid State Sci. and Tech., vol. 4, 2015. [4] J. Müller, et al., ECS Trans., vol. 69 , 2015.

Why E dep /E c is Small for HfO 2 (E dep /E c ) min ~ 2P/[MW*(C IL +C F )] • Largest E c smallest d F (E dep /E c ) max / (E dep /E c ) min smallest E dep /E c largest C F ~ C IL /(C F +C IS_min ) [1] W. Shih, et al., J. Appl. Phys. vol. 103, 2008. [2] S. Lee, et al., J. Appl. Phys. vol. 91, 2002. [3] J. Müller, et al., ECS J. Solid State Sci. and Tech., vol. 42015. [4] J. Müller, et al., ECS Trans., vol. 69, 2015.

Scaling Consideration for FEDRAM PZT & SBT Require Too Thick FE Layer – Not Suitable for Production

Scaling Consideration for FEDRAM HfO 2 -Based FeFET < 10nm in Thickness J. Müller et al., IEEE IEDM Technical Digest pp.10.8.4-10.8.5. (2013)

Demonstration of 28nm FeFET Cell Fabricated at Our Foundry Partner

Excellent Memory Characteristics Sizable Memory Windows Have Been Measured

10-Year Retention of FeFET Cell

Endurance of HfO2-Based FeFET

Trade-off Between Retention and Endurance High Endurance but Short Retention – DRAM Like

Excellent Manufacturability Integrating FE-Gate with CMOS HKMG Any advanced CMOS foundry can manufacture without new equipment.

Proposed 3-D FeFET Memory Arrays US Patent Issued

Summary of FeFET Memory • FeFET memory has numerous advantages over conventional Flash • Either Flash-like or DRAM-like memory can be realized by tuning the programming strength • Test memory cells have been demonstrated with foundry partner’s 28nm technology • It’s most suitable for eFlash applications • It has great potential for low-cost, high-density storage technology

Negative Capacitance: Science Fact or Science Fiction?

A Close Examination of Salahuddin/Data's Original Paper in Nano Letters

Negative Capacitance (NC) Was Proposed Salahuddin claimed that the ferroelectric capacitor can be negative! S. Salahuddin, S. Datta, Nano Letter (2008) 11/15/2018 33

Ginzburg-Landau theory Phase transition from paraelectricity to ferroelectricity 11/15/2018 34

NC Theory Negative Capacitance! But unstable! S. Salahuddin, S. Datta, Nano Letter (2008 ) 11/15/2018 35

Quasi-Static NC (QSNC) theory “Quasi - static negative capacitance” (QSNC) theory 11/15/2018 36

Amazing Predictions of the QSNC Theory J. Van Houdt, et.al EDL (2018) 11/15/2018 37

What’s Wrong with the QSNC Theory? 11/15/2018 38

Mistake 1 In equilibrium, only local minimum states exist! We need 11/15/2018 39

Mistake 1 (Continued) “Negative Capacitance” region cannot exist in equilibrium 11/15/2018 40

Mistake 2 Therefore, the P-E (or P- V) “S Curve” cannot be translated directly to the Q-V curve 11/15/2018 41

Mistake 2 (Continued) It’s well known that P ≠ Q in a FeFET Why is it P ≠ Q in a MOSFET or any other circuit like the following? Answer: Due to Incomplete Charge compensation P ≠ Q Q Whenever there is a capacitor In series with the ferroelectric capacitor, P P ≠ Q , which causes a depolarization field V g that hurts the retention time Ψ s This is well known in the ferroelectric Q memory community*. *IEEE Electron Device Letters, vol.23(7), 386 (2002)

Mistake 2 (Continued) Actual Case NC theory 11/15/2018 43

Mistake 3 Ignoring the strong Coupling of FE/DE Layers J. Kittl, et.al APL (2018) 11/15/2018 44

Mistake 3 (Continues) 11/15/2018 45

Experimental Verification Experimental MFM Capacitor 11/15/2018 46

C-V Measurements The FE + DE Series Capacitance Always Shows Lower Total Capacitance 11/15/2018 47

V APP -V DE Measurements Sweep rate: Sweep rate: 56V/ms 56V/ms Sweep rate: Sweep rate: 80V/ms 80V/ms 11/15/2018 48

V APP -V DE Measurements (Continued) Sweep rate f = 1kHz 20V: 80V/ms 16V: 64V/ms 12V: 48V/ms 8V: 32V/ms f = 1kHz f = 1kHz Sweep rate 14V: 56V/ms 8V: 32V/ms 11/15/2018 49

Summary of Negative Capacitance • Salahuddin’s Quasi-Static Negative Capacitance (QSNC) theory has been closely examined • Several major mistakes have been identified • Experimental results did not support the 3 major predictions of the QSNC theory

Quasi-static Negative Capacitance: Fact or Fiction?

Thank You!

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.