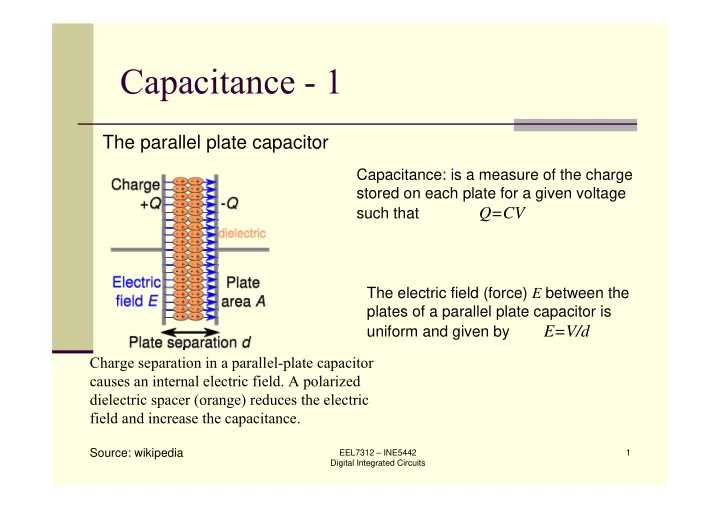

Capacitance - 1 The parallel plate capacitor Capacitance: is a - PowerPoint PPT Presentation

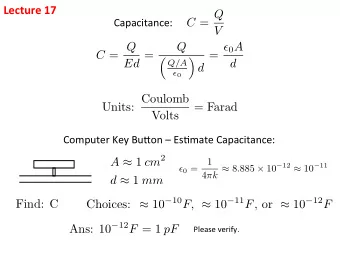

Capacitance - 1 The parallel plate capacitor Capacitance: is a measure of the charge stored on each plate for a given voltage such that Q=CV The electric field (force) E between the plates of a parallel plate capacitor is uniform and given by

Capacitance - 1 The parallel plate capacitor Capacitance: is a measure of the charge stored on each plate for a given voltage such that Q=CV The electric field (force) E between the plates of a parallel plate capacitor is uniform and given by E=V/d Charge separation in a parallel-plate capacitor causes an internal electric field. A polarized dielectric spacer (orange) reduces the electric field and increase the capacitance. Source: wikipedia EEL7312 – INE5442 1 Digital Integrated Circuits

Capacitance - 2 Current flow L Electrical-field lines W H t di Dielectric Substrate ε ε = 2 = fF/ μ m ox C di c WL ox t int t ox Defined by foundry di Source: Rabaey EEL7312 – INE5442 2 Digital Integrated Circuits

Capacitance - 3 Source: Rabaey EEL7312 – INE5442 3 Digital Integrated Circuits

Capacitance - 4 Fabrication Gate oxide Capacitance process thickness / area (fF/ μ m 2 ) (CMOS) (nm) AMIS 1.5 32 1.1 μ m IBM 0.25 6.3 5.5 μ m IBM 0.13 3.2 11 μ m Source: MOSIS Source: Intel Tech. Journal EEL7312 – INE5442 4 Digital Integrated Circuits

Capacitance - 5 = = = ; / ( )/ Q CV I dQ dt d CV dt = / I CdV dt for constant capacitance For constant V → I =0, i.e. a capacitor behaves as an open circuit at I + dc. V Capacitors are energy-storage (memory) devices used in filters, - oscillators, power sources. Ideal capacitors are not dissipative (and not noisy) but charging and discharging them causes heating through dissipative devices connected to the capacitors. EEL7312 – INE5442 5 Digital Integrated Circuits

The RC circuit - 1 + V R - = = / / KCL I CdV dt V R = + / C R I + V RCdV dt V R = + V V V S C C V S + KVL V C - S C R C - Assume that V S = 0 for t <0, V S = A for t ≥ 0 (and V C (0)=0). ( ) = ⎡ − − τ ⎤ ≥ 1 exp / 0; V A ⎣ t ⎦ t t d C = < 0 0 50% V t C ( ) = = − τ ≥ / exp / / 0 I CdV dt A t R t C t d = τ ln2 ≅ 0.69 τ τ = RC EEL7312 – INE5442 6 Digital Integrated Circuits

The RC circuit - 2 ( ) ( ) + V R - = − − t τ = − τ ≥ ⎡ ⎤ exp / / 0 1 exp / V A I A t R t ⎣ ⎦ C I + The power dissipation p (electric power converted into R V S + V C heat) in the resistor is - C 2 exp ( ) - = 2 = − τ 2 / / p RI A t R The energy converted into heat in the resistor is Assume that V S = 0 for t <0, ∞ ∞ 2 2 ⎛ 2 ⎞ A t CA ∫ ∫ V S =A for t ≥ 0 (and V C (0)=0). = = − = exp ⎜ ⎟ E pdt dt τ R ⎝ ⎠ 2 R 0 0 The energy stored in the capacitor (for t →∞ ) 2 2 CV CA E = = C C 2 2 Exercise: (a) Using the energy conservation principle calculate the energy delivered by the source. (b) Calculate the energy E S delivered by the source using the formula below ∞ = ∫ E V Idt S S 0 EEL7312 – INE5442 7 Digital Integrated Circuits

Simulation 4.2 RC1 + V R - 1 2 * this is RC1.cir file I + v0 1 0 dc 0 pulse 0 1V 0 10ps 10ps 10ns 20ns R V S + R 1 2 1k V C - C C 2 0 1p - 0 .end EEL7312 – INE5442 8 Digital Integrated Circuits

Exercise 4.2 Run SpiceOpus to determine the voltages at the intermediate nodes 2 and 3 for the stimulus of simulation 4.2 2 1 3 R= 1 k Ω I R/ 2 R/ 2 V S + - C= 1 pF C/ 2 C/ 2 0 SpiceOpus (c) 1 -> source RC2.cir SpiceOpus (c) 2 -> tran 0.1ns 20ns SpiceOpus (c) 3 -> setplot new New plot V (3) Current tran1RC2 (Transient Analysis) V (2) const Constant values (constants) SpiceOpus (c) 4 -> plot v(1) v(2) v(3) xlabel time[s] ylabel Outputs[V] EEL7312 – INE5442 9 Digital Integrated Circuits

Comparison between exercises 4.1 and 4.2 2 1 3 4 1 I R= 1 k Ω I R/ 2 R/ 2 R V S + V S + - - C C/ 2 C= 1 pF C/ 2 0 0 V(3) V(4) EEL7312 – INE5442 10 Digital Integrated Circuits

Capacitance - 6 Fringing Capacitance w= W-H/2 W H t di thick oxide capacitance/unit length substrate (a) H W - H/2 + (b) Source: Rabaey EEL7312 – INE5442 11 Digital Integrated Circuits

Capacitance - 7 Interwire Capacitance Crosstalk: a signal can affect another nearby signal. fringing parallel Substrate noise coupling Source: Rabaey EEL7312 – INE5442 12 Digital Integrated Circuits

Capacitance - 8 Wiring Capacitances (0.25 μ m CMOS) aF/ μ m 2 aF/ μ m Source: Rabaey EEL7312 – INE5442 13 Digital Integrated Circuits

Exercise 4.3 Estimate the capacitance of the wires specified below: 1. Polysilicon, W= 0.25 μ m, L=1 mm; 2. Polysilicon, W= 0.25 μ m, L=10 mm; 3. Metal 1, W= 0.25 μ m, L=1 mm; 4. Metal 1, W= 0.25 μ m, L=10 mm. In each case, calculate the delay time assuming a lumped RC model for the wire and the capacitance with the substrate. Assume that the sheet resistances for polysilicon (with silicide) and metal 1 are 5 Ω and 0.1 Ω , respectively. ⎛ ⎞ ⎛ ⎞ C C = = ; fringe PP ⎜ ⎟ ⎜ ⎟ C WL C L PP fringe ⎝ ⎠ ⎝ ⎠ area length C C L = = 2 88 aF/ μ m fringe 54 aF/ μ m PP W area length L = + = H R R W C C C wire PP fringe wire thick oxide ≅ 0.69 substrate t R C d wire wire Source: Rabaey EEL7312 – INE5442 14 Digital Integrated Circuits

Exercise 4.3 - Answer 1. C wire =76 fF, R wire = 20 k Ω , R wire C wire = 1520 ps, t d = 0.69R wire C wire =1050 ps 2. C wire =760 fF, R wire = 200 k Ω , R wire C wire = 152 ns, t d = 0.69R wire C wire =105 ns 3. C wire =47.5 fF, R wire = 400 Ω , R wire C wire = 19 ps, t d = 0.69R wire C wire =13 ps 4. C wire =475 fF, R wire = 4 k Ω , R wire C wire = 1.9 ns, t d = 0.69R wire C wire =1.3 ns Note that the delay time increases proportionally with the square of the wire length. Why? So far we have considered that the distributed RC line can be represented by a lumped RC model (pessimistic view) and that the drive signal is a step supplied by an ideal voltage source (optimistic view). EEL7312 – INE5442 15 Digital Integrated Circuits

RC delay - 1 Influence of the output resistance of the driver V out Example: R driver =100 k Ω , c wire and 1- μ m-wide, 10-mm- Driver long Al1 wire. What’s t pd ? C C = = 2 30 aF/ μ m fringe 40 aF/ μ m PP area length R wire << R driver ⎛ ⎞ ⎛ ⎞ C C = = = = 0.3 pF; fringe 0.4 pF ⎜ PP ⎟ ⎜ ⎟ C WL C L R PP ⎝ ⎠ fringe ⎝ ⎠ area length driver V out = + = 0.7 pF C C C wire PP fringe ≅ t ≅ 0.69 50 ns t R C V in d driver wire d C lumped What’s the approximate maximum operating frequency of the input such that the output can detect the correct value of the input? Source: Rabaey EEL7312 – INE5442 16 Digital Integrated Circuits

RC delay – 2: The Elmore delay -1 Elmore delay model *– method to determine the approximate delay time in an RC network; it avoids running costly simulations for calculation of delay time. Useful for determining delays in transmission lines, gates, clock distribution networks,… Sources: Rabaey & *W. C. Elmore, “The transient response EEL7312 – INE5442 17 of damped linear networks with particular regard to wideband Digital Integrated Circuits amplifiers,” J. Applied Physics, vol. 19, Jan 1948

RC delay – 3: The Elmore delay -2 τ = + + + + = R C R C R C R C R C 1 1 2 2 3 3 4 4 Di i i i i ii i ( ) path s → i + + + R ii =R 1 +R 3 +R i R R R C 1 3 i i + path s → 1 R i1 =R 1 R C 1 1 + path s → 2 R i2 =R 1 R C 1 2 ( ) + + path s → 3 R i3 =R 1 +R 3 R R C 1 3 3 ( ) + + path s → 4 R i4 =R 1 +R 3 R R C 1 3 4 Sources: Rabaey & *W. C. Elmore, “The transient response EEL7312 – INE5442 18 of damped linear networks with particular regard to wideband Digital Integrated Circuits amplifiers,” J. Applied Physics, vol. 19, Jan 1948

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.