Learning Outcomes I understand the sources of capacitance in CMOS - PowerPoint PPT Presentation

2-7.1 2-7.2 Learning Outcomes I understand the sources of capacitance in CMOS circuits I understand how delay scales with resistance, capacitance and voltage Spiral 2-7 I can determine appropriate width of PMOS and NMOS transistors

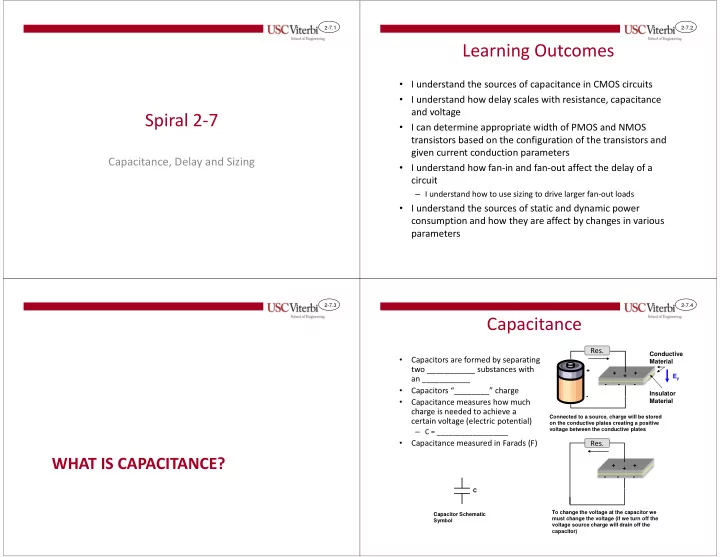

2-7.1 2-7.2 Learning Outcomes • I understand the sources of capacitance in CMOS circuits • I understand how delay scales with resistance, capacitance and voltage Spiral 2-7 • I can determine appropriate width of PMOS and NMOS transistors based on the configuration of the transistors and given current conduction parameters Capacitance, Delay and Sizing • I understand how fan-in and fan-out affect the delay of a circuit – I understand how to use sizing to drive larger fan-out loads • I understand the sources of static and dynamic power consumption and how they are affect by changes in various parameters 2-7.3 2-7.4 Capacitance Res. Conductive • Capacitors are formed by separating Material two ___________ substances with + + + + E y an ___________ - - - • Capacitors “________” charge Insulator - Capacitance measures how much • Material charge is needed to achieve a Connected to a source, charge will be stored certain voltage (electric potential) on the conductive plates creating a positive voltage between the conductive plates – C = __________________ • Capacitance measured in Farads (F) Res. WHAT IS CAPACITANCE? + + + - - - C To change the voltage at the capacitor we Capacitor Schematic must change the voltage (if we turn off the Symbol voltage source charge will drain off the capacitor)

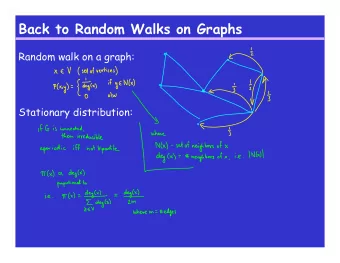

2-7.5 2-7.6 Charging/Discharging Capacitors Capacitor I-V Relationship � • Charging a capacitor gets more “__________” as more charge is added • Fact � � � , or � � �� • Eventually, no more charge can be added and the capacitor acts like an open circuit • Also recall � � � � � �� + + + �� + + + - - - Voltage of �� • Thus, substituting � � �� � __________ Capacitor + + + + + + • Current is linearly related (slope = C) to the - - - - - - As more charge (voltage) ___________ in voltage (not the absolute builds up that charge repels like charge and makes it voltage) “harder” to add more (like pushing a spring) – No voltage _________ (constant voltage) means no ____________________ Time 2-7.7 2-7.8 Measures of Capacitance • C = �� + + + - - - � – � is the permittivity of the insulator substance (intrinsic material property) • � defined as 1 for a vacuum • Silicon dioxide (separates gate from silicon) = 3.9 First-order RC circuit step response • Pure silicon = 11.68 RC CIRCUIT ANALYSIS – � is the _________ of the conductive materials – � is the ___________________ (or thickness of the capacitor)

2-7.9 2-7.10 Resistance / Capacitance Analogy Voltage, Resistance & Capacitance + + • Let's analyze a simple circuit + Resistance = – Known as an RC circuit (resistor & capacitor Limit of water flow Charge = in series) Water – Assume t < 0, _________________ – For t > 0, Vs = ___ (voltage source turns on) – Current through R must be same as current "through" C • � � � � � � � �� �� ⇒ � � ____________ � – Now let's solve for dVc/dt �� �� � ______________ � • Voltage Source = Water Pressure Capacitance = – We can solve this differential equation Total Water Needed �� � � � • � � � � � �� � � � 0 � � �� Switching Time = Time to fill or drain the capacitor (“bucket”) of charge Thus, increase the voltage or decrease the resistance/capacitance. • For Vc(0)=0 we have � � � � _______________ 2-7.11 2-7.12 Voltage, Resistance & Capacitance Time Constant • Let's analyze a simple circuit • Notice the charging (discharging) time is determined by product of R*C – Known as an RC circuit (resistor & capacitor in series) • We refer to this as the ___________, τ – Assume t < 0, Vs = Vdd then Vc=Vdd – τ = RC – For t > 0, Vs = 0 (voltage source = GND) • As the product of RC increases we get – Current through R must be same as current ___________ switching times "through" C • We can show that the time it takes to � � �� � �� �� �� � � � � � �� �� ⇒ � � � � • � �� charge/discharge a capacitor to a – Now let's solve for dVc/dt fraction of Vdd is given in the table �� �� � � � �� ⇒ �� �� � � � � � � �� � 0 • below – We can solve this differential equation Voltage Range Time � 0 � � � • � � � � � 0 to 50% (t p = prop. delay) _____*RC �� 0 to 63% (τ) RC 10% to 90% (t r =rise time/delay) ____*RC • For Vc(0)=Vdd we have � � � � __________

2-7.13 2-7.14 MOSFET Parasitic Capacitance • In order to examine the delay of a MOSFET, we have to determine nature and amount of ______________ capacitance associated with MOS transistor Parasitic: Unintentional, ______________________ capacitors – – It's not that we want caps, we're ________________ due to the structure of the MOSFET. • The oxide layer separating gate and substrate is a more obvious capacitor • However the _______________ around the source and drain DELAY also form capacitors Gate Source Drain 14 2-7.15 2-7.16 Transistor R and C values Resistor and Capacitor Delay • Observation: Output of one transistor usually drives input of another • Outputs connect to other inputs Wire from an output – Sources of resistance • To change the output voltage (really of another gate the input of the next gate), we must • ____________________________________ conduct enough charge to raise or • _____________ connecting __________________ + + lower its present voltage – Sources of capacitance Wire + • ________________ of the next transistor • Resistance limits the amount of • Other small capacitances charge that can be transferred per Desired Transition: 0V -> Vdd unit time Charge must be conducted through this path and build up at the • Capacitance determines how much gate input to raise the voltage to the necessary value charge must be present to attain a 3V certain voltage Source • Time it takes to attain a certain Metal Wire voltage is proportional to R*C Gate Gate Switching Time ~ Source Drain Source Drain Resistance*Capacitance

2-7.17 2-7.18 Where RC Circuits Occur Where RC Circuits Occur • Consider a CMOS gate driving others (__________) • Depending on the inverter input the PMOS or NMOS will be in ________________ mode and can be modeled as resistors – The output connects to the gate inputs of the loads (fan- – Thus we have an RC circuit either charging or discharging the output (C L ) out) and thus can be modeled as a capacitive load (C L ) 2-7.19 2-7.20 Defining Delays • We model – The next gate(s) and other parasitic capacitances as a lumped capacitance – The PDN or PUN transistors as resistors (since they are operating in linear mode when the input is near VDD or GND) • t PLH and t PHL refer to the ___________ delay of a circuit when the output changes from low to high (______) [t PLH ] or high to low (________) [t PHL ] � ( � )) – � !" # 0.69' � ! � - * + � )) �� ,+ CMOS SIZING Vin � ( � )) – � "! # 0.69' . � ! � * / � )) �� ,/ - Vout • We say the delay of the gate is then: – t PD ≈ (t PLH + t PHL ) / 2 Vin • Important: What reduces delay? Vout – ___________________________

2-7.21 2-7.22 Sizing – Inverter Sizing – PMOS is Slower than NMOS! K • Assume n K ≈ p 2 • Recall the equations for current through a transistor in linear mode • Find the ratio and W p and W n that balances the delay of output – |1 �2 | � 3 7 �2 | 4 4 5′ 2 9 :2 � | � ; | |� �2 | � |� ! during falling and rising transitions – Ohm's law says I = V/R so in the equation above 3 � ∝ 5′ 7 ! R 1 KW K W 2 W • Problem _________ (K N ≈ _____K P ) ⇒ ⇒ p n n n W 2 W ∝ ∝ = = p n R L R K W W – PMOS are ______ at conducting than NMOS VDD n p p p – This will leave to imbalances in ______ (i.e. ______________) – To balance the delay when pulling up vs. pulling down OUT we can play with _______ IN • Solution: Make _________ by about a factor of 2 or 2.5 CL 2-7.23 2-7.24 Sizing – Simple CMOS Gates Sizing – Complex CMOS Gates PUN: make • Goal: Make any gate have the same worst case resistance as each path an inverter W/L = 2) B • The ratio of the {W/L} PUN / {W/L} PDN should be about two (or A higher) to make up for slow PMOS C Important Notes: For parallel transistors D consider only the case if 1 is on (Remember if NOR R||R then Reff=R/2 which is a better case so A we assume only one is D on) Series transistors in NAND B C PDN: series add lengths/ make each path resistance W/L = 1 All paths in a PxN should 24 have same resistance

2-7.25 2-7.26 Compound Gate Example Compound Gate Example Y = D • (A + B + C) Y = AB+CD PUN: make PUN: make each path each path A W/L = 2) W/L = 2) B C D Y PDN: PDN: D make each path make each path W/L = 1 W/L = 1 A B C 2-7.27 2-7.28 Fanout • Fanout refers the number of gates an output connects to • As the fanout increases C L This inverter has a fanout (# of ________________ and loads) = 1 means the delay _________ FANIN & FANOUT This inverter has a fanout (# of loads) = 3

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.