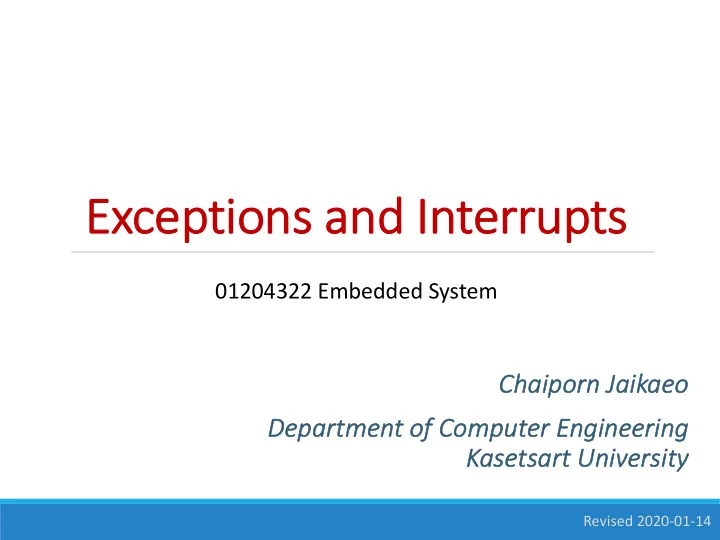

Ex Excepti tion ons s and Interru rrupts ts 01204322 Embedded - PowerPoint PPT Presentation

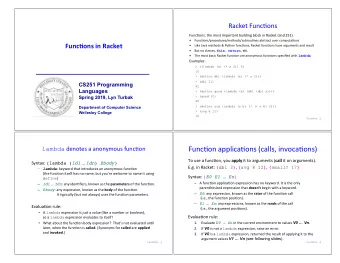

Ex Excepti tion ons s and Interru rrupts ts 01204322 Embedded System Chaipo Chaiporn J n Jaik aikae aeo De Department of f Computer Engineering Kasetsart Unive versity Revised 2020-01-14 Ou Outline Polling vs. interrupt

Ex Excepti tion ons s and Interru rrupts ts 01204322 Embedded System Chaipo Chaiporn J n Jaik aikae aeo De Department of f Computer Engineering Kasetsart Unive versity Revised 2020-01-14

Ou Outline • Polling vs. interrupt programming styles • General interrupt mechanism in microcontrollers • ARM Cortex-M4’s interrupt system • Hands-on activity ◦ Standard output redirection to UART ◦ Switch input probing using timer interrupt 2

Co Common Programming Pattern rns • Software polling • Interrupt (event-driven) • DMA (direct memory access) ◦ Good for moving large amount of data, e.g., audio • RTOS (Real-Time Operating System) ◦ Simplifies a complex application into smaller, concurrent tasks • Combination of methods above 3

Po Polling vs. Interrupt • Polling ◦ Program keeps checking for a certain event to happen ◦ E.g., GPIO pin status changed, or timer • Interrupt http://clipart-library.com/clipart/1162315.htm ◦ Program keeps doing regular routines ◦ When an event of interest happens, the program suspends normal execution and executes code that handles the event https://lastminuteengineers.com/handling -esp32-gpio-interrupts-tutorial/ 4

Po Polling vs. Interrupt (cont’d) • Considering pseudo-code for switch-toggled LED forever: wait until switch is pressed toggle LED wait until switch is released when switch pressed is detected: toggle LED forever: do nothing (or sleep) 5

In Inter errup upts v s vs. s. Ex Excep eptions ns • An exception is an event that alters normal program flow • Interrupts are exceptions caused by hardware events, such as peripherals and I/O • Other exceptions are: ◦ Faults – caused by faulting instructions, such as division by zero ◦ Traps – deliberately caused by user program to trigger certain event or service ◦ Aborts – used only to signal severe problems; operation no longer possible 6

In Inter errup upt S Ser ervice R e Rout utine (IS ne (ISR) • A special block of code that gets executed automatically by the CPU when a corresponding interrupt occurs • Also known as Interrupt Handler ◦ or Exception Handler in general saves program state restores program state interrupt ISR normal program flow à normal program flow à 7

Ma Maskable v vs. N Non-mask maskab able le Interrupts ts • Maskable interrupts can be disabled by the program ◦ To perform critical operations that must not be interrupted ◦ Most interrupts are maskable • Non-maskable interrupts cannot be disabled ◦ Used to indicate critical events, e.g., reset, power failure http://clipart-library.com/clipart/618555.htm 8

Lo Locatio ions o of I f ISR SRs • Should be at fixed locations so CPU can find them easily • Problem: different ISRs have different lengths • Possible solutions ◦ A table of ISR locations is maintained at a fixed memory location ◦ This table is called Interrupt Vector Table ◦ ISRs may be changed dynamically by the application ◦ AVR’s vector table is filled with JMP instructions, while Cortex-M’s vector table stores ISR addresses 9

In Inter errup upt P Priorities es • Many MCUs support different interrupt priorities • An interrupt with a higher priority can preempt the execution of a lower-priority interrupt • Priorities may be fixed or programmable • Program can also choose to disable interrupts whose priorities are below a threshold ST’s training slides on Moving from Priority: IRQ2 > IRQ1 8 to 32 bits hands-on workshop (IRQ = I nterrupt R e Q uest) 10

In Inter errup upt L Latenc ency • Interrupt latency à a mount of time to respond to an interrupt • Depends on: 1. How long the interrupt is disabled 2. Time to execute ISRs of higher priority interrupts 3. Time for processor to stop current execution, do necessary save state, and start executing the ISR 4. Time taken for the ISR to save context and start executing instructions that count as a ‘response’ • Factor 3 depends on HW, not under software control • Other factors are controlled by writing efficient code that are not too long ◦ Make ISRs short Taken from lecture slides by Prof. Chung-Ta King 11

Wr Writing an ISR • ISR should finish as quickly as possible • ISR does not accept parameters, nor returns a value ◦ To communicate with the main program, use global variables or shared data structures ◦ These variables must be declared volatile • For events that need complicated handling, set a flag to notify the main code • Accessing variables shared with ISR must be atomic ◦ Especially read-modify-write memory update sequence ◦ An interrupt can happen in the middle of variable access ◦ Wrap these statements inside a critical section (disable interrupt, etc.) 12

ST STM32L4’s Interrupt System • Controlled by Nested Vectored Interrupt Controller (NVIC) • 67 maskable interrupt channels • 16 programmable priority levels ◦ 4 bits of interrupt priority are used • Low-latency exception and interrupt handling • Power management control Source: ST’s UM1956: STM32 Nucleo-32 Boards 13

Co Cort rtex-M4 M4’s s Me Memory y Ma Map 4GB address space 0xFFFFFFFF NVIC, system timer, system control block, System 0.5 GB vendor-specific memory (e.g., boot loader) 0xE0000000 External RAM Off-chip memory for data 1 GB 0xA0000000 External Device E.g., SD card 1 GB 0x60000000 E.g., timers, GPIO Peripherals 0.5 GB 0x40000000 SRAM On-chip SRAM, for heap, stack, and code 0.5 GB 0x20000000 Code On-chip flash, storing application code 0.5 GB 0x00000000 Based on lecture slides and video clips by Dr. Yifeng Zhu 14

Da Data Memor ory 0xFFFFFFFF 0x3FFFFFFF System 0.5 GB 0xE0000000 External RAM 1 GB 0xA0000000 External Device 1 GB 0x2000FFFF Stack 0x60000000 Peripherals 0.5 GB Actual RAM for 0x40000000 STM32L432KC SRAM 0.5 GB Heap (64KB) 0x20000000 Code Global Variables 0.5 GB 0x00000000 0x20000000 Based on lecture slides and video clips by Dr. Yifeng Zhu 15

Instruc Ins uction M n Memo emory 0xFFFFFFFF 0x1FFFFFFF System 0.5 GB Reserved 0xE0000000 0x0803FFFF External RAM 1 GB RW Data Section Actual flash for 0xA0000000 STM32L432KC RO Data Section (256KB) External Device Text Section 1 GB Interrupt Vector Table Initial Stack Pointer 0x60000000 0x08000000 Peripherals 0.5 GB 0x40000000 Reserved default SRAM 0.5 GB mapping 0x20000000 Interrupt Vector Table Code 0.5 GB Initial Stack Pointer 0x00000000 0x00000000 Based on lecture slides and video clips by Dr. Yifeng Zhu 16

NV NVIC Op Operation ion • When an interrupt signal is detected, NVIC looks up the ISR address from the interrupt vector table • The address is then passed to the CPU Interrupt Vector Table Interrupt Position Memory Address of ISR (8 bits) (32 bits) 1 Address of ISR for interrupt 1 2 Address of ISR for interrupt 2 3 Address of ISR for interrupt 3 : : Based on lecture slides and video clips by Dr. Yifeng Zhu 17

In Inter errup upt V Vec ector T Tabl ble Stack : Reserved for initial MSP Reset_Handler() Code executed after reset : SysTick_Handler() Code executed every system tick WWDG_IRQHandler() ISR for WWDG interrupt : : : : Address for n th interrupt = 64 + 4 n Taken from RM0394: Reference Manual for STM32L41xx/2xx/3xx/4xx/5xx/6xx 18

Ex Example: ample: IS ISR A Addre ddress ss Find the interrupt vector table entry that contains the address of EXTI Line3 interrupt handler • EXTI Line3 interrupt’s position is 9 ◦ Entry address = 64 + 4*9 = 100 = 0x64 • Notes: ISR address found in the table entry always has LSB set to 1 to indicate THUMB instruction set 19

Sin Single gle I Interrupt O Operation ion EXTI3 Based on lecture slides and video clips by Dr. Yifeng Zhu 20

Co Cort rtex-M4 M4’s s Interru rrupt Pri riori rities • Four bits à 16 different priorities • The four bits can be divided into ◦ Preemption priorities (0-4 bits) ◦ Sub priorities (0-4 bits) • An interrupt with smaller preemption priority number (higher priority) preempts the execution of an interrupt with larger preemption priority number • For pending interrupts of the same preemption priority, one with the smaller sub priority number will be serviced first 21

Ne Nested Interrupts: : Preemption ion Suppose: * DMA1_Channel2’s priority = 3 * EXTI3’s priority = 5 (The smaller the number, the higher the priority) Based on lecture slides and video clips by Dr. Yifeng Zhu 22

Ne Nested Interrupts: : Tail ail Chain ainin ing • Suppose EXTI4 is of lower priority than EXTI3 • Cortex-M4 optimizes the unnecessary unstacking/stacking operations, saving clock cycles Based on lecture slides and video clips by Dr. Yifeng Zhu 23

Ha Hands nds-On On: : Sw Switch Input and Serial Output

Fe Feature res • Communicates with host computer via VCP ◦ Utilizes C’s printf() function • Debounces switch and filter EMI in pure software ◦ No additional components (resisters, capacitors) required ◦ Utilizes timer for signal sampling 25

Wiring Wi • Connect a switch to pin D4 and GND • D3 is connected to STM32L432KC’s pin PB0 26

Cl Clock k Settings • Configure for 80 MHz system clock generated from 4 MHz MSI, with 32.768 kHz LSE enabled for clock trimming 27

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.