Background w Allen Tanner built an SRAM/ROM generator program back - PDF document

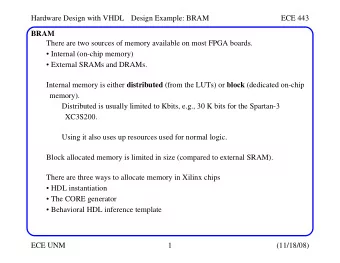

memCellsF09 Single- and Double-port SRAM building blocks Background w Allen Tanner built an SRAM/ROM generator program back in 2004 n the ROM seems to work fine there are fabricated examples that work n the SRAM isnt as good

memCellsF09 Single- and Double-port SRAM building blocks Background w Allen Tanner built an SRAM/ROM generator program back in 2004 n the ROM seems to work fine – there are fabricated examples that work n the SRAM isn’t as good – there are fabricated examples that work and that don’t work w So, I have new (tested) SRAM cells w For ROM, you can still use “ makemem ” n But – Verilog “case” compiled by Synopsys works just as well! Ø 1

ROM ROM V DD Pull-up devices WL [0] GND WL [1] WL [2] GND WL [3] BL [0] BL [1] BL [2] BL [3] Ø 2

ROM ROM Ø 3

ROM Layout Metal1 on top of diffusion WL [0] GND (diffusion) WL [1] Polysilicon Basic cell 10 λ x 7 λ Metal1 WL [2] 2 λ WL [3] Only 1 layer (contact mask) is used to program memory array Programming of the memory can be delayed to one of last process steps ROM Layout Ø 4

makemem 102 vladimir:~> java -cp /uusoc/facility/cad_common/local/Cadence/lib/mem/j makemem -h makemem v2.2 Nov 8, 2004 Allen Tanner University of Utah CS6710 Enter the following: java makemem choice options Where: choice selects the creation of either ROM or SRAM. for ROM enter:-r rname : rname.rom is the file name. : for SRAM enter:-s r c : Version 1 SRAM single port. for SRAM enter:-s1 r c : Version 2 SRAM single port. for SRAM enter:-s2 r c : Version 2 SRAM dual port. for SRAM enter:-s3 r c : Version 2 SRAM triple port. : r is the number of rows (decimal). : c is the number of columns (decimal). : :-h -H : help (no processing occurs when help is requested). :-f fname : output file name. Used with .cif, .v & .il files. :-n sname rname : sname for array top cell name. : : rname for ROM (only) dockable ROM array top cell name :-t n : use tristate buffers on the outputs of ROM. :-q : output hello.txt file to find the working file directory. makemem Limits w Number of rows is limited to 64 by address decoder design n Columns are not restricted w For ROM you can add a tristate bus at the output which is another level of decoding n width must be an even number w SRAM has single, dual, and triple port options Ø 5

ROM vs. Verilog ROM vs. Verilog Ø 6

ROM vs. Verilog ROM vs. Verilog Ø 7

ROM vs. Verilog ROM vs. Verilog Ø 8

ROM vs. Verilog After all this – you should use your cells and Verilog! SRAM w Can be tricky n Make the SRAM bit cells as small as possible n assembled into “ columns ” l A column is bunch of bit cells and the associated support for writing (big drivers) and reading (pullups, sense amps, or inverters) those bits l Column “ height ” is number of words in the memory l Columns are tiled in “ width ” to make the number of bits in a word n addressing hardware on the side l convert binary addresses into unary row addresses Ø 9

Disclaimer w These cells are available for you to use n They have been fabricated and tested w But they’re offered without any warranty! J n Use at your own risk – I think they’ll work, but they’ve only been tested on one test chip n Make sure you understand the protocol and timing n Make sure to simulate with your whole system (behavioral simulation) Protocol and timing w These are async static RAMS – no clock n Apply the Address and wait for data (Q) n Probably around 10ns delay on-chip w They are also static write n Apply Address, WE, and Din n Wait (~10ns) until write happens n For safety, use a 1ns setup time from Address to WE Ø 10

SRAM example (4x8) SRAM cells R/W circuits Address Column decoder SRAM example (4x8) Address Bits Ø 11

SRAM example (4x8) Datain, Qout, and WE signals SRAM 8t Cell Ø 12

SRAM 8t Cell SRAM Cell (4x4) Ø 13

SRAM Column Support SRAM Column Support Ø 14

Double-port SRAM w One RW port, one R-only port w duplicates the read circuits for a second port Double-port SRAM w One RW port, one R-only port w duplicates the read circuits for a second port Ø 15

2-port column support 2-port column support Ø 16

2-port example (32x16) 2-port example (32x16) D, Q, QR, and WE bits RA Bits A Bits Ø 17

memCellsF09 w Building blocks for these SRAMs n /uusoc/facility/cad_common/local/Cadence/lib/OA/memCellsF09 n Make sure to turn “ categories ” on l Things are separated into categories to keep things organized n Both 8t (single-port) and 10t (double-port) columns are available l in 4, 8, 16, and 32rows l Tile them horizontally to get bits in a word l Must be even (columns are two-bits wide) Address Decoders w two kinds: static and pseudoNMOS n static burns less power, but is slower n pseudoNMOS uses more power, but slightly faster n Both have been tested working up to 32x16 Ø 18

memCellsF09 Library Memory Size Comparison 4rows by 8bits 32rows by 16bits 32rows by 16bits Dual port Ø 19

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.