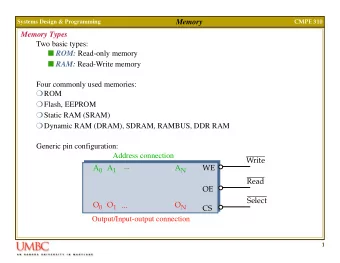

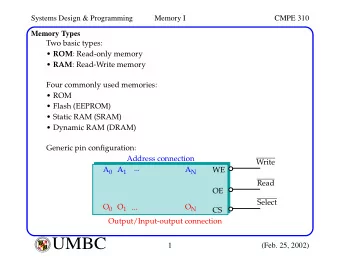

Read Only Memory ROM A read only memory have address inputs and - PowerPoint PPT Presentation

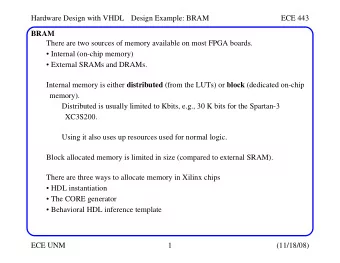

Read Only Memory ROM A read only memory have address inputs and data outputs With m address lines you can 2 m x n access the 2 m different ROM A m-1 memory addresses D n-1 A m-2 At each address, there is one D n-2 data word with n

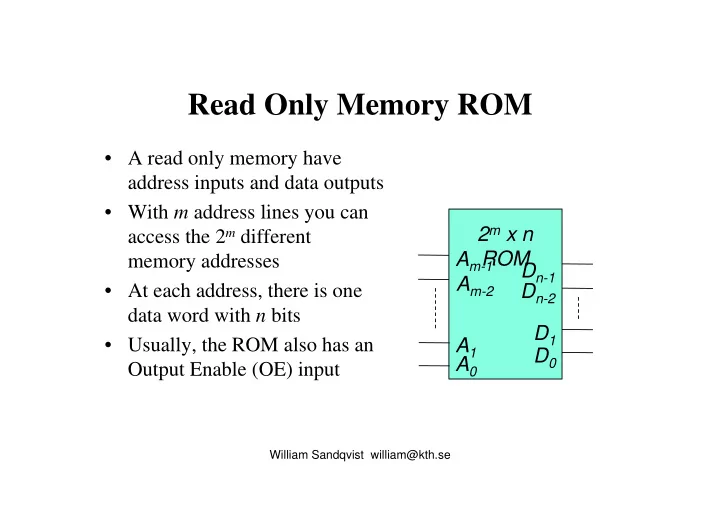

Read Only Memory ROM • A read only memory have address inputs and data outputs • With m address lines you can 2 m x n access the 2 m different ROM A m-1 memory addresses D n-1 A m-2 • At each address, there is one D n-2 data word with n bits D 1 • Usually, the ROM also has an A 1 D 0 A 0 Output Enable (OE) input William Sandqvist william@kth.se

Read Only Memory ROM Exemple of a ROM Read only memory: ROM 4M 512k × 8 bit Chip Enable activates the chip CE Output Enable connects memory to outputs OE (otherwise they are in the three-state mode) William Sandqvist william@kth.se

A small ROM Possible memory content A 2 A 1 A 0 D 3 D 2 D 1 D 0 0 0 0 0 0 1 0 8x4 ROM 0 0 1 0 1 1 0 D 3 0 1 0 1 1 1 1 A 2 D 2 0 1 1 1 1 0 1 A 1 D 1 1 0 0 0 0 1 1 D 0 A 0 1 0 1 0 0 0 0 1 1 0 1 0 0 1 1 1 1 0 0 1 1 William Sandqvist william@kth.se

ROM Pullup ”1” V DD GND 0 Ord 0 GND Adress Innehåll Address Content 1 Ord 1 x 1 x 0 z 3 z 2 z 1 z 0 x 0 00 1010 01 0101 x 1 10 1100 2 Ord 2 11 0001 GND 3 Ord 3 OE OE=Output Enable z 3 z 2 z 1 z 0 William Sandqvist william@kth.se

ROM implementation of combinatorical functions Adress Innehåll Address Content z m-1 x n-1 x n-1 …x 1 x 0 z m-1 …z 1 z 0 … … 0…00 1…10 f(x n-1 ,…,x 1 ,x 0 ) 0…01 0…01 z 1 x 1 … … z 0 x 0 1…11 0…01 A ROM having n inputs with m outputs can be used to implement a combinatorial function with m outputs and 2 n min-terms William Sandqvist william@kth.se

ROM implementation of sequence circuit Adress Innehåll Address Content z m-1 x n-1 x n-1 …x 3 x 2 x 1 x 0 z m-1 …z 3 z 2 z 1 z 0 … … f(x n-1 ,…,x 1 ,x 0 ) 0…0000 1…0001 z 4 x 4 0…0001 0…0010 z 3 x 3 … … 1…1111 0…0000 ... ... z 0 x 0 A Moore-machine = one ROM and a CP register with D-flip- flops With feedbacks a ROM can be used to generate sequences and implement state machines William Sandqvist william@kth.se

Read and Write Memory Random Access Memory RAM • RAM-memory has also 2 m x n a Write ( WR ) input A m-1 RAM which allows us to D n-1 A m-2 D n-2 enter a data word at a given address D 1 A 1 D 0 A 0 • D n-1 … D 0 are both inputs and outputs. OE WR William Sandqvist william@kth.se

Read-Write-Memory Random Access Memory RAM Read/Write memory: RD SRAM 4M 512k × 8 bit WR Chip Select activates the chip CS RD read from memory, data outputs are active RD WR write to memory (at write the data outputs are in the three-state mode ) WR William Sandqvist william@kth.se

SRAM Static Random Access Memory • A SRAM-memory consits of a matrix of SRAM-cells Sel • To write ‘Data’ is used at input! Strongest! – ‘Sel’ is set to 1 and the value that Data is on ‘Data’ is stored in the cell • To read ‘Data’ is used as output! – ‘Sel’ is set to 1, and the value from the cell is present at the output William Sandqvist william@kth.se

SRAM Data 1 Data 0 Sel 0 A matrix is formed by 2 m x n SRAM-cells Sel 1 William Sandqvist william@kth.se

SRAM-memory d d d Data inputs n 1 – n 2 – 0 Write tristate buffers are used to ensure that you just either Sel 0 reads or writes Sel 1 Sel 2 a m decoder 0 a 1 Address -to-2 a m m 1 – Sel 2 m 1 ” Read William Sandqvist william@kth.se Data outputs q q q n 1 – n 2 – 0

DRAM Dynamic RAM • SRAM memorycell needs 4 transistors and it becomes too costly to implement a large memory • DRAM memorycell is using only one transistor and one capacitor William Sandqvist william@kth.se

DRAM Memorycell Bit Line • DRAM-cell consists of Word Line only one transistor and one capacitor • Skrivning C 1-bit DRAM – To load the cell the word cell line is set to ‘1’ • The cell now optains the value from the bit line William Sandqvist william@kth.se

DRAM Memorycell • To read is a little bit more complex Bit Line – You do not want to lose the Word Line information when reading! – The bit-line is set at a voltage between the High and Low – To read the cell the word line is set to C ‘1’ 1-bit DRAM • The bitline now adjusts it’s voltage to a cell voltage up or down • An extra circuit (per bit line) senses the current change direction to create a real 0 or 1 • Aftervards the charge in the capacitor C must be restored! William Sandqvist william@kth.se

DRAM Memory Chip 256Mbit (32M × 8) Memorymodule with 8 chips William Sandqvist william@kth.se

SRAM vs DRAM • SRAM takes up more space but a DRAM requires a simpler access logic and is therefore faster (but also more expensive) • DRAM is used for random access memories in our regular computers • When you remove the power you loses the contents of SRAM or DRAM memory! William Sandqvist william@kth.se

Memory types • Volatile memorys – Memories lose their information if power is disconnected • static RAM (SRAM) • dynamic RAM (DRAM) • Non-volatile memorys – Memories keep their information if power is disconnected • Flash (blockwise writing) • EPROM, EEPROM (bytewise writing) We need a combination of different memories in an electrotechnical design! William Sandqvist william@kth.se

Flash-memory • Non-volatile memory • low cost and low power consumption • can be erased and updated but it takes much more time than in a RAM-memory William Sandqvist william@kth.se

EPROM Erasable Programmable ROM Programmable ROM (can be programmed with a chip programmer) Erasable - can be erased using ultraviolet light and then reprogrammed. Hence the "window" on the top side of the chip. When working with modern electronic equipment you will not have to meet the EPROM. William Sandqvist william@kth.se

Memory technologies Technology Accesstime Cost $/GB SRAM 1 ns 1000 DRAM 50 ns 100 HDD 10 ms 1 Fast memory is expensive and inexpensive memories are slow! Principle numbers. William Sandqvist william@kth.se

Logic in a microprocessor There are both combinatorial and sequential logic in a processor. Control logik is a statemachine while the ALU are mostly combinatorial. William Sandqvist william@kth.se

Registry element Symbol D in D D D ut ut in WR WR > Clock 1 logic element WR / hold in a FPGA WR = 1 synchronous writing WR = 0 hold William Sandqvist william@kth.se

Register Symbol WR > 32 bit register is 32 logic elements in a FPGA William Sandqvist william@kth.se

Program counter -register Program memory: Byteaddressed Register: hoppadress ”4” JA An instruction is 4 ADD bytes PC, Program Counter counts up with "4" after each instruction. Jump/Run MUX 32 bit instruktion At the program Register: programräknare jumps PC is loaded > PC with the jump Clock address JA (Jump All processors have a program counter Address) and then the program pointing out where the next instruction is continues from to be fetched in the memory. there. William Sandqvist william@kth.se

Register with threestateoutpot Symbol WR OE > Symbol bidirectional (inputs and outputs are connected together) WR OE > William Sandqvist william@kth.se

Register and Databus 1 0 0 1 WR WR OE OE > > Databus Several bidirectional registers with three state outputs can be connected to each other to form a common data bus. William Sandqvist william@kth.se

Register and Databuss 0 1 1 0 WR WR OE OE > > Databus Data can now be controlled to be copied between all registers on the data bus. William Sandqvist william@kth.se

Dubble port register Symbol WR OE1 OE2 > More Dubble portregisters can be paired with each other for two common output buses. William Sandqvist william@kth.se

Mikrocomputer - architecture The computer registers. A 32 × 32 bit dubbleport Register File William Sandqvist william@kth.se

Mikrocomputer - add Example Add instruction 1. The instruction add R1,R2,R3 is fetched from memory (as binary code) 2. The instruction is decoded William Sandqvist william@kth.se

Mikrocomputer - add Example Add instruction 1. The instruction add R1,R2,R3 is fetched from memory (as binary code) 2. The instruction is decoded William Sandqvist william@kth.se

Mikrocomputer - add Example Add instruction 3. Register R2 and R3 are add with the ALU 4. The Result is written to register R1 William Sandqvist william@kth.se

Mikrocomputer - add Example Add instruction 3. Register R2 and R3 are add with the ALU 4. The Result is written to register R1 it requires several clock pulse periods for the implementation of an instruction. (maybe you could arrange a Pipeline? ) William Sandqvist william@kth.se

Register file The processor has a 32 × 32 bit register file (with dual port registers). It can therefore be simultaneously read from any two registers or write to a register per clock pulse. The computer instruction add R1, R2,R3 add , means the sum R2+R3 is put in R1 R0 … R31 A register file whith 32 registers 32 × 32 bit register file are 32 2 = 1024 logic elements in a FPGA ADD A 32 bit adder are 32 logic- elements in a FPGA William Sandqvist william@kth.se

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.