A Low-Power MTJ-Based Nonvolatile FPGA Using Self-Terminated - PowerPoint PPT Presentation

26th International Conference on Field-Programmable Logic and Applications 29th August 2nd September, 2016, Lausanne, Switzerland Session S4b 31st August 10:30-12:35 A Low-Power MTJ-Based Nonvolatile FPGA Using Self-Terminated

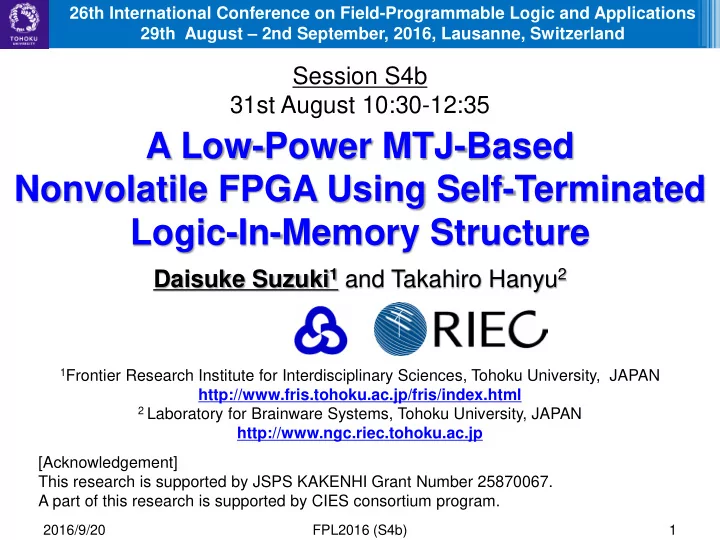

26th International Conference on Field-Programmable Logic and Applications 29th August – 2nd September, 2016, Lausanne, Switzerland Session S4b 31st August 10:30-12:35 A Low-Power MTJ-Based Nonvolatile FPGA Using Self-Terminated Logic-In-Memory Structure Daisuke Suzuki 1 and Takahiro Hanyu 2 1 Frontier Research Institute for Interdisciplinary Sciences, Tohoku University, JAPAN http://www.fris.tohoku.ac.jp/fris/index.html 2 Laboratory for Brainware Systems, Tohoku University, JAPAN http://www.ngc.riec.tohoku.ac.jp [Acknowledgement] This research is supported by JSPS KAKENHI Grant Number 25870067. A part of this research is supported by CIES consortium program. 2016/9/20 FPL2016 (S4b) 1

Background FPGA (Field-Programmable Gate Array) → Various digital systems are implemented with short design time and low cost. Power density [W/cm 2 ] Active 10 1 Standby 10 -1 10 -2 10 3 10 2 10 1 CMOS Technology [nm] [Ref.] Y. Liu, et al., ISSCC, pp. 84-85, Feb. 2016. [Ref.] E. Pop, Nano Res. 3 (2010) 147. A large number of HW components Large amount of standby power are embedded for reconfigurability due to nano-scale CMOS process ⇒ Low area & energy efficiency How to overcome standby power problem of FPGA? 2016/9/20 FPL2016 (S4b) 2

MTJ Device •High endurance •Scalability •CMOS compatibility R P R AP (Low res.) (High res.) •3D-stacking Storage ReRAM Atom CAAC- SRAM MTJ device element device switch IGZO No Nonvolatile Yes Yes Yes Yes Scalability + ++ ++ -- ++ - -- + ++ Endurance ++ Write access ++ + - + ++ MTJ device is the best candidate for realizing nonvolatile logic. 2016/9/20 FPL2016 (S4b) 3

MTJ-Based Nonvolatile Logic Families 1 st Generation 2 nd Generation Storage and logic functions are merged. Storage elements are replaced → Logic-in-memory (LIM) structure by nonvolatile ones. MTJ MTJ MTJ MTJ MTJ MTJ SRAM LIM LIM SRAM FF Logic FF Logic MRAM Si Si JSPS FIRST program (Leader Prof. H. Ohno) T. Ohsawa, et al., VLSIC, 2013. S. Matsunaga, et al., VLSIC, 2013. N. Sakimura, et al., ISSCC, 2014. D. Suzuki, et al., VLSIC, 2015. MTJ device is the best candidate for realizing Nonvolatile logic LSI. 2016/9/20 FPL2016 (S4b) 4

Design Issue Tile Configuration data Logic Element (LE) Routing switch SEL CLB CB D Lookup Latch n CFGC p-MTJ table (LUT) MUX X FF device Z CB SB CLB: Configurable logic block CB: Connection block SB: Switch block CFGC: Configuration circuit Dynamic Recall Backup Power Static Static (Power on) (Power off) Time 1. Reduction of the overhead due to recall/backup operations 2. Reduction of the number of leakage current paths 2016/9/20 FPL2016 (S4b) 5

Logic-In-Memory Structure V D V D Leakage D D Buffer D SA/buffer (shared) D path NMOS multiplexer NMOS multiplexer X X 6 tree tree 6 64 64 64-bit nonvolatile SRAM V DD MTJ configuration array WT MTJ6 MTJ0 MTJ1 (shared) SA SA SA 3 WT WT WT MTJ6 MTJ0 MTJ1 3 SA: Sense amplifier WT: Write transistor WT WT WT Both SAs and WDs are shared. Nonvolatile SRAM based Proposed Compact circuitry with small number of leakage current paths 2016/9/20 FPL2016 (S4b) 6

Self-Terminated Power-Gating Scheme V DD V DD V DD Power switch N0 N2 SLP N1 F[0] PG controller F[1] FF0 F[0] PGEN GND FF1 F[2] F[1] FF2 F[2] PGEN GND I TOTAL FF[1] FF[0] FF[2] Done Done Done w/o self- I B [1] termination I B [0] I B [2] I L Time t 1 t 0 t 2 t WORST Minimization of both backup energy and leakage energy. 2016/9/20 FPL2016 (S4b) 7

Evaluation 30 SRAM-based NVSRAM based Proposed Frequency: 100 MHz α : 20% T c: 5 µ s t R : 2 ns 25 Total power [mW] 20 15 10 5 0 alu4 apex2 apex4 bigkey clma des diffeq dsip elliptic ex1010 ex5p frisc misex3 pdc s298 s38417 s38584.1 seq spla tseng Average Proposed SRAM-based NVSRAM based Average 19.8mW 3.12 mW 1.97 mW total power 2016/9/20 FPL2016 (S4b) 8

Thank you! 2016/9/20 FPL2016 (S4b) 9

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.