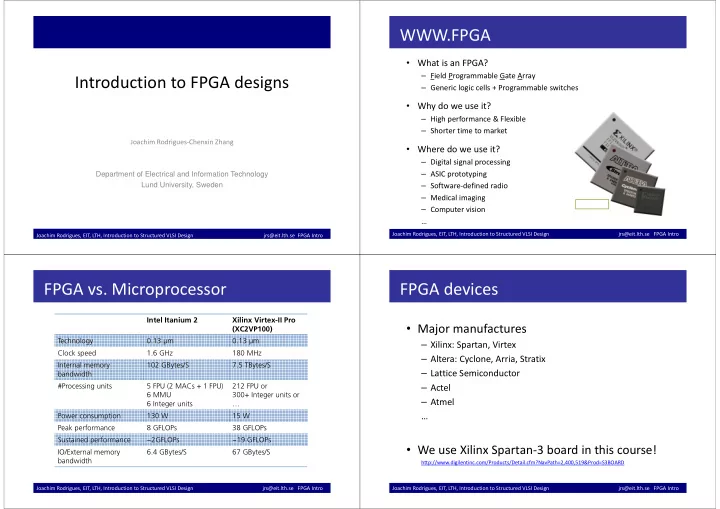

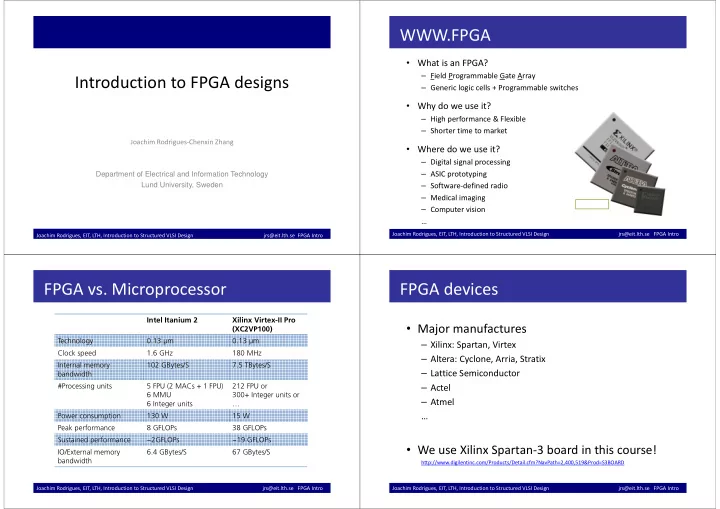

WWW.FPGA • What is an FPGA? – Field Programmable Gate Array Introduction to FPGA designs – Generic logic cells + Programmable switches • Why do we use it? – High performance & Flexible – Shorter time to market Joachim Rodrigues ‐ Chenxin Zhang • Where do we use it? – Digital signal processing Department of Electrical and Information Technology – ASIC prototyping Lund University, Sweden – Software ‐ defined radio – Medical imaging – Computer vision … Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se FPGA Intro Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se FPGA Intro FPGA vs. Microprocessor FPGA devices Intel Itanium 2 Xilinx Virtex-II Pro • Major manufactures (XC2VP100) Technology 0.13 µm 0.13 µm – Xilinx: Spartan, Virtex Clock speed 1.6 GHz 180 MHz – Altera: Cyclone, Arria, Stratix Internal memory 102 GBytes/S 7.5 TBytes/S – Lattice Semiconductor bandwidth #Processing units 5 FPU (2 MACs + 1 FPU) 212 FPU or – Actel 6 MMU 300+ Integer units or – Atmel 6 Integer units … … Power consumption 130 W 15 W Peak performance 8 GFLOPs 38 GFLOPs Sustained performance ~2GFLOPs ~19 GFLOPs • We use Xilinx Spartan ‐ 3 board in this course! IO/External memory 6.4 GBytes/S 67 GBytes/S bandwidth http://www.digilentinc.com/Products/Detail.cfm?NavPath=2,400,519&Prod=S3BOARD Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se FPGA Intro Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se FPGA Intro

Xilinx Spartan ‐ 3 FPGAs (I) Xilinx Spartan ‐ 3 FPGAs (II) • XC3S200: • A RAM ‐ based architecture – 480 CLBs = 480*4 Slices = 480*4*2*(4 ‐ input LUTs + registers) – 12 18 ‐ kbit dual ‐ port BRAMs = 12*18 Kb = 216 Kbits – Configurable Logic Blocks (CLBs) 12 18 ‐ bit dedicated multipliers – – Programmable switches – 4 Digital Clock Managers (DCMs) – Input/Output Blocks (IOBs) – 173 User I/Os LUT-based logic cell Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se FPGA Intro Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se FPGA Intro Xilinx Spartan ‐ 3 FPGAs (III) Xilinx Spartan ‐ 3 FPGAs (IV) • Example: 2 ‐ bit adder (s = a + b) b1 a1 b0 a0 s1 s0 0 0 0 0 0 0 0 0 0 1 0 1 Carry generation 0 0 1 0 0 1 s0 0 0 1 1 1 0 0 0 0 0 1 1 0 1 0 1 1 1 0 1 1 0 1 1 0 1 1 1 0 0 1 0 0 0 1 0 1 0 0 1 1 1 1 0 1 0 1 1 1 0 1 1 0 0 Sum generation 1 1 0 0 0 0 s1 Each slice contains 2 LUT-based 1 1 0 1 0 1 logic cells and 4 slices form a CLB 1 1 1 0 0 1 1 1 1 1 1 0 Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se FPGA Intro Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se FPGA Intro

Clock Non ‐ Idealities • Clock skew – Spatial variation in temporally equivalent clock edges. – Skew is a time offset of the clocks. It is a fixed difference between technically identical clocks caused by intra ‐ device clock network, device process variations, and unbalanced loading. • Clock jitter FPGA Clocking resources – Temporal variations in consecutive edges of the clock signal – Jitter occurs due to system noise and signal crosstalk and causes phase uncertainty resulting in ambiguity in the rising and falling edge of a signal. – Jitter can be both random and deterministic. Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se FPGA Intro Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se FPGA Intro Clock Skew Clock Non ‐ Idealities • Both skew and jitter affects the cycle time • Skew might lead to race through the registers • Absolute Skew ‐ Delay from input to leaf cell • Relative Skew ‐ Delay difference between leaf cells Same clock at two different locations of the chip Too much clock skew may: 1) Force you to reduce clock rate 2) Cause malfunction at any clock rate t skew t jitter Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se FPGA Intro Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se FPGA Intro

Distributed Buffers in H-tree Synthesized Clock tree Clock tree in an ASIC Small relative skew Absolute skew of less importance Clock Clock buffers are placed in the core row gaps Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se FPGA Intro Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se FPGA Intro Spartan ‐ III ‐ Clocking resources Spartan III ‐ Clocking resources • 16 Global Clock inputs (GCLK0 through GCLK15) • 8 Right-Half Clock inputs (RHCLK0 through RHCLK7) • 8 Left-Half Clock inputs (LHCLK0 through LHCLK7) • Clock input pins are used automatically when external signals drive clock buffers Each global clock multiplexer buffer can be driven either by the clock pad • to distribute a clock directly to the device, or by the Digital Clock Manager (DCM) • Eight global clocks can be used in each quadrant of the Virtex ‐ II Pro device. Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se FPGA Intro Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se FPGA Intro

Spartan III ‐ Global clock Clock ‐ buffer ‐ VHDL BUFG_inst : BUFG BUFG_inst : BUFG port map ( port map ( • IBUFG is inferred by the O => O, -- Clock buffer output O => O, -- Clock buffer output synthesis tool on any top ‐ I => I -- Clock buffer input I => I -- Clock buffer input level clock port. ); ); -- End of BUFG_inst -- End of BUFG_inst • Global clocks are driven by instantiation instantiation dedicated clock buffers ( IBUFG ), which can also be BUFGCE_1_inst : BUFGCE_1 BUFGCE_1_inst : BUFGCE_1 used to port map ( port map ( O => O, -- Clock buffer ouptput O => O, -- Clock buffer ouptput – gate the clock ( BUFGCE ) CE => CE, -- Clock enable input CE => CE, -- Clock enable input – multiplex between two I => I -- Clock buffer input I => I -- Clock buffer input independent clock inputs ); ); ( BUFGMUX ). -- End of BUFGCE_1_inst instantiation -- End of BUFGCE_1_inst instantiation Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se FPGA Intro Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se FPGA Intro Digital Clock Manager (DCM) DCM ‐ Properties • Clock De ‐ skew . Generates new • Spartan III accommodates 4 system clocks (internal or DCM’s external to FPGA), phase ‐ aligned to the input clock for eliminating • DCM introduces phase shift, clock clock distribution delays. division/multiplication • Can be instantiated by direct instantiation, or Coregen • Skew less clock distribution • Frequency Synthesis . Generates a wide range of output clock frequencies performing very flexible clock multiplication and division. • Phase Shifting . Performs forward or backward (positive or negative) phase shift. Implement coarse 90° phase shifting (0°, 90°, 180°, and 270°) Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se FPGA Intro Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se FPGA Intro

Recommend

More recommend