A 1MS/s to 1GS/s Ringamp-Based Pipelined ADC with Fully Dynamic - PowerPoint PPT Presentation

A 1MS/s to 1GS/s Ringamp-Based Pipelined ADC with Fully Dynamic Reference Regulation and Stochastic Scope-on-Chip Background Monitoring in 16nm Benjamin Hershberg, Nereo Markulic, Jorge Lagos, Ewout Martens, Davide Dermit, Jan Craninckx imec,

A 1MS/s to 1GS/s Ringamp-Based Pipelined ADC with Fully Dynamic Reference Regulation and Stochastic Scope-on-Chip Background Monitoring in 16nm Benjamin Hershberg, Nereo Markulic, Jorge Lagos, Ewout Martens, Davide Dermit, Jan Craninckx imec, Leuven, Belgium 2020 Symposia on VLSI Technology and Circuits CD1.1

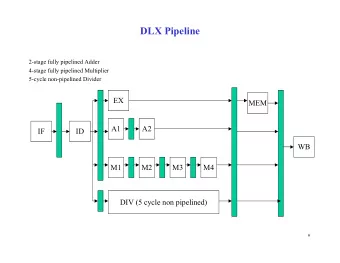

Architecture Overview INp c BACKEND STG1 STG2 STG3 STG4 STG5 STG6 STG7 1.5b 1.5b 1.5b 1.5b 1.5b 1.5b 1.5b 1.5b + 3b c INm C TOT = C TOT = C TOT = C TOT = C TOT = C TOT = C TOT = C TOT = master clock c 256fF 128fF 128fF 128fF 128fF 128fF 128fF 256fF VREFP dirty VREFP ext. c VREFP clean VCM ext. c reference VCM VREFM ext. c regulator VREFM dirty VREFM clean Ringamp “deep” pipeline based on: • • New in this work: [Hershberg, ISSCC 2019, Paper 3.6] – Reference Regulation [Hershberg, ISSCC 2019, Paper 3.1] – Stochastic Scope-on-Chip – Fully Dynamic Power Consumption – Asynchronous event-driven timing control – Ringamp Topology – MDAC with passive-hold mode in STG1 – Early quantization in STG2-9 2020 Symposia on VLSI Technology and Circuits CD1.1 Slide 1

Outline • Ringamp Topology • Fully Dynamic Reference Regulation • Scope-on-Chip Amplifier Settling Monitor • Performance Summary & Conclusion 2020 Symposia on VLSI Technology and Circuits CD1.1 Slide 2

Ringamp Topology • What is a ringamp? – Multi-stage amplifier INp OUTm – Dominant output pole – Dynamic stabilization ☺ High efficiency ☺ High linearity ☺ High speed ☺ Wide output swing ☺ Fully dynamic (switchable) [Hershberg, JSSC 2012] ☺ Scales with Digital 2020 Symposia on VLSI Technology and Circuits CD1.1 Slide 3

Ringamp Topology VDD • Fully-Differential INp INm • Multi-Path CMFB DZN DZN V DD V DD • Trapped-Charge OUTm OUTp EN EN EN EN EN EN EN Biasing V SS V SS DZP DZP • CMOS-Resistor • Bias-Enhanced • Self-Resetting VSS B1 • Slew-Done Detector Trapped Charge CMFB Trapped-Charge Bias Control OUTp VDD DZN VSS DZP C FB C SENSE EN EN EN C SMALL EN EN EN 7 C BIG 7 C SENSE C FB Dz_nmos[7:0] Dz_pmos[7:0] OUTm 2020 Symposia on VLSI Technology and Circuits CD1.1 Slide 4

Ringamp Topology VDD • Fully-Differential INp INm • Multi-Path CMFB DZN DZN V DD V DD • Trapped-Charge OUTm OUTp EN EN EN EN EN EN EN Biasing V SS V SS DZP DZP • CMOS-Resistor • Bias-Enhanced • Self-Resetting VSS B1 • Slew-Done Detector Trapped Charge CMFB Trapped-Charge Bias Control OUTp VDD DZN VSS DZP C FB C SENSE EN EN EN C SMALL EN EN EN 7 C BIG 7 C SENSE [Lim, JSSC Dec. 2015] C FB Dz_nmos[7:0] Dz_pmos[7:0] OUTm 2020 Symposia on VLSI Technology and Circuits CD1.1 Slide 5

Ringamp Topology VDD • Fully-Differential INp INm • Multi-Path CMFB DZN DZN V DD V DD • Trapped-Charge OUTm OUTp EN EN EN EN EN EN EN Biasing V SS V SS DZP DZP • CMOS-Resistor • Bias-Enhanced • Self-Resetting VSS B1 • Slew-Done Detector Trapped Charge CMFB Trapped-Charge Bias Control OUTp VDD DZN VSS DZP C FB C SENSE EN EN [Lim, JSSC Dec. 2015] EN C SMALL EN EN EN [Hershberg, ISSCC 2019] 7 C BIG 7 C SENSE C FB Dz_nmos[7:0] Dz_pmos[7:0] OUTm (Paper 3.1) 2020 Symposia on VLSI Technology and Circuits CD1.1 Slide 6

Ringamp Topology VDD • Fully-Differential INp INm • Multi-Path CMFB DZN DZN V DD V DD • Trapped-Charge OUTm OUTp EN EN EN EN EN EN EN Biasing V SS V SS DZP DZP • CMOS-Resistor • Bias-Enhanced • Self-Resetting VSS B1 • Slew-Done Detector Trapped Charge CMFB Trapped-Charge Bias Control OUTp VDD DZN VSS DZP C FB C SENSE EN EN EN C SMALL [Hershberg, ISSCC 2019] EN EN EN 7 C BIG 7 C SENSE C FB Dz_nmos[7:0] Dz_pmos[7:0] (Paper 3.1) OUTm 2020 Symposia on VLSI Technology and Circuits CD1.1 Slide 7

Ringamp Topology VDD • Fully-Differential INp INm • Multi-Path CMFB DZN DZN V DD V DD • Trapped-Charge OUTm OUTp EN EN EN EN EN EN EN Biasing V SS V SS DZP DZP • CMOS-Resistor • Bias-Enhanced • Self-Resetting VSS B1 • Slew-Done Detector Trapped Charge CMFB Trapped-Charge Bias Control OUTp VDD DZN VSS DZP C FB C SENSE EN EN EN C SMALL EN EN EN 7 C BIG 7 C SENSE [Lagos, JSSC Feb. 2019] C FB Dz_nmos[7:0] Dz_pmos[7:0] OUTm 2020 Symposia on VLSI Technology and Circuits CD1.1 Slide 8

Ringamp Topology VDD • Fully-Differential INp INm • Multi-Path CMFB DZN DZN V DD V DD • Trapped-Charge OUTm OUTp EN EN EN EN EN EN EN Biasing V SS V SS DZP DZP • CMOS-Resistor • Bias-Enhanced • Self-Resetting VSS B1 • Slew-Done Detector Trapped Charge CMFB Trapped-Charge Bias Control OUTp VDD DZN VSS DZP C FB C SENSE EN EN [Chen, TCASII 2018] EN C SMALL EN EN EN 7 C BIG 7 C SENSE C FB [Lagos, JSSC Mar. 2019] Dz_nmos[7:0] Dz_pmos[7:0] OUTm 2020 Symposia on VLSI Technology and Circuits CD1.1 Slide 9

Ringamp Topology VDD • Fully-Differential INp INm • Multi-Path CMFB DZN DZN V DD V DD • Trapped-Charge OUTm OUTp EN EN EN EN EN EN EN Biasing V SS V SS DZP DZP • CMOS-Resistor • Bias-Enhanced • Self-Resetting VSS B1 • Slew-Done Detector Trapped Charge CMFB Trapped-Charge Bias Control OUTp VDD DZN VSS DZP C FB C SENSE EN EN EN C SMALL EN EN EN 7 C BIG 7 C SENSE [Lagos, JSSC Mar. 2019] C FB Dz_nmos[7:0] Dz_pmos[7:0] OUTm 2020 Symposia on VLSI Technology and Circuits CD1.1 Slide 10

Ringamp Topology VDD • Fully-Differential INp INm • Multi-Path CMFB • Trapped-Charge OUTm OUTp Biasing • CMOS-Resistor • Bias-Enhanced • Self-Resetting VSS B1 • Slew-Done Detector Trapped Charge CMFB Trapped-Charge Bias Control OUTp VSS DZP VDD DZN C FB C SENSE EN EN EN C SMALL EN EN EN 7 C BIG 7 C SENSE [Lagos, JSSC Mar. 2019] C FB Dz_nmos[7:0] Dz_pmos[7:0] OUTm 2020 Symposia on VLSI Technology and Circuits CD1.1 Slide 11

Ringamp Topology INm INp EN EN • Fully-Differential A C + OUTp BN BP BP BN OUTm • Multi-Path CMFB B D slew done detected • Trapped-Charge EN EN Biasing • CMOS-Resistor slew done detector • Bias-Enhanced slew done t d EN • Self-Resetting slew done detected • Slew-Done Detector [Hershberg, ISSCC 2019] (Paper 3.6) 2020 Symposia on VLSI Technology and Circuits CD1.1 Slide 12

Ringamp Topology INm INp EN EN • Fully-Differential A C + OUTp BN BP BP BN OUTm • Multi-Path CMFB B D slew done detected • Trapped-Charge EN EN Biasing • CMOS-Resistor slew done detector • Bias-Enhanced slew done t d EN • Self-Resetting slew done Not Mandatory detected • Slew-Done Detector Using a fixed time- delay to generate [Hershberg, ISSCC 2019] slew done also ok. (Paper 3.6) 2020 Symposia on VLSI Technology and Circuits CD1.1 Slide 13

Outline • Ringamp Topology • Fully Dynamic Reference Regulation • Scope-on-Chip Amplifier Settling Monitor • Performance Summary & Conclusion 2020 Symposia on VLSI Technology and Circuits CD1.1 Slide 14

Fully Dynamic Reference Regulation • Goal: fully dynamic power for complete system (core + reference) – Constant FoM for any clock rate – Enables reconfigurable, multi-standard ADCs • ADC core fully dynamic by design ✓ [Hershberg, ISSCC 2019, Paper 3.6] – Enabler: Asynchronous timing control – Enabler: Ring amplifier with fast on/off switching • Reference Regulation – How can we make this fully dynamic too? 2020 Symposia on VLSI Technology and Circuits CD1.1 Slide 15

Fully Dynamic Reference Regulation • Discrete Time Regulator Loop VREF ext. + – Comparator monitors replica level prepare Charge source replica out – Feeds back “charge packet” (C P ) V DD C P update into charge reservoir (C R ) C R R load connect prepare prepare connect [Kull, JSSC 2013] 2020 Symposia on VLSI Technology and Circuits CD1.1 Slide 16

Fully Dynamic Reference Regulation • Discrete Time Regulator Loop VREF ext. + – Comparator monitors replica level prepare Charge source replica out – Feeds back “charge packet” (C P ) V DD C P update into charge reservoir (C R ) C R R load connect prepare • Limitations prepare – Must source all charge for an ADC conversion in a single charge packet connect – Reference ripple error a problem – Acceptable for ADCs < 8 bit – C R too large for ADCs > 8 bit (> 1nF) [Kull, JSSC 2013] 2020 Symposia on VLSI Technology and Circuits CD1.1 Slide 17

Proposed: Split-Reference Regulation • Key observation: V REF accuracy & Example Settling Waveform current requirements are decoupled w.r.t. time – Initial: large current, low accuracy – Final: small current, high accuracy amplify track IN X OUT Ringamp track track early Example 1.5b flip-around MDAC VREF amplify sub-DAC 2020 Symposia on VLSI Technology and Circuits CD1.1 Slide 18

Proposed: Split-Reference Regulation • Key observation: V REF accuracy & Example Settling Waveform current requirements are decoupled w.r.t. time – Initial: large current (98%), low accuracy – Final: small current (2%), high accuracy amplify track IN X OUT Ringamp track track early Example 1.5b flip-around MDAC VREF amplify sub-DAC 2020 Symposia on VLSI Technology and Circuits CD1.1 Slide 19

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.