DUNE COLD ADC UPDATE #2 Carl Grace, LBNL May 16, 2018 Advancing - PowerPoint PPT Presentation

DUNE COLD ADC UPDATE #2 Carl Grace, LBNL May 16, 2018 Advancing Science by Design ENGINEERING DIVISION 1 Carl Grace Reminder from last time Cold ADC is a 16-channel, 12-bit, 2 MS/s Digitizer ASIC to replace the current ADC ASIC

DUNE COLD ADC UPDATE #2 Carl Grace, LBNL May 16, 2018 Advancing Science by Design ENGINEERING DIVISION 1 Carl Grace

Reminder from last time • Cold ADC is a 16-channel, 12-bit, 2 MS/s Digitizer ASIC to replace the current ADC ASIC • Designed by joint team from LBNL, FNAL, and BNL • Key design goal: first time success • Cold ADC uses a conservative, industry-standard design with digital self-calibration • Besides functionality and reliability, design goal is low- noise operation • Design contains significant features for risk mitigation and observability Advancing Science by Design ENGINEERING DIVISION 2 Carl Grace

Outline • Design Partitioning • Current Status • BJT Measurements and Backup Reference • A Note on Risk Mitigation (Functional Verification) • New Simulated Results Advancing Science by Design ENGINEERING DIVISION 3 Carl Grace

Design Responsibilities VDD/VSS domains Cold ADC DIG_CLKOUT(P/N) BUFFER S/H IN0 DIG_FRAME(P/N) DIG_OUTA(P/N) 30 16 16 DIG_OUTB(P/N) 8-1 Calibration 12-bit 16 MS/s Correction DIG_OUTC(P/N) MUX Engine Pipelined ADC Logic DIG_OUTD(P/N) DIG_OUTE(P/N) DIG_OUTF(P/N) BUFFER S/H IN7 DIG_OUTG(P/N) ADC Reference Data LVDS DIG_OUTH(P/N) Buffers Formatter I/O LVDS_REF IN8 BUFFER S/H CLK_64MHZ(P/N) CLK_16MHZ(P/N) 30 16 16 CLK_2MHZ(P/N) 8-1 Calibration 12-bit 16 MS/s Correction MUX Pipelined ADC Engine Logic VMONITOR IMONITOR IN15 BUFFER S/H I2C_(SCL,SDA, Configuration I2C BNL SDO) and Debug BUFFER + S2D Interface BJT-based CMOS-based LBNL Reference Reference UART MISO/MOSI Generation Generation FNAL I2C_ADD VREF(P,N,CMI,CMO), BGR SSO_(FRAME, DATA[1:0], CLK) Advancing Science by Design ENGINEERING DIVISION 4 Carl Grace

Outline • Design Partitioning • Current Status • BJT Measurements and Backup Reference • A Note on Risk Mitigation (Functional Verification) • New Simulated Results Advancing Science by Design ENGINEERING DIVISION 5 Carl Grace

Current Status • 1 st Pass of chip schematics complete • Currently undergoing deep review process, where each team reviews circuits of other teams to improve quality • Setting up Analog/Digital co-simulations • A few blocks have been laid out to exercise design flow; comprehensive layout design to begin after deep review • Cold ADC is on-track for summer submission Advancing Science by Design ENGINEERING DIVISION 6 Carl Grace

Outline • Design Partitioning • Current Status • BJT Measurements and Backup Reference • A Note on Risk Mitigation (Functional Verification) • New Simulated Results Advancing Science by Design ENGINEERING DIVISION 7 Carl Grace

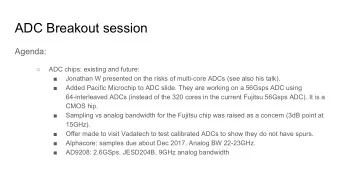

BJT Measurements • Bipolar transistors (BJTs) are critical for accurate reference voltage generation • Unfortunately, the cold models available for LAr temperature do not include BJTs • As luck would have it, LBNL developed a chip in 2011 in the same process (65nm) at the same foundry, that happened to include some BJT test structures • Both BNL and LBNL measured some of these devices at cold and correlated their results to inform the design of a BJT-based voltage reference Advancing Science by Design ENGINEERING DIVISION 8 Carl Grace

BJT Bonding Each test device is a 5x5 array of standard BJTs Advancing Science by Design ENGINEERING DIVISION 9 Carl Grace

BJT Measurements (77 K) IE X VE WITH VB=VC=0, 77K LBNL 1.00E-01 0 0.2 0.4 0.6 0.8 1 1.2 1.00E-03 1.00E-05 IE(A) 1.00E-07 1.00E-09 1.00E-11 1.00E-13 VE(V) Measurements mostly agree, but simulation more than an order-of- magnitude off! BNL Can use measured values to build a voltage reference, but we only measured a single device from one fabrication run done 7 years ago… Design CMOS reference for backup Advancing Science by Design ENGINEERING DIVISION 10 Carl Grace

CMOS Reference (current ref) Startup VDDA TRIM<2:0> MP3 MP6-8 MP4 MP5 RPULLUP KICKSTART_B MP1 MP2 IREF MN5 RDROP Adjust reference current using trim MN2 and monitor output MN1 MN4 INT EXT MN3 RBIAS RBIAS_EXT CMOS reference Advancing Science by Design ENGINEERING DIVISION 11 Carl Grace

CMOS Reference (simulation) About 5% shift in bias current across temperature. Not amazing but good enough for ADC. Advancing Science by Design ENGINEERING DIVISION 12 Carl Grace

Outline • Design Partitioning • Current Status • BJT Measurements and Backup Reference • A Note on Risk Mitigation (Functional Verification) • New Simulated Results Advancing Science by Design ENGINEERING DIVISION 13 Carl Grace

Design Risk Mitigation BLOCK WORK-AROUND Buffer Bypass (directly connect LARASIC to ADC) ADC References Bypass (use external references) Bandgap Reference Select or bypass (use CMOS-based reference, external BGR, or external references) Bias Currents Highly adjustable to improve settling or reduce power at cold (for instance) Calibration Algorithm Calibrate off-line and load gain estimates into register file Correction Logic Use uncalibrated (traditional) ADC output Digital Interface to colData Route ADC data through SSO (can still evaluate ADC performance) Configuration Interface Read and Write with either I2C or UART ADC Gain Boosting Include gain booster kill switch Advancing Science by Design ENGINEERING DIVISION 14 DUNE Cold ADC

Design Risk Mitigation • During the drafting of the DUNE Technical Proposal, Gary Varner made the astute observation that while there are myriad benefits of high ASIC configurability, designing in so many knobs has its own risks and should be acknowledged. He is quite right. • Through the use of a design methodology known as Functional Verification, I claim that the unknown risks of device variability at cold temperature can be converted to the risk of botched configurability, and that second risk can be retired. Advancing Science by Design ENGINEERING DIVISION 15 Carl Grace

Model-based functional verification • Exhaustive regression testing • Check every mode and every setting (still possible in analog) Section 1: Berkeley Lab Mission • Automate pass/fail tests (create self-checking testbenches) SUBTITLE HERE IF NECESSARY • Model-based Verification • Replaces transistor-level circuit with model • Dramatically accelerates simulation • Moves verification early into design cycle (improves top-down design) • Simplifies re-use of analog blocks • Full-chip verification • Use common environment to verify functionality of complex mixed-signal loops such as gain control, frequency synthesis, or calibration Advancing Science by Design ENGINEERING DIVISION 16

Example of functional verification 12 ADC channels Synthesized Logic 11.9 mm 3 Serial TXs PLL 5.4 mm 3 Serial TXs Biasing 12 ADC channels Reference Gen HIPSTER (High-Speed Image Preprocessor Targeted for Electron Readout - 2015) HIPSTER contained 549 configuration bits (PLL/EQ settings, ADC biasing, power downs, etc) (Cold ADC has 381 configuration bits) Using Functional Verification HIPSTER had zero configuration bit errors on first silicon Advancing Science by Design ENGINEERING DIVISION 17 Presenter Name

Outline • Design Partitioning • Current Status • BJT Measurements and Backup Reference • A Note on Risk Mitigation (Functional Verification) • New Simulated Results Advancing Science by Design ENGINEERING DIVISION 18 Carl Grace

ADC Simulation (schematic) 16-bit ideal DAC readback 13 kHz full-scale sine input Uncalibrated output Advancing Science by Design ENGINEERING DIVISION 19

ADC Comparator Simulation Room temperature Monte Carlo (400 runs) (spec. 62.5 mV-rms) Advancing Science by Design ENGINEERING DIVISION 20 Presenter Name

Backup Slides BACKUP Advancing Science by Design ENGINEERING DIVISION 21 Presenter Name

Reference Buffers • Reference Buffers drive ADC references • Need to settle to better than about 0.25 LSB between samples (define settling time as 1/3 clock period @ 20 MS/s for margin) • Need Low Noise 𝑂 ideal Pipelined ADC 𝑊 = −1 + 𝐸(𝑗) transfer function 𝑗𝑜 2 𝑗−1 𝑊 𝑠𝑓𝑔 𝑗=1 • Noise in reference directly couples to input of ADC Advancing Science by Design ENGINEERING DIVISION 22 Carl Grace

Reference Buffers (cont.) Two Basic Approaches: • 1. Slow, but don’t budge! Need a heavy capacitance L bondwire R trace V ref_external V ref_internal C d_ext C d_local C d_int • 2. Fast so you can settle before next kick Fast Buffer V ref Gen V ref_internal C d_local Advancing Science by Design ENGINEERING DIVISION 23 Carl Grace

Reference Buffers (cont.) Approach 1 (low speed) • We need C d_ext to be large enough that switching ADC capacitors doesn’t change V ref more than 0.25 LSB • Δ Q = C ADC V MAX = 8 pF *1.5 V = 12 pC • Allowed Δ V = LSB/4 = 3.0/2 14 = 183 µV • C d_ext = Δ Q/ Δ V = 12 pC / 183 µV = 66 nF (off-chip needed) • Need to be mindful of capacitor speed and series inductance + resistance Advancing Science by Design ENGINEERING DIVISION 24 Carl Grace

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.