ADC and DAC on Red Pitaya Goal: Review the ADC and DAC digital - PowerPoint PPT Presentation

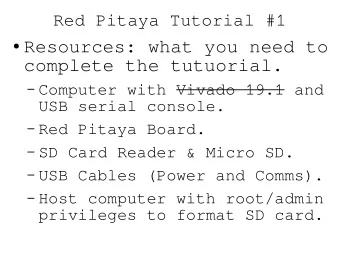

ADC and DAC on Red Pitaya Goal: Review the ADC and DAC digital interfaces. Understand the modifications to the Base Design to enable the ADC and DAC on the dev board. Meeting timing. Differences between 2017.2 and 2019.1.

ADC and DAC on Red Pitaya • Goal: • Review the ADC and DAC digital interfaces. • Understand the modifications to the Base Design to enable the ADC and DAC on the dev board. • Meeting timing. • Differences between 2017.2 and 2019.1. • These are things that can drive you crazy as a designer. • Testing. • The board specific code was obtained and modified from Red Pitaya Github and is intended for Vivado 2017.2.

ADC Data Interface

ADC Interface Could use different clock sources No access to SPI for configuration. • Data is latched in FPGA/HDL with always@(posedge ADCCLK) begin ADC_DA <= ADA; ADC_DB <= ADB; end

Timing Constraints _ _______________ _______________ ____________ DATA _X_______________X_______________X____________ |-------->| input delay _______ _______ ______ CLK _______/ \_______/ \_______/ • If (clock pad to CLK path) > (data pad to D + set_input_delay) then there is a timing violation.

Timing Constraints __ ____________ ____________ ________ DATA __XXXXX____________XXXXX____________XXXXX________ |------>| | input delay min | | |------------>| input delay max __ ________ ________ ____ CLK \_______/ \_______/ \_______/

ADC Timing • Based on the info here I would expect input delay to vary between 4 and 4.6 ns. • Actual value from board manufacturer is 3.4 ns.

ADC Clock Adjustments

ADC Constraints ### ADC # ADC data set_property IOSTANDARD LVCMOS18 [get_ports {adc_da_i[*]}] set_property IOB TRUE [get_ports {adc_da_i[*]}] set_property IOSTANDARD LVCMOS18 [get_ports {adc_db_i[*]}] set_property IOB TRUE [get_ports {adc_db_i[*]}] # ADC A data set_property PACKAGE_PIN Y17 [get_ports {adc_da_i[0]}] ... set_property PACKAGE_PIN V16 [get_ports {adc_da_i[13]}] # ADC B data set_property PACKAGE_PIN R18 [get_ports {adc_db_i[0]}] ... set_property PACKAGE_PIN Y18 [get_ports {adc_db_i[13]}] set_property IOSTANDARD DIFF_HSTL_I_18 [get_ports adc_clk_i[*]] set_property PACKAGE_PIN U18 [get_ports adc_clk_i[1]] set_property PACKAGE_PIN U19 [get_ports adc_clk_i[0]] # Output ADC clock set_property IOSTANDARD LVCMOS18 [get_ports {adc_clk_o[*]}] set_property SLEW FAST [get_ports {adc_clk_o[*]}] set_property DRIVE 8 [get_ports {adc_clk_o[*]}] #set_property IOB TRUE [get_ports {adc_clk_o[*]}] set_property PACKAGE_PIN N20 [get_ports {adc_clk_o[0]}] set_property PACKAGE_PIN P20 [get_ports {adc_clk_o[1]}] # ADC clock stabilizer set_property IOSTANDARD LVCMOS18 [get_ports adc_cdcs_o] set_property PACKAGE_PIN V18 [get_ports adc_cdcs_o] set_property SLEW FAST [get_ports adc_cdcs_o] set_property DRIVE 8 [get_ports adc_cdcs_o] create_clock -period 8.000 -name adc_clk [get_ports adc_clk_i[1]] set_input_delay -clock adc_clk 3.400 [get_ports adc_da_i[*]] set_input_delay -clock adc_clk 3.400 [get_ports adc_db_i[*]]

Data Format • Two’s complement is better for FPGA/DSP so need to convert. • Can’t access SPI on the ADC so this is done in HDL. //Verilog code //------------------------------------------------------------------// // ADC -------------------------------------------------------------// //------------------------------------------------------------------// wire adc_clk; IBUFDS i_clk (.I (adc_clk_i[1]), .IB (adc_clk_i[0]), .O (adc_clk)); assign adc_clk_o = 2'b10; // generating ADC clock is disabled assign adc_cdcs_o = 1'b1; //ADC clock duty cycle stabilizer is enabled //sync adc input data to adc_clk reg signed [13:0] adc_db_raw; reg signed [13:0] adc_da_raw; always@(posedge adc_clk) begin adc_db_raw <= {~adc_db_i[13], adc_db_i[12:0]}; //convert offset binary to signed (two's complement) adc_da_raw <= {~adc_da_i[13], adc_da_i[12:0]}; //convert offset binary to signed (two's complement) end //------------------------------------------------------------------//

Works in 18.1 but not 19.1? • Need to look at: • Timing Summary. • Implementation. Min Delay Paths -------------------------------------------------------------------------------------- Slack (VIOLATED) : -0.935ns (arrival time - required time) Source: adc_da_i[13] Destination: adc_da_raw_reg[13]/D • Bits [12:0] • Bit [13] • Delay is added • No violation

Work-Around //Verilog code //------------------------------------------------------------------// // ADC -------------------------------------------------------------// //------------------------------------------------------------------// wire adc_clk; IBUFDS i_clk (.I (adc_clk_i[1]), .IB (adc_clk_i[0]), .O (adc_clk)); assign adc_clk_o = 2'b10; // generating ADC clock is disabled assign adc_cdcs_o = 1'b1; //ADC clock duty cycle stabilizer is enabled //sync adc input data to adc_clk reg [13:0] adc_db_raw; reg [13:0] adc_da_raw; always@(posedge adc_clk) begin adc_db_raw <= adc_db_i; adc_da_raw <= adc_da_i; end wire signed [13:0] adc_db; wire signed [13:0] adc_da; assign adc_db = {~adc_db_raw[13], adc_db_raw[12:0]}; //convert offset binary to signed (two's comp) assign adc_da = {~adc_da_raw[13], adc_da_raw[12:0]}; //convert offset binary to signed (two's comp) //------------------------------------------------------------------//

DAC Data Interface

DAC Data Interface • Need 250 MHz to generate IQWRT and IOCLK. • Need 125 MHz to generate DATA_IN and IQ_SEL. • Use a PLL and ADC clk.

Constraints ### DAC # data set_property IOSTANDARD LVCMOS33 [get_ports {dac_dat_o[*]}] set_property SLEW SLOW [get_ports {dac_dat_o[*]}] set_property DRIVE 4 [get_ports {dac_dat_o[*]}] #set_property IOB TRUE [get_ports {dac_dat_o[*]}] set_property PACKAGE_PIN M19 [get_ports {dac_dat_o[0]}] set_property PACKAGE_PIN M20 [get_ports {dac_dat_o[1]}] set_property PACKAGE_PIN L19 [get_ports {dac_dat_o[2]}] set_property PACKAGE_PIN L20 [get_ports {dac_dat_o[3]}] set_property PACKAGE_PIN K19 [get_ports {dac_dat_o[4]}] set_property PACKAGE_PIN J19 [get_ports {dac_dat_o[5]}] set_property PACKAGE_PIN J20 [get_ports {dac_dat_o[6]}] set_property PACKAGE_PIN H20 [get_ports {dac_dat_o[7]}] set_property PACKAGE_PIN G19 [get_ports {dac_dat_o[8]}] set_property PACKAGE_PIN G20 [get_ports {dac_dat_o[9]}] set_property PACKAGE_PIN F19 [get_ports {dac_dat_o[10]}] set_property PACKAGE_PIN F20 [get_ports {dac_dat_o[11]}] set_property PACKAGE_PIN D20 [get_ports {dac_dat_o[12]}] set_property PACKAGE_PIN D19 [get_ports {dac_dat_o[13]}] # control set_property IOSTANDARD LVCMOS33 [get_ports dac_wrt_o] set_property SLEW FAST [get_ports dac_wrt_o] set_property DRIVE 8 [get_ports dac_wrt_o] set_property IOSTANDARD LVCMOS33 [get_ports dac_sel_o] set_property SLEW FAST [get_ports dac_sel_o] set_property DRIVE 8 [get_ports dac_sel_o] set_property IOSTANDARD LVCMOS33 [get_ports dac_clk_o] set_property SLEW FAST [get_ports dac_clk_o] set_property DRIVE 8 [get_ports dac_clk_o] set_property IOSTANDARD LVCMOS33 [get_ports dac_rst_o] set_property SLEW FAST [get_ports dac_rst_o] set_property DRIVE 8 [get_ports dac_rst_o] #set_property IOB TRUE [get_ports dac_*_o] set_property PACKAGE_PIN M17 [get_ports dac_wrt_o] set_property PACKAGE_PIN N16 [get_ports dac_sel_o] set_property PACKAGE_PIN M18 [get_ports dac_clk_o] set_property PACKAGE_PIN N15 [get_ports dac_rst_o]

DAC Data Interface • Need 250 MHz to generate IQWRT • IQCLK nees -45 degree phase offset for 500 ps. • Need 125 MHz to generate DATA_IN and IQ_SEL. • Use a PLL and ADC clk. • Use ODDR SelectIO Resourse to interleave signals.

PLL Instantiation PLLE2_ADV #( .BANDWIDTH ("OPTIMIZED"), .COMPENSATION ("ZHOLD" ), .DIVCLK_DIVIDE ( 1 ), //VCO is at 125 x 8 = 1000.00 MHz (between 600 and 1200 MHz) .CLKFBOUT_MULT ( 8 ), .CLKFBOUT_PHASE ( 0.000 ), .CLKOUT0_DIVIDE ( 8 ), pll ( .CLKOUT0_PHASE ( 180.000 ), // Output clocks .CLKOUT0_DUTY_CYCLE ( 0.5 ), .CLKFBOUT (clk_fb ), .CLKOUT1_DIVIDE ( 8 ), .CLKOUT0 (adc_clk ), .CLKOUT1_PHASE ( 180.000 ), .CLKOUT1 (dac_clk_1x), .CLKOUT1_DUTY_CYCLE ( 0.5 ), .CLKOUT2 (dac_clk_2x), .CLKOUT2_DIVIDE ( 4 ), .CLKOUT3 (dac_clk_2p), .CLKOUT2_PHASE ( 0.000 ), // Input clock control .CLKOUT2_DUTY_CYCLE ( 0.5 ), .CLKFBIN (clk_fb ), .CLKOUT3_DIVIDE ( 4 ), .CLKIN1 (clk125 ), .CLKOUT3_PHASE (-45.000 ), .CLKIN2 (1'b0 ), .CLKOUT3_DUTY_CYCLE ( 0.5 ), // Tied to always select the primary input clock .CLKOUT4_DIVIDE ( 4 ), // 4->250MHz .CLKINSEL (1'b1 ), .CLKOUT4_PHASE ( 0.000 ), // Ports for dynamic reconfiguration .CLKOUT4_DUTY_CYCLE ( 0.5 ), .DADDR (7'h0 ), .CLKOUT5_DIVIDE ( 4 ), .DCLK (1'b0 ), .CLKOUT5_PHASE ( 0.000 ), .DEN (1'b0 ), .CLKOUT5_DUTY_CYCLE ( 0.5 ), .DI (16'h0 ), .CLKIN1_PERIOD ( 8.000 ), .DO ( ), .REF_JITTER1 ( 0.010 )) .DRDY ( ), .DWE (1'b0 ), // Other control and status signals .PWRDWN (1’b0 ), .RST (~FRSTN ));

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.

![[LE,RO] red red red red red red red red red red red red red red red red red red](https://c.sambuz.com/407320/le-ro-s.webp)