Hybrid CLS-Opamp/ZCBC Pipelined ADC Using a 300mV Output Swing - PowerPoint PPT Presentation

A 1.4V Signal Swing Hybrid CLS-Opamp/ZCBC Pipelined ADC Using a 300mV Output Swing Opamp Benjamin Hershberg Skyler Weaver Un-Ku Moon Oregon State University, Corvallis, OR Preview 1. Background Correlated Level Shifting

A 1.4V Signal Swing Hybrid CLS-Opamp/ZCBC Pipelined ADC Using a 300mV Output Swing Opamp Benjamin Hershberg Skyler Weaver Un-Ku Moon Oregon State University, Corvallis, OR

Preview 1. Background • Correlated Level Shifting • Zero-Crossing Based Circuits 2. Hybrid CLS-Opamp/ZCBC Structure 3. Dynamic Zero-Crossing Detector 4. Measurement Results

Correlated Level Shifting (CLS) Ф A V o Ф S Ф 1 C CLS V i Ф 2 Ф 1 Ф S Ф A V CMI V CMO (+/-V r ,0) Ф S Ф A Ф 1 Ф 2 Finite opamp gain error becomes 1/A 2 Opamp output tied to different nodes in Φ 1 and Φ 2 Gregoire, ISSCC 2008

CLS – Basic Operation Ф A V o Ф S Ф 1 C CLS V i Ф 2 Ф 1 Ф S Ф A V CMO V CMI (+/-V r ,0) Ф 1 : Opamp Design Requirements opamp charges output Ф 1 Ф 2 directly Output Swing Large Small processes full signal Slew Rate Large Small

CLS – Basic Operation Ф A V o Ф S Ф 1 C CLS V i Ф 2 Ф 1 Ф S Ф A V CMO V CMI (+/-V r ,0) Ф 2 : Opamp Design Requirements opamp is level shifted to Ф 1 Ф 2 mid-rail Output Swing Large Small processes error only Slew Rate Large Small

Observation Use separate charging devices for Ф 1 and Ф 2 Optimized design for each phase • Increase overall accuracy & efficiency For this test chip: • Ф 1 : Zero-crossing based circuit (ZCBC) • Ф 2 : Double-cascoded Opamp Design Requirements telescopic opamp Ф 1 Ф 2 Output Swing Large Small Slew Rate Large Small

Ф 1 : Zero-crossing based circuit Charges output until input I src virtual ground condition is detected V x Ф PC V CM Slewing efficiency V CM V SS V CM Easy to turn off during Ф 2 ZCD No forced feedback overshoot V CM Linearity and reliability challenges V X Ф PC Sepke, ISSCC 2006

Ф 1 : Zero-crossing based circuit Charges output until input I src virtual ground condition is detected V x Ф PC V CM Slewing efficiency V CM V SS V CM Easy to turn off during Ф 2 ZCD No forced feedback overshoot V CM Linearity and reliability challenges Ф 1 : Fast, coarse charging V X Φ 2 : High accuracy feedback Ф PC Sepke, ISSCC 2006

Ф 2 : Telescopic Opamp V DD High Gain Low Swing V ctrl High Speed Low Slew V bp2 Low Power V bp3 V o - V o + V bn4 V bn3 V i + V i - V bn1 V SS

Ф 2 : Telescopic Opamp V DD High Gain Low Swing V ctrl High Speed Low Slew V bp2 Low Power V bp3 V o - V o + V bn4 Effective Gain 35dB (A Ф 1 ) V bn3 + 75dB (A Ф 2 ) V i + V i - 110 dB V bn1 V SS

Hybrid CLS-Opamp/ZCBC V SS V DD S PC V i+ (n+1) ( Ф PC ) I P Ф A V o+ Ф S V x+ V i+ Ф S Ф A Ф S +V ref V cm V CM -V ref Ф A Ф S Ф S V i- Ф S V x- Ф A V o- I N S PC V i- (n+1) ( Ф PC ) V DD V SS

Hybrid CLS-Opamp/ZCBC V SS V DD S PC V i+ (n+1) ( Ф PC ) I P Ф A V o+ Ф S V x+ V i+ Ф S D C Ф A Ф S +V ref V cm V CM -V ref Ф A Ф S Ф S V i- Ф S V x- Ф A V o- I N S PC V i- (n+1) ( Ф PC ) V DD V SS

Hybrid CLS-Opamp/ZCBC V SS V DD S PC V i+ (n+1) ( Ф PC ) I P Ф A V o+ Ф S C CLS V x+ V i+ Ф S D C Ф A Ф S +V ref V cm S OP V CM -V ref Ф A Ф S Ф S V CM S OP V i- Ф S V x- C CLS Ф A V o- I N S PC V i- (n+1) ( Ф PC ) V DD V SS

Hybrid CLS-Opamp/ZCBC V SS V DD S PC V i+ (n+1) ( Ф PC ) I P Ф A V o+ Ф S C CLS V x+ C DAC V i+ Ф S D C Ф A Ф S S DAC +V ref V cm V DD V SS S OP V CM -V ref Ф A Ф S Ф S S DAC V CM S OP V i- Ф S V x- C DAC C CLS Ф A V o- I N S PC V i- (n+1) ( Ф PC ) V DD V SS

V X- V SS V DD S PC V i+ (n+1) ( Ф PC ) I P V o+ Ф A V X+ Ф S C CLS V x+ C DAC Ф S V i+ D C Ф A Ф S S DAC +V ref V cm V DD V SS S OP V CM -V ref Ф A Ф S Ф S S DAC V CM S OP Ф S V i- C DAC V x- C CLS Ф A V o- I N S PC V i- (n+1) ( Ф PC ) Pre-charge switches closed V DD V SS ZCD & current sources begin to turn on Opamp output shorted to V CM C DAC set to track output

V X- V SS V DD S PC V i+ (n+1) ( Ф PC ) I P V o+ Ф A V X+ Ф S C CLS V x+ C DAC Ф S V i+ D C Ф A Ф S S DAC +V ref V cm V DD V SS S OP V CM -V ref Ф A Ф S Ф S S DAC V CM S OP Ф S V i- C DAC V x- C CLS Ф A V o- I N S PC V i- (n+1) ( Ф PC ) ZCBC coarse charging V DD V SS When ZCD trips: • turns off current sources • activates asynchronous timing block

V X- V SS V DD S PC V i+ (n+1) ( Ф PC ) I P V o+ Ф A V X+ Ф S C CLS V x+ C DAC Ф S V i+ D C Ф A Ф S S DAC +V ref V cm V DD V SS S OP V CM -V ref Ф A Ф S Ф S S DAC V CM S OP Ф S V i- C DAC V x- C CLS Ф A V o- I N S PC V i- (n+1) ( Ф PC ) V DD V SS Overshoot cancellation Δ V on bottom plate of C DAC cancels overshoot

V X- V SS V DD S PC V i+ (n+1) ( Ф PC ) I P Ф A V X+ Ф S C CLS V x+ Ф S V i+ D C Ф A Ф S +V ref V cm S OP V CM -V ref Ф A Ф S Ф S V CM S OP Ф S V i- V x- C CLS Ф A I N S PC V i- (n+1) ( Ф PC ) V DD V SS Opamp fine settling Shorting switch (S OP ) opens C DAC disconnects from output (minimize load)

Overshoot Cancellation V X- signal independent signal dependent V X+ Pure ZCBC: signal independent portion becomes DC offset Hybrid structure: opamp must cancel all overshoot

Overshoot Cancellation V X- Opamp virtual ground condition: Vx- = Vx+ V X+ Opamp will try to cancel all overshoot present

Overshoot Cancellation V X- opamp outputs V X+ No cancellation: opamp output saturates

Overshoot Cancellation V X- signal independent signal dependent V X+ A solution: cancel all predictable overshoot

Overshoot Cancellation V X- opamp outputs V X+ Opamp only processes signal dependent error

Overshoot Cancellation Charge cancellation DAC • Testability • No offset accumulation • Integrator compatible (e.g. ΔΣ ) Other possibilities to mitigate overshoot • ZCD input offset • Opamp input offset • Other DAC topologies

Dynamic ZCD V o - Voltage V i + V i - time t d Current (I tail ) time low g m ok need high g m Concept: redistribute current usage to maximize useful g m

Dynamic ZCD V DD Φ PC V o- V o+ I ref V i+ V i- Φ PC C FB M 1 M 3 V b I tail M 2 V SS

Dynamic ZCD V DD V o - Voltage V i + Input V i - V o- V o+ time off t d I ref V i+ V i- V o - Output Voltage Φ PC V b C FB M 1 M 3 V b time t d I tail off M 2 Current (I tail ) V SS I tail time t d Ф PC Step 1: Pre-charge

Dynamic ZCD V DD V o - Voltage V i + Input V i - V o- V o+ time off t d V i+ V i- V o - Output Voltage V b C FB M 1 V b time t d I tail off M 2 Current (I tail ) V SS I tail time t d A ZCD (V i+ - V i- ) > (V o+ - V o- ) Step 2: Power conservation

Dynamic ZCD V DD V o - Voltage V i + Input V i - V o- V o+ time off t d V i+ V i- V o - Output Voltage V b C FB M 1 V b time t d I tail off M 2 Current (I tail ) V SS I tail time t d A ZCD (V i+ - V i- ) < (V o+ - V o- ) Step 3: High g m

Dynamic ZCD V DD V o - Voltage V i + Input V i - V o- V o+ time off t d V i+ V i- V o - Output Voltage V b C FB M 1 V b time t d I tail =0 off M 2 Current (I tail ) V SS I tail time t d Step 4: Shutdown

Dynamic ZCD Strongly correlated design variables • A ZCD • C FB • I SRC /C LOAD Best choice dependent on specific design targets

ZCD Variation Tolerance In test, I ref varied from 6.5uA - 50uA with no impact on performance • Only limited by tuning range of test board • Current bias, voltage bias, or self-bias feasible Higher g m at critical instant can suppress certain internal and external variations Floating bias • Blocks certain transient effects • Vulnerable to others

ZCD Power Efficiency Your mileage will vary Depends on design specifications • Converter accuracy • ZCD time delay • Current source slew rate For this test ADC: simulation shows 4x improvement over state of the art ( Brooks, ISSCC 2009 ) In general, the slower the ramp, the more dramatic the savings

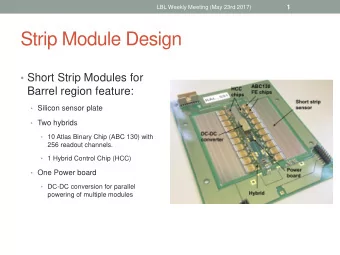

Chip Micrograph 10 identical 1.5b stages 1.5b backend flash

Measured Results

Measured Results SNDR vs. Fin 75 70 dB 65 60 -1 0 10 10 Fin / Fs f nyquist

Measured Results

Key Benefits Accuracy - Extremely high effective gain, even in modern processes. Robustness - Relax ZCBC design by adding linear feedback. Efficiency - Amplification devices optimized for unique requirements. Efficient charging with ZCBC. High gain, single stage opamp w/o gain boosting amplifiers or compensation.

Acknowledgements This work was funded by the Semiconductor Research Corporation and the Center for Design of Analog-Digital Integrated Circuits. The authors would like to thank TowerJazz Semiconductor for providing fabrication. Additional thanks to Peter Kurahashi, Sasidhar Lingam, Phil Crosby, Arnie Frisch, Ed Hershberg, Dianne Glenn and members of the OSU AMS lab for their valuable contributions and insight.

Additional Materials

DNL DIFFERENTIAL NONLINEARITY vs. DIGITAL OUTPUT CODE 0.5 DNL (LSB) 0 -0.5 0 256 512 768 1024 1280 1536 1792 2048 DIGITAL OUTPUT CODE

INL INTEGRAL NONLINEARITY vs. DIGITAL OUTPUT CODE 3 2 1 INL(LSB) 0 -1 -2 -3 0 256 512 768 1024 1280 1536 1792 2048 DIGITAL OUTPUT CODE

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.

![Fast op. amp. [Renesas EL5104, Analog Devices AD9631-2] Fast opamp The EL5104, EL5105,](https://c.sambuz.com/1064204/fast-op-amp-s.webp)