1 What an odd little circuit Bistable latches o Memories Q Q o - PDF document

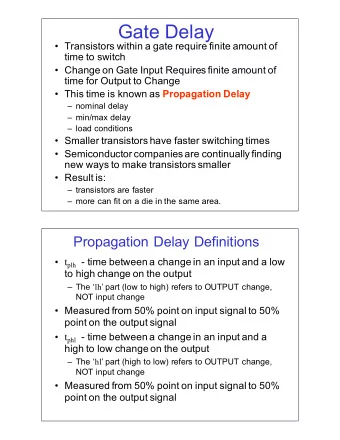

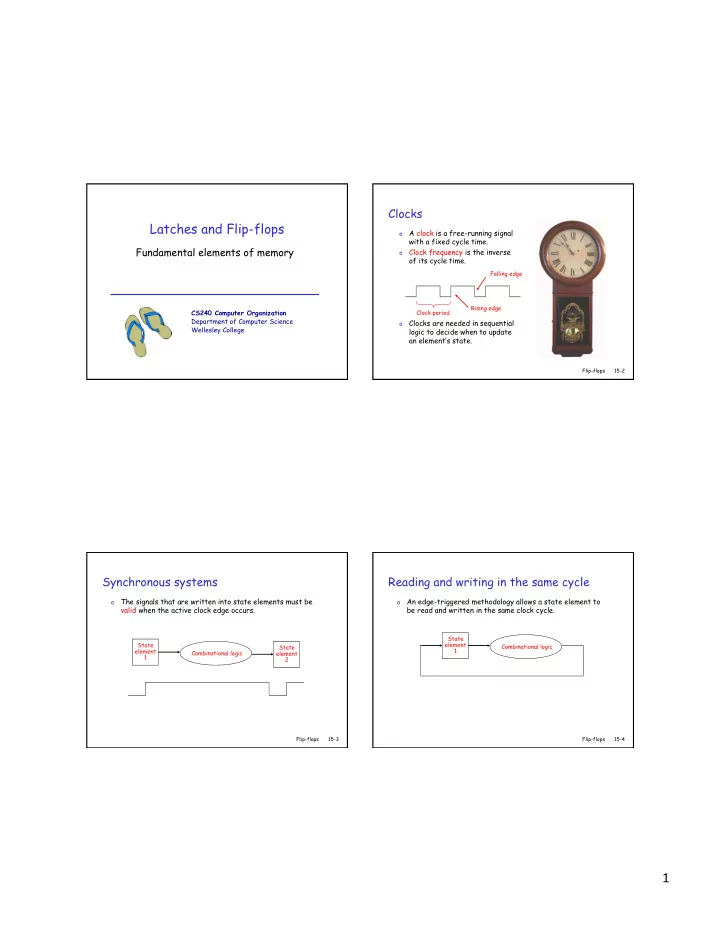

Clocks Latches and Flip-flops o A clock is a free-running signal with a fixed cycle time. Fundamental elements of memory o Clock frequency is the inverse of its cycle time. Falling edge Rising edge CS240 Computer Organization Clock period

Clocks Latches and Flip-flops o A clock is a free-running signal with a fixed cycle time. Fundamental elements of memory o Clock frequency is the inverse of its cycle time. Falling edge Rising edge CS240 Computer Organization Clock period Department of Computer Science o Clocks are needed in sequential Wellesley College logic to decide when to update an element’s state. Flip-flops 15-2 Synchronous systems Reading and writing in the same cycle o The signals that are written into state elements must be o An edge-triggered methodology allows a state element to valid when the active clock edge occurs. be read and written in the same clock cycle. State State element State Combinational logic 1 element Combinational logic element 1 2 Flip-flops 15-3 Flip-flops 15-4 1 ¡

What an odd little circuit Bistable latches o Memories Q Q o New memories S R Q Q Flip-flops 15-5 Flip-flops 15-6 Redrawing the SR latch A D latch o New o When the clock is unasserted, the cross-coupled pair of R NOR gates acts to store the state value. Q R C Q Q o Old S S Q D S R Q Q o When the clock goes high, the Q value tracks the value of D. Flip-flops 15-7 Flip-flops 15-8 2 ¡

A D flip-flop with a falling-edge trigger One D Flip-Flop* = One Bit E D D Q D Q Q D D 1 D Q D latch latch Flip-Flop Q Q C C C Q C *Block diagram. Flip-flops 15-9 Flip-flops 15-10 Dual D flip-flop One Nibble* 0 D Q D Flip-Flop C Q 1 D Q D Flip-Flop C Q 0 D Q D Flip-Flop C Q 1 D Q D Flip-Flop Write C Q Clock *Half a byte! Flip-flops 15-11 Flip-flops 15-12 3 ¡

Register files Implementation of two read ports o A register file consists of a set of registers that can be read and written by supplying a register number. o Register files with two read ports will be important later in the semester when we build our MIPS machine. Flip-flops 15-13 Flip-flops 15-14 Implementation of write port Synthesis of sequential circuits o The output of combinational circuits depends only on their current input. o Sequential circuits “selectively” remember past events. o They speak of such circuits as having state and model them with finite automata. Flip-flops 15-15 Flip-flops 15-16 4 ¡

Identify the required internal states* Identify the required internal states* inside outside signal signal 10 00 01 Closed Open 01 Closed Open 10 11 11 00 *And use input signals to generate transition diagram. *And use input signals to generate transition diagram. Flip-flops 15-17 Flip-flops 15-18 Determine required memory* Select flip-flops and develop control levels State code Out In Out In Out In Out In Outside 0 0 0 1 1 0 1 1 Output signal Closed 0 0 0 1 0 D Q Inside D Flip-flop Open 1 1 1 1 0 Q C *Assign codes to states and produce state and output tables. Flip-flops 15-19 Flip-flops 15-20 5 ¡

Develop control level table(s) Develop Boolean expression for D State Out In D State Out In D 0 0 0 0 0 0 0 0 0 0 1 0 0 0 1 0 0 1 0 1 0 1 0 1 0 1 1 0 0 1 1 0 1 0 0 0 1 0 0 0 1 0 1 1 1 0 1 1 1 1 0 1 1 1 0 1 1 1 1 1 1 1 1 1 D = State’ • Out • In’ + State • Out’ • In + State • Out • In’ + State • Out • In *These are the inputs to the flip-flops that make them behave according to the transition diagram and table. Flip-flops 15-21 Flip-flops 15-22 Implement circuit Outside Inside D Q D Output signal Flip-flop Q C Flip-flops 15-23 6 ¡

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.