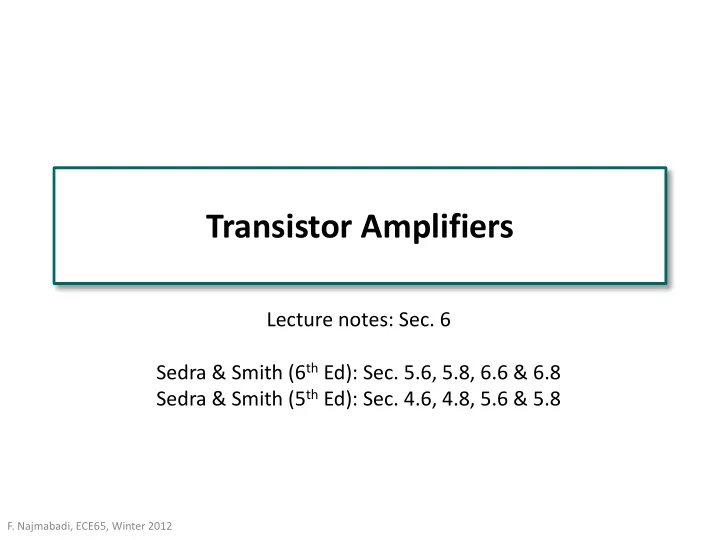

Transistor Amplifiers Lecture notes: Sec. 6 Sedra & Smith (6 th - PowerPoint PPT Presentation

Transistor Amplifiers Lecture notes: Sec. 6 Sedra & Smith (6 th Ed): Sec. 5.6, 5.8, 6.6 & 6.8 Sedra & Smith (5 th Ed): Sec. 4.6, 4.8, 5.6 & 5.8 F. Najmabadi, ECE65, Winter 2012 How to add signal to the bias Bias & Signal

Transistor Amplifiers Lecture notes: Sec. 6 Sedra & Smith (6 th Ed): Sec. 5.6, 5.8, 6.6 & 6.8 Sedra & Smith (5 th Ed): Sec. 4.6, 4.8, 5.6 & 5.8 F. Najmabadi, ECE65, Winter 2012

How to add signal to the bias Bias & Signal Bias & Signal v GS = V GS + v gs v DS = V DS + v ds 1. Direct Coupling 2. Capacitive Coupling Use bias with 2 voltage supplies o For the first stage, bias such that Use a capacitor to separate bias V GS = 0 voltage from the signal. o For follow-up stages, match bias Simplified biasing problem. voltages between stages Used in discrete circuits Difficult biasing problem Only amplifies “AC” signals Used in ICs Amplifies “DC” signals! F. Najmabadi, ECE65, Winter 2012

Capacitive coupling is based on the fact that capacitors appear as open circuit in bias Real Circuit Bias Circuit Signal Circuit At a high enough frequency, Z c = 1/ ( ω C ) , becomes small (effectively, capacitors become short circuit). Mid-band parameters of an Amplifier.* o At low frequencies, Z c cannot be ignored. As Z c depends on frequency, amplifier is NOT linear (for an arbitrary signal) for these low frequencies. Capacitors introduce a lower cut-off frequency for an amplifier (i.e., amplifier o should be operated above this frequency). F. Najmabadi, ECE65, Winter 2012 In ECE102, you will see that transistor amplifiers also have an “upper” cut-off frequency

What are amplifier parameters? v A = o Voltage Gain : v v i v = Open - loop Gain : o A vo v → ∞ i R L v R = Input Resistance : i i i i v = Output Resistance of Amplifier : o R o i → o 0 v i v = o Output Resistance of the circuit : R out i → o 0 v sig Output resistance is the Thevenin resistance between the output terminals! F. Najmabadi, ECE65, Winter 2012

Observations on the amplifier parameters Overall Gain : v v v R = = × = o i o i A A + v v v v R R sig sig i i sig v R v R = = = i i o L A A + + v vo v R R v R R sig i sig i L o A vo is the maximum possible gain Value of R i is important. of the amplifier. o For R sig << R i , v i ≈ v sig Value of R o is important. o For R sig = R i , v i = 0.5 v sig o For R o << R L , A v ≈ A vo o For R sig >> R i , v i ≈ 0 o For R o = R L , A v = 0.5 A vo Prefer “large” R i o For R o >> R L , A v ≈ 0 Prefer “small” R o F. Najmabadi, ECE65, Winter 2012

How to Solve Amplifier Circuits 1. Find Bias and Signal Circuits. 2. Bias circuit (signal = 0): o Capacitors are open circuit. o Use transistor large-signal model to find the bias point. o Use bias parameters to find small-signal parameters ( r π , g m , r o ). 3. Signal Circuit (IVS becomes short, ICS becomes open circuit): o Assume capacitors are short to find mid-band amplifier parameters. o Replace diodes and/or transistors with their small-signal model. o Solve for mid-band amplifier parameters ( A v , R i , R o ). • For most circuits, we can use fundamental amplifier configurations, elementary R forms instead of solving signal circuits. o Include impedance of capacitors to find the lower cut-off frequency of the amplifier. F. Najmabadi, ECE65, Winter 2012

Example 1: Draw the small-signal equivalent of the circuit below (assume capacitors are short for small signal). IVS → 0 R remains Caps short Ground at the bottom Replace MOS with its small signal model F. Najmabadi, ECE65, Winter 2012

Example 2: Draw the small-signal equivalent of the circuit below (assume capacitors are short for small signal). IVS → 0 Caps short Ground at the bottom (100k || 33k = 24.8 k) Flip PMOS Replace MOS with its small signal model F. Najmabadi, ECE65, Winter 2012

Example 3: Draw the small-signal equivalent of the circuit below (assume capacitors are short for small signal). IVS → 0 Caps short ICS → 0 (This makes ICS an open circuit) Replace MOS with its small signal model F. Najmabadi, ECE65, Winter 2012

Basic MOS Amplifier Configurations We are considering only signal circuit here! F. Najmabadi, ECE65, Winter 2012

Possible MOS amplifier configurations Common-Gate Common-Source Common-Drain Same as Common Gate Common-Source with R s (v i does not change) Not Useful F. Najmabadi, ECE65, Winter 2012

PMOS configurations are the same as those of NMOS Common-Source Common-Gate Common-Drain Since PMOS has the same signal model, configurations and results are exactly the same F. Najmabadi, ECE65, Winter 2012

Common Source Configuration (Gain) Signal Circuit: ′ = − ( || ) v g v r R o m gs o L v ′ = = − o ( || ) A g r R v m o L v i = − A g r vo m o Signal Circuit with Relevant circuit for MOS SSM: Gain calculation By KCL F. Najmabadi, ECE65, Winter 2012

Common Source Configuration ( R i ) Signal Circuit with MOS SSM: Relevant circuit for R i calculation = 0 i i v = = ∞ i R i i i F. Najmabadi, ECE65, Winter 2012

Common Source Configuration ( R o ) Signal Circuit with MOS SSM: Relevant circuit for R o calculation (set v i = 0 ) Current source becomes open circuit R = r o o F. Najmabadi, ECE65, Winter 2012

Common Source with Source Resistor Small Signal Circuit: Signal Circuit with MOS SSM: v = ⇒ = = ∞ Input Resistance i 0 i R i i i i F. Najmabadi, ECE65, Winter 2012

Common Source with Source Resistor (Gain) Relevant circuit for Gain calculation Node voltage method : = − ′ v v v v g r R gs i S = = − o m o L A − ′ + + + v v v v ( 1 ) v r g r R R Node v S + − − = S S o ( ) 0 g v v i o m o S L m i S ′ R r g R S o ≈ − m L A − ′ + + v v v v 1 / g R R r Node v o + + − = o o S ( ) 0 g v v m S L o ′ m i S = − R r A g r L o vo m o F. Najmabadi, ECE65, Winter 2012

Common Source with Source Resistor (R o ) set v i = 0 Attach v x and compute i x R o = v x /i x Node voltage method: = − v v gs S − v v v Node v S + − − = S S x ( ) 0 g v m S R r S o v v = S x 1 1 i ≡ = + + x ( 1 ) R r g r R + + S o m o S ( 1 ) R v r g r R o x o m o S v v = = S x i + ( + x 1 ) R r g r R = + + S o m o S ( 1 ) R r g r R o o m o S F. Najmabadi, ECE65, Winter 2012

Common Gate Configuration Gain Node voltage method: = − v v gs i − v v v + + − = Node v o o o i ( ) 0 g v ′ m i R r L o + 1 v g r = o m o v ′ i || r R r o L o + 1 v g r ′ = = o m o ( || ) A r R v o L v r i o ′ ≈ ( || ) A g r R v m o L ≈ A g r vo m o F. Najmabadi, ECE65, Winter 2012

Common Gate Configuration ( R i and R o ) Input Resistance ′ = + + ( ) KVL: v i g v r i R i i m gs o i L ′ + = + ( 1 ) ( ) v g r i r R i m o i o L ′ + v r R = = i o L R + i 1 i g r i m o ′ 1 R ≈ + L R i g g r m m o Output Resistance (set v i = 0 ) Current source becomes open circuit R = r o o F. Najmabadi, ECE65, Winter 2012

Common Drain Configuration (Source Follower) Gain Node voltage method: = − v v v gs i o v v + − − = Node v o o o ( ) 0 g v v ′ m i o R r L o v = + o g v g v ′ m i m o || r R o L ′ ( || ) g r R = m o L A ′ + v 1 ( || ) g r R m o L g r = ≈ m o 1 A + vo 1 g r m o F. Najmabadi, ECE65, Winter 2012

Common Drain Configuration (Source Follower) Input Resistance = 0 i i v = = ∞ i R i i i Output Resistance (set v i = 0 ) v v v = − = + x x x i g v x m gs 1 / r r g o o m 1 1 = ≈ || R r o o g g m m F. Najmabadi, ECE65, Winter 2012

MOS Basic Amplifier Configurations (PMOS circuits are identical) Common Source Common Gate ′ = − ′ = ( || ) A g r R ( || ) A g r R v m o L v m o L Common Drain/Source Follower Common Source with RS ′ ′ g R ( || ) g r R = − m L = A m o L A ′ + + v ′ 1 / + g R R r v 1 ( || ) g r R m S L o m o L F. Najmabadi, ECE65, Winter 2012

MOS Elementary R forms

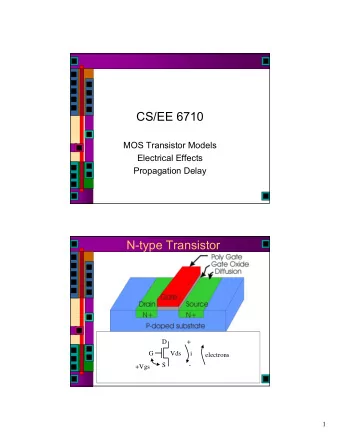

A Transistor can be configured to act as a resistor for small signals! Ex: Output resistance of a CS Amplifier r o Notation: Set v i = 0 , current source becomes open circuit r o is the small-signal resistance R = r between the point and ground o o If we connect any two terminals of a MOS, we get a two-terminal device. o For Small Signals, this two terminal device can be replaced with its Thevenin equivalent circuit. o As there is NO independent sources present, the Thevenin equivalent circuit is reduced to a resistor. F. Najmabadi, ECE65, Winter 2012

Transistor can be configured to act as a resistor for small signals! But, MOS should be in saturation for small signal model to work! o Connection between MOS terminals are, therefore, made through ground for small signals. o In fact, one or both MOS terminals have to be connected to bias power supplies to ensure that MOS is in saturation Real Circuit Small Signal Circuit A) B) No Small Signal circuit MOS is NOT in saturation F. Najmabadi, ECE65, Winter 2012

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.

![Transistor Channel Model [Farquhar and Hasler, 2004] Transistor HH Channel Model [Farquhar and](https://c.sambuz.com/897541/transistor-channel-model-s.webp)