Testbench - -- interface entity reg32 is port (CLK, rst_n, load : in - PowerPoint PPT Presentation

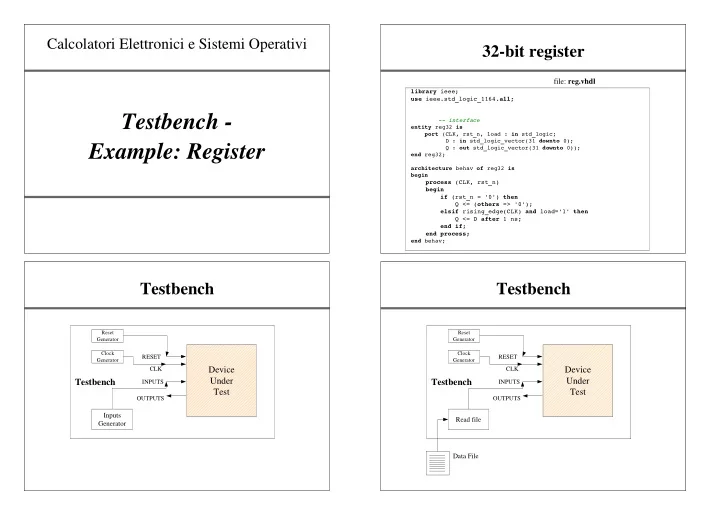

Calcolatori Elettronici e Sistemi Operativi 32-bit register file: reg.vhdl library ieee; use ieee.std_logic_1164. all ; Testbench - -- interface entity reg32 is port (CLK, rst_n, load : in std_logic; D : in std_logic_vector(31 downto 0);

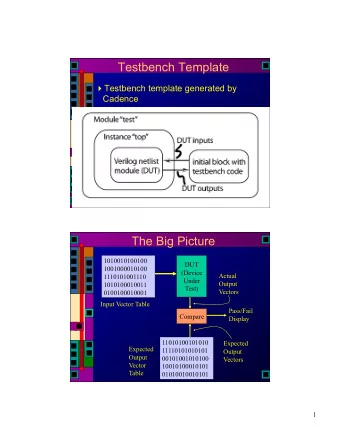

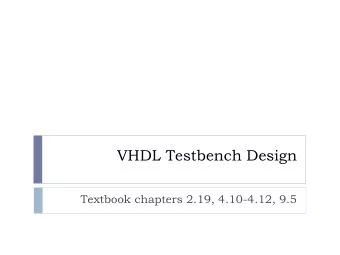

Calcolatori Elettronici e Sistemi Operativi 32-bit register file: reg.vhdl library ieee; use ieee.std_logic_1164. all ; Testbench - -- interface entity reg32 is port (CLK, rst_n, load : in std_logic; D : in std_logic_vector(31 downto 0); Example: Register Q : out std_logic_vector(31 downto 0)); end reg32; architecture behav of reg32 is begin process (CLK, rst_n) begin if (rst_n = '0') then Q <= ( others => '0'); elsif rising_edge(CLK) and load='1' then Q <= D after 1 ns; end if ; end process; end behav; Testbench Testbench Reset Reset Generator Generator Clock Clock RESET RESET Generator Generator CLK Device CLK Device Under Under Testbench Testbench INPUTS INPUTS Test Test OUTPUTS OUTPUTS Inputs Read file Generator Data File

Testbench for 32-bit register: Data File Testbench for 32-bit register file: data.txt file: TB.vhdl 10111001010101111101000100001011 library ieee; 1 use ieee.std_logic_1164. all ; use ieee.numeric_std. all ; 01101011101001101100110000001110 use STD.textio. all ; 1 01111001110110100110010111110101 -- interface 1 entity TB is end TB; 10011011010100000100100011110100 0 -- architecture architecture behav of TB is 11010011110111101011110010101000 0 constant CLK_SEMIPERIOD0: time := 25 ns; constant CLK_SEMIPERIOD1: time := 15 ns; 00111100100110011100111110100101 constant CLK_PERIOD : time := CLK_SEMIPERIOD0+CLK_SEMIPERIOD1; 1 constant RESET_TIME : time := 3*CLK_PERIOD + 9 ns; ... ... Testbench for 32-bit register Testbench for 32-bit register file: TB.vhdl file: TB.vhdl signal CLK, rst_n : std_logic ; -- DUT declaration component reg32 is port ( -- signals for debugging and tb control signal count : std_logic_vector (23 downto 0) := CLK, rst_n, load : in std_logic ; (others=> '0'); D : in std_logic_vector (31 downto 0); signal int_count : integer := 0; Q : out std_logic_vector (31 downto 0) signal start : integer := 0; ); signal done : integer := 0; end component; signal counter_data : std_logic_vector (23 downto 0) := ( others => '0'); signal int_counter_data : integer := 0; -- TB architecture definition begin -- DUT instance -- signals for DUT (Device Under Test) DUT : reg32 signal load : std_logic := '0'; port map ( signal D : std_logic_vector (31 downto 0); CLK => CLK, rst_n => rst_n, signal Q : std_logic_vector (31 downto 0); load => load, D => D, Q => Q );

Testbench for 32-bit register Testbench for 32-bit register file: TB.vhdl file: TB.vhdl -- read from datafile read_file_process: process (clk) -- RESET file infile : TEXT open READ_MODE is "data.txt"; start_process: process variable inputline : LINE; begin 1 ns RESET_TIME variable in_D : bit_vector (D'range); rst_n <= '1'; variable in_load : bit ; wait for 1 ns; begin rst_n <= '0'; if (clk='0') and (start = 1) then data updated on the falling edge wait for RESET_TIME; -- read new data from file rst_n <= '1'; D input for DUT if not endfile(infile) then start <= 1; readline(infile, inputline); wait; read(inputline, in_D); D <= to_UX01(in_D); load input for DUT end process start_process; readline(infile, inputline); read(inputline, in_load); load <= to_UX01(in_load); used to start reading from datafile readline(infile, inputline); -- separator (empty line) counter_data <= std_logic_vector(unsigned(counter_data) + 1); int_counter_data <= int_counter_data + 1; else done <= 1; end if ; end if ; used to keep track of data read end process read_file_process; Testbench for 32-bit register (v1) Testbench for 32-bit register (v1) file: TB.vhdl file: TB.vhdl -- terminate the simulation when there are no more data in datafile -- CLOCK generator done_process: process (done) clk_process: process variable outputline : LINE; begin begin if CLK = '0' then if (done=1) then CLK <= '1'; write(outputline, string'("End simulation - ")); wait for CLK_SEMIPERIOD1; write(outputline, string'("cycle counter is ")); else write(outputline, int_count); CLK <= '0'; writeline(output, outputline); wait for CLK_SEMIPERIOD0; assert false count <= std_logic_vector(unsigned(count) + 1); report "NONE. End of simulation." int_count <= int_count + 1; severity failure ; end if ; end if ; end process clk_process; end process done_process; CLK_SEMIPERIOD0 end behav ; CLK_SEMIPERIOD1 used to keep track of clock cycles

Testbench for 32-bit register (v2) 32-bit register: simulation results (v1) file: TB.vhdl End simulation - cycle counter is 22 End simulation - cycle counter is 22 TB.vhdl:110:13:(assertion failure): NONE. End of simulation. TB.vhdl:110:13:(assertion failure): NONE. End of simulation. ./tb:error: assertion failed ./tb:error: assertion failed -- CLOCK generator clk_process: process simulation output begin if CLK = '0' then CLK <= '1'; wait for CLK_SEMIPERIOD1; else Waveforms CLK <= '0'; wait for CLK_SEMIPERIOD0; count <= std_logic_vector(unsigned(count) + 1); int_count <= int_count + 1; end if ; if done = 1 then wait ; end if ; end process clk_process; No more events will be generated (simulation terminates) Calcolatori Elettronici e Sistemi Operativi Exercises Implement and simulate (using a testbench): Exercise: Combinatorial logic Multiplexer, shifter, adder Ones counter Double sequence recognizer Detect seq1 =1011011 and seq2 =10101

Ones counter Ones counter 8 8 ASM chart X OUTP ctrlunit DATAIN onescounter READY datapath CALC OK toplevel testbench OUTP: total number of bits equal to '1' received on X DATAIN=1 � signals a new input data CALC=1 � signals that input data are finished: provide result READY=1 � the device is ready to receive a new data OK=1 � the device finished the computation the result on OUTP is ready and valid a new computation can start INIT READY OK Ones counter A <= X X 1 0 CALC selA 8 A loadA ctrlunit 1 0 LSB_A 8 DATAIN rsl =0 interface START ONES <= 0 8 A <= A>>1 clk, reset, zA 0 0 WAITDATA 1 control signals from extern A(0) READY A <= X selONES scan the asm chart to find status signals 8 INC SHIFT FSM evolution ( � ) ONES loadONES ONES <= ONES+1 A <= A>>1 1 0 A <= A>>1 CALC 1 8 OUTP use also “ when others ” + 0 1 find control signals for datapath ( � ) 0 1 A=0 8 DATAIN CALC_A write outputs expression 0 1 A <= A>>1 A=0 0 do not forget any “ else ” 1 A(0) complete the interface 0 1 INC 0 LSB_A A(0) SHIFT 1 A(0) LSB_A

Ones counter: ctrlunit Ones counter: ctrlunit file: ctrlunit.vhdl file: ctrlunit.vhdl library ieee; architecture behav of ctrlunit is use ieee.std_logic_1164. all ; type statetype is (INIT, START, INC, SHIFT, CALC_A, WAITDATA); signal state, nextstate : statetype ; begin -- interface -- FSM entity ctrlunit is state <= INIT when rst_n='0' else port ( nextstate when rising_edge(CLK); CLK, rst_n : in std_logic ; -- control inputs process (state, DATAIN, CALC, LSB_A, zA) DATAIN : in std_logic ; begin CALC : in std_logic ; -- control outputs case state is READY : out std_logic ; when INIT => OK : out std_logic ; if CALC /= '0' then loadA : out std_logic ; nextstate <= INIT; selA : out std_logic ; elsif DATAIN /= '1' then loadONES : out std_logic ; nextstate <= INIT; selONES : out std_logic ; else -- status signals nextstate <= START; LSB_A : in std_logic ; end if ; zA : in std_logic ); end ctrlunit; Ones counter: ctrlunit Ones counter: ctrlunit file: ctrlunit.vhdl file: ctrlunit.vhdl when START => when CALC_A => if LSB_A = '0' then if LSB_A = '0' then nextstate <= SHIFT; nextstate <= SHIFT; else else nextstate <= INC; nextstate <= INC; end if ; end if ; when INC => when WAITDATA => if zA = '1' then if CALC = '1' then nextstate <= WAITDATA; nextstate <= INIT; elsif LSB_A = '1' then elsif DATAIN = '0' then nextstate <= INC; nextstate <= WAITDATA; else else nextstate <= SHIFT; nextstate <= CALC_A; end if ; end if ; when SHIFT => when others => if zA = '1' then nextstate <= INIT; nextstate <= WAITDATA; end case; elsif LSB_A = '1' then end process; nextstate <= INC; else nextstate <= SHIFT; end if ;

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.