Design and Verilog Module Creating a design and implementing in FPGA - PowerPoint PPT Presentation

Design and Verilog Module Creating a design and implementing in FPGA Design Verilog (mainly) Schematic(sometimes) Verify Need writing a testbench Simulation using ISIM Creating a design and implementing in FPGA Add User

Design and Verilog Module

Creating a design and implementing in FPGA • Design • Verilog (mainly) • Schematic(sometimes) • Verify • Need writing a testbench • Simulation using ISIM

Creating a design and implementing in FPGA • Add User constraints File (xdc) • Define the pin locations of FPGA • Ex: Clk, reset, LED, switches, VGA pins • Later: Add timing constraints • Put pin locations • Generate programming files

Note • When copying the verilog from the website, some extra spaces between the variables will appear. You will need to delete them when you see the errors

Design Metrics • These are the key design metrics that must be met when designing any device • Function • Performance • Area • Energy • Design time • These metrics have become more critical

Design Metrics • In less than 20 years, the size of cellphones have reduced. However a lot more applications and features such as video web application, phone application in addition to the voice • The key challenge is design these components in order to meet the real time performance and area footprint within a limited power budget

Logic Design • Basic digital components for logical design: • Combinational Logic • Output value is determined by combining input values at that time • Ex: • AND • OR • Inverter • Multiplexer

Logic Design • Sequential Logic • The output value depends on current and previous values and/or time sequence • Ex: Flip flop, state machines it can remember a single bit of information which can change based on the time

Board Description • The main FPGA on board • Artix-7 100T • 4,860 Kbit Block RAM • 15,850 logic cells (each with 6 input LUTs and 8 Flipflops) • 240 DSP slices • Max clk 450 MHz • Board features • 16 user switches • 16 user LEDs • Two 4-digit 7-segment displays • USB-UART Bridge • Two tri-color LEDs • Micro SD card connector

Board Description-Contd. • 12-bit VGA output • PWM audio output PDM microphone • 3-axis accelerometer • Temperature sensor • 10/100 Ethernet PHY • 128MiB DDR2 • Serial Flash Four Pmod ports • Digilent USB-JTAG port for FPGA programming and communication • USB HID Host for mice, keyboards and memory sticks

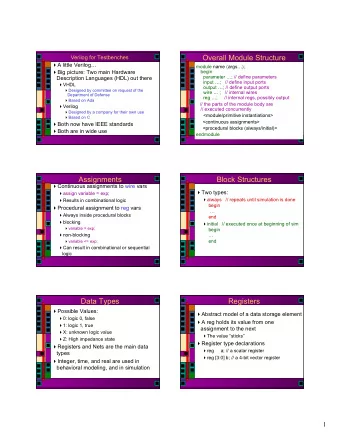

Verilog Module • Verilog model consists of • Module definition describing the inputs and outputs of the circuit and the implementation of the circuit • Ports declaration: • Input or output • Size

Verilog Module-Contd. • Net declaration • Wire: assignment statements • Reg: always blocks • Size (number of bits) • Behavioral description • Assignment statements • Always statements

Example 1 c 4 + sum 5 d 4 Assign sum=

Example 2 module top(in1,in2,d,sum, clk); nput [2:0] in1,in2; top Input [3:0] d; Input clk; + + Output [4:0] sum; c sum + reg [3:0] a; 5 wire[3:0] c; assign c = {in1[2],in1} +{in2[2],in2}; a d assign sum ={c[3],c} +{a[3],a}; //If we were extending for 2 bits //assign sum ={c[3],c[3],c} +{a[3],a[3],a}; clk //assign sum={2{c[3]}} ,c }+ {2{a[3]}} ,a}; ` always@(posedge clk) a<=d; endmodule

Example 2 module top(in1,in2,d,sum, clk); top Input signed [2:0] in1,in2; Input signed [3:0] d; + + Input clk; c Output signed [4:0] sum; sum + 5 reg signed [3:0] a; wire signed[3:0] c; a d assign c = in1 + in2; assign sum = c + a; always@(posedge clk) clk a <= d; ` endmodule

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.

![Problem 1 Design a Verilog 16-bit adder module module adder (A, B, sum); input [15:0] A, B;](https://c.sambuz.com/1025319/problem-1-design-a-verilog-16-bit-adder-module-module-s.webp)