SoC SoC Design Design g Lecture L Lecture 3: Introduction to - PowerPoint PPT Presentation

SoC SoC Design Design g Lecture L Lecture 3: Introduction to ASICs 3 I : Introduction to ASICs I d d i i ASIC ASIC Shaahin Hessabi Shaahin Hessabi Department of Computer Engineering Department of Computer Engineering Sharif

SoC SoC Design Design g Lecture L Lecture 3: Introduction to ASICs 3 I : Introduction to ASICs I d d i i ASIC ASIC Shaahin Hessabi Shaahin Hessabi Department of Computer Engineering Department of Computer Engineering Sharif University of Technology Sharif University of Technology

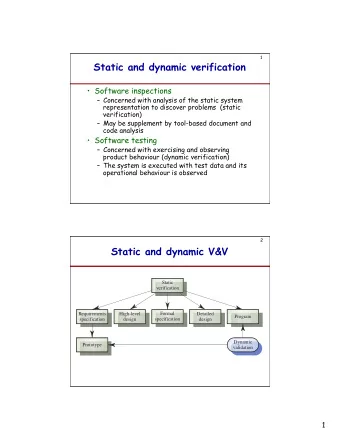

IC Technology IC Technology � The term The term ASIC ASIC is often reserved for is often reserved for circuits that are fabricated in a silicon circuits that are fabricated in a silicon circuits that are fabricated in a silicon circuits that are fabricated in a silicon foundry, while circuits that can be foundry, while circuits that can be programmed at the customer s site programmed at the customer’s site programmed at the customer s site programmed at the customer’s site are called Programmable Logic. are called Programmable Logic. � The term The term full custom full custom is reserved for is reserved for circuits where all silicon layers can circuits where all silicon layers can be optimized. This implies a long be optimized. This implies a long d d design process and thus full custom design process and thus full custom i i d th d th f ll f ll t t is mainly used for high is mainly used for high- -volume high volume high- - end circuits end circuits end circuits. end circuits. Sharif University of Technology Introduction to ASICs Page 2

What is an ASIC? What is an ASIC? � An ASIC (Application Specific Integrated Circuit) is an An ASIC (Application Specific Integrated Circuit) is an integrated circuit for a specific application and (generally) integrated circuit for a specific application and (generally) integrated circuit for a specific application and (generally) integrated circuit for a specific application and (generally) produced in relatively small volumes (batches of produced in relatively small volumes (batches of 10 10 to to 10000 units). 10000 10000 units). 10000 units). units). � A typical ASIC is a circuit, where functions are designed A typical ASIC is a circuit, where functions are designed by the customer, and layout and the fabrication is done by the customer, and layout and the fabrication is done y y , , y y by the silicon vendor. by the silicon vendor. � An ASIC technology helps to shorten the design time by An ASIC technology helps to shorten the design time by providing a semi providing a semi- -fabricated integrated circuit. fabricated integrated circuit. � Not ASICs: General Not ASICs: General- -purpose processors, memory chips purpose processors, memory chips and other standard components. and other standard components. Sharif University of Technology Introduction to ASICs Page 3

ASIC Vs. Standard IC ASIC Vs. Standard IC ASICs: ASICs: Standard ICs: � Good security of intellectual property G d i f i ll l Typically low component cost � � Optimum system design Parts available off the shelf � � Relatively efficient use of board space y p Proven component reliability Proven component reliability � � (smaller systems) Multiple sourcing � � Reliability enhanced at system level System house not required to have y q ( ewe co po e ts) (fewer components) � in-house experts in chip design � Performance may be better than comparable standard ICs (unique Examples: chipsets, telecom ICs, � features and lower power consumption) features and lower power consumption) processors, interface ICs, logic ICs, i f IC l i IC � Reduced cost for storage (less memory circuits. components to store) � D i � Design cost is high and design cycle is t i hi h d d i l i long Sharif University of Technology Introduction to ASICs Page 4

ASICs Advantages and Disadvantages ASICs Advantages and Disadvantages g g g g Advantages Advantages Disadvantages Disadvantages � Efficient use of board space Effi i f b d � Potential for design failure P P Potential for design failure i l f i l f d i d i f il f il (lower final system cost) � Not off Not off- -the the- -shelf available shelf available � P � Product security d t it ( p ( p (specification, design, testing (specification, design, testing ifi ifi ti ti d i d i t ti t ti and documentation phases are and documentation phases are � Unique features and fine-tuning needed) needed) needed) needed) the product the product � High unit cost of IC (higher High unit cost of IC (higher � Optimized system performance initial costs of initial costs of development) development) p p ) ) � Possible product differentiation � Possible product differentiation Sharif University of Technology Introduction to ASICs Page 5 of 32

ASIC vs the Rest ASIC vs the Rest W OPS/mW 1000 Dedicated HW ncy: MO (ASICs) (ASICs) 100 Reconfigurable Efficien Processor/Logic Processor/Logic 10 ASIPs Energy E DSPs DSPs 1 Embedded E Processors Processors .1 Flexibility Sharif University of Technology Introduction to ASICs Page 6

ASIC Tasks and Roles ASIC Tasks and Roles � System Designer, Architect System Designer, Architect � System Level Functional Specification, Architectural System Level Functional Specification, Architectural y y p p , , Specification Specification � Performance and Power Consumption Specification Performance and Power Consumption Specification � Partitioning across domains Partitioning across domains – – RF/Analog, Digital, Software RF/Analog, Digital, Software – Estimates E i E i Estimates � Block Level Partitioning, Interfaces Block Level Partitioning, Interfaces � Memory and Interconnect Hierarchy Memory and Interconnect Hierarchy � Power Management Strategy � Power Management Strategy Power Management Strategy Power Management Strategy � Chip Level Planning Chip Level Planning – Package, Pads, I/O Package, Pads, I/O – Preliminary Floorplan Preliminary Floorplan Preliminary Floorplan Preliminary Floorplan – Global Control and Timing Global Control and Timing – Clock and Reset strategy Clock and Reset strategy – DFT Strategy DFT Strategy DFT Strategy DFT Strategy � Startup and Boot Sequence Startup and Boot Sequence Sharif University of Technology Introduction to ASICs Page 7

ASIC Tasks and Roles (cont’d) ASIC Tasks and Roles (cont’d) � Logic Designer Logic Designer � Block Level Design � Block Level Design Block Level Design Block Level Design � Detailed Block Level Design Specification Detailed Block Level Design Specification � Synthesis and hand Synthesis and hand- -off of a off of a timing clean timing clean block block � Exhaustive block level verification with near perfect code coverage Exhaustive block level verification with near perfect code coverage � Verification Engineer Verification Engineer � Verification Plan � Verification Plan Verification Plan Verification Plan � Modeling of Environment Modeling of Environment � Verification Environment, Scripts, Regression Verification Environment, Scripts, Regression � DFT Engineer DFT Engineer DFT E DFT E i i � DFT logic DFT logic � Boundary Scan � Boundary Scan Boundary Scan Boundary Scan � ATPG ATPG Sharif University of Technology Introduction to ASICs Page 8

ASIC Tasks and Roles (cont’d) ASIC Tasks and Roles (cont’d) � Front end ASIC Engineer Front end ASIC Engineer � Chip Level � Chip Level Chip Level Chip Level – Synthesis Strategy Synthesis Strategy – Synthesis Scripts Synthesis Scripts – Timing Analysis Timing Analysis g g y y – Interface to backend Interface to backend � Back end ASIC Engineer Back end ASIC Engineer � Floorplanning � Floorplanning Floorplanning Floorplanning � Place and Route Place and Route � Clock Tree Synthesis Clock Tree Synthesis � Power routing � Power routing Power routing Power routing � Pads and Package Pads and Package � Integration and Test Integration and Test Sharif University of Technology Introduction to ASICs Page 9

ASIC Project Phases ASIC Project Phases Requirements Capture Requirements Capture 1. 1. � Market Survey Business Opportunities Customer Interaction � Market Survey, Business Opportunities, Customer Interaction Market Survey Business Opportunities Customer Interaction Market Survey, Business Opportunities, Customer Interaction � Requirements Specification Requirements Specification – – CRS (Customer Requirements CRS (Customer Requirements Specification) Specification) – Hierarchical list of requirements Hierarchical list of requirements – Peformance, Cost and Delivery Schedule Peformance, Cost and Delivery Schedule PreStudy PreStudy PreStudy PreStudy 2. 2. 2 � Estimate Die Size, Package, Power Consumption, Performance, Estimate Die Size, Package, Power Consumption, Performance, Development, Manufacturing, Integration and Test Times Development, Manufacturing, Integration and Test Times � Buy or Develop Decisions Buy or Develop Decisions � Explore architectural and algorithmic alternatives Explore architectural and algorithmic alternatives � Interact with Customer, Marketting and refine Requirements doc. Interact with Customer Marketting and refine Requirements doc Interact with Customer Marketting and refine Requirements doc Interact with Customer, Marketting and refine Requirements doc. � Quit or go ahead decision Quit or go ahead decision Sharif University of Technology Introduction to ASICs Page 10

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.