Problems for MOS Section Lecture notes: Sec. 4 F. Najmabadi, ECE65, - PowerPoint PPT Presentation

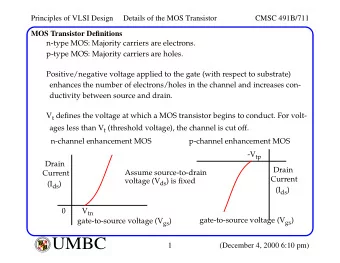

Problems for MOS Section Lecture notes: Sec. 4 F. Najmabadi, ECE65, Winter 2012 Exercise 1: Compute i D ( p C ox ( W/L ) = 0.4 m A/V 2 , V tp = 3 V and = 0 ). PMOS with v SG = 5 V and v GD = 6 V. V OV = v SG | V tp | = 5

Problems for MOS Section Lecture notes: Sec. 4 F. Najmabadi, ECE65, Winter 2012

Exercise 1: Compute i D ( µ p C ox ( W/L ) = 0.4 m A/V 2 , V tp = − 3 V and λ = 0 ). PMOS with v SG = 5 V and v GD = 6 V. V OV = v SG – | V tp | = 5 – 3 = 2 V V OV > 0 → MOS is ON o v SD = v SG + v GD = 5 + 6 = 11 V v SD = 11 > V OV = 2 → MOS in saturation o W = µ = × × = 2 - 3 2 0 . 5 0.5 0.4 10 (2) 0.8 mA i C V D p ox OV L F. Najmabadi, ECE65, Winter 2012

Exercise 2: Find V S ( µ n C ox ( W/L ) = 0.5 m A/V 2 , V tn = 0.8 V and λ = 0 ). Since i D = 10 µ A, MOS is ON Assume MOS in saturation W = µ 2 0 . 5 i C V D n ox OV L × = × × → = - 6 - 3 2 10 10 0.5 0.5 10 0 . 2 V V V OV OV = + = + = 0 . 2 0 . 8 1 V v V V GS OV t = − = − → = − 0 1 V v V V V V GS G S S S = − = − − = 7 ( 1 ) 8 V v V V DS D S = > = 8 0.2 V (MOS in saturation ) v V DS OV F. Najmabadi, ECE65, Winter 2012

Exercise 3: Consider this PMOS with µ p C ox ( W/L ) = 0.6 m A/V 2 , V tp = −1 V and λ = 0 . For what values of V G , PMOS will be ON? A) For what values of V D , PMOS will be in triode? (in terms of V G ) B) For what values of V D , PMOS will be in saturation? (in terms of V G ) C) = − = − 5 v V V V SG S G G = − = − 5 v V V V SD S D D = − = − − = − | | 5 | | 4 V v V V V V OV SG tp G tp G A) Range of V G for MOS ON? ≥ → − ≥ → ≤ 0 4 0 4 V V V V OV G G B) Range of V D for MOS in triode? ≤ → − ≤ − → ≥ + 5 4 1 v V V V V V SD OV D G D G C) Range of V D for MOS in saturation? ≥ → − ≥ − → ≤ + 5 4 1 v V V V V V SD OV D G D G F. Najmabadi, ECE65, Winter 2012

Exercise 4: Find v GS , v DS , and i D ( µ n C ox ( W/L ) = 0.4 m A/V 2 , V tn = 3 V and λ = 0 ). = + + − = + + − 6 3 3 GS - KVL : 0 10 10 15 10 15 i v i V V i G GS D OV t D → = + 3 12 10 V i OV D = + + − 3 3 DS - KVL : 15 10 10 15 i v i D DS D → = + × 3 30 2 10 v i DS D Not in cut-off as for i D = 0, GS-KVL gives V OV =12 V > 0. Assume MOS in saturation W = µ 2 0 . 5 i C V D n ox OV L = + × × × 3 - 3 2 GS - KVL : 12 10 0.5 0.4 10 V V OV OV + − = 2 0.2 12 0 V V OV OV = − > 10 . 64 V ( incorrect, need 0) V V OV OV = → = 5 . 64 V 8 . 64 V V v OV GS = + → = 3 GS - KVL : 12 10 6 . 36 mA V i i OV D D = + × → = 3 DS - KVL : 30 2 10 17 27 V v i v . DS D DS = > = 17.3 5.64 V (MOS in saturation ) v V F. Najmabadi, ECE65, Winter 2012 DS OV

Exercise 5: Find R such that PMOS is in saturation with V OV = 0.6 V ( µ p C ox = 0.1 m A/V 2 , W/L = 10/0.18 , V tp = −0.4 V and λ = 0) . In an IC, W/L (typically specified as a fraction) is a design parameter for MOS circuits. W = µ = × × × × = 2 - 3 2 0 . 5 0.5 0.1 10 ( 10 / 0 . 18 ) ( 0 . 6 ) 1 mA i C V D p ox OV L = + SG - KVL : 1.8 Ri v D SG = − + + 3 10 | | R V V OV tp − = + + 3 1.8 10 0 . 6 0 . 4 R = Ω 800 R = + → = SD - KVL : 1.8 1 . 0 V R i v v D SD SD = > = → 1 . 0 0 . 6 MOS in saturation v V SD OV F. Najmabadi, ECE65, Winter 2012

Exercise 6: Find V D ( µ n C ox ( W/L ) = 0.5 m A/V 2 , V t = 0.8 V and ignore channel-width modulation). When the gate and drain of a MOS are connected to each other, MOS becomes a 2-terminal device. o Called diode-connected transistor If MOS is ON ( v DS = v GS ≥ V t ), MOS will always be in saturation! o v DS = v GS ≥ v GS − V t = V OV W = µ 2 0 . 5 i C V D n ox OV L = + = × × × + + 3 3 - 3 2 5 10 10 0.5 0.5 10 DS/GS - KVL : i v V V V D GS OV OV t + − = 2 0.25 4 . 2 0 V V OV OV = − > 6 . 56 V ( incorrect, need 0) V V OV OV = 2 . 56 V V OV = + → = = = 3 . 36 V v V V V v v GS OV t D DS GS F. Najmabadi, ECE65, Winter 2012

Exercise 7: Find V 1 and V 2 ( µ n C ox ( W/L ) = 5 m A/V 2 , V t = 1 V and ignore channel-width modulation). = + − = + + − 3 3 0 10 2 . 5 10 2 . 5 GS1 - KVL : v i V V i 1 1 GS D OV t D → + = 3 10 1 . 5 V i 1 OV D = + + − 3 2.5 10 2 . 5 GS2 - KVL : v v i 2 1 GS DS D = + + − 3 2.5 10 2 . 5 DS - KVL : v v i DS 2 DS 1 D = = KCL : i i i 1 2 D D D Q1 is not in cut-off as for i D1 = 0, GS1-KVL gives V OV =1.5 V > 0. Q2 is not in cut-off either as i D1 = i D2 > 0 o F. Najmabadi, ECE65, Winter 2012

Exercise 7 (cont’d) : Find V 1 and V 2 ( µ n C ox ( W/L ) = 5 m A/V 2 , V t = 1 V and ignore channel-width modulation). Assume both MOS in saturation W = = µ 2 0 . 5 i i C V 1 1 D D n ox OV L = + = + × × × 3 3 - 3 2 1.5 10 10 0.5 5 10 GS1 - KVL : V i V V 1 1 OV D OV OV + − = 2 2.5 1 . 5 0 V V 1 1 OV OV = − > 1 . 0 V ( incorrect, need 0) V V 1 OV OV = 0 . 60 V V OV 1 Both MOS in saturation, i D 2 = i D 1 and λ = 0: V OV 2 = V OV 1 = 0.60 V = + = + = 0 . 6 1 1 . 6 V v V V 1 1 GS OV t = − = − → = − 0 1 . 6 V v V V V V 1 1 1 2 2 GS G S = + = + = 0 . 6 1 1 . 6 V v V V 2 2 GS OV t = − = − → = 2 . 5 0 . 9 V v V V V V 2 2 2 1 1 GS G S F. Najmabadi, ECE65, Winter 2012

Exercise 7 (cont’d) : Find V 1 and V 2 ( µ n C ox ( W/L ) = 5 m A/V 2 , V t = 1 V and ignore channel-width modulation). Need to confirm our assumption of both MOS in saturation = − = − = − − = 0 . 90 ( 1 . 6 ) 2 . 5 V v V V V V 1 1 1 1 2 DS D S = > = 2 . 5 0 . 6 V v V 1 1 DS OV = − = − = − = 2 . 5 2 . 5 0 . 9 1 . 6 V v V V V 2 2 2 1 DS D S = > = 1 . 6 0 . 6 V v V 2 2 DS OV For circuits with multiple transistors, it is usually advantageous to keep track of node voltages (at transistor terminals! F. Najmabadi, ECE65, Winter 2012

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.