Pre-Knowledge In order to complete this lab - PDF document

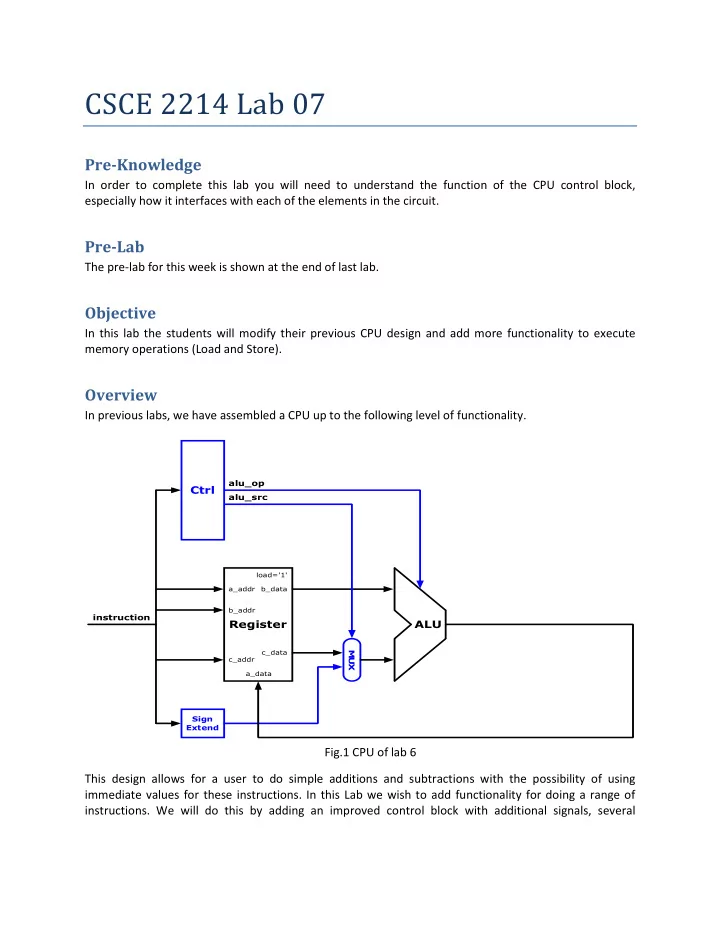

Pre-Knowledge In order to complete this lab you will need to understand the function of the CPU control block, especially how it interfaces with each of the elements in the circuit. Pre-Lab

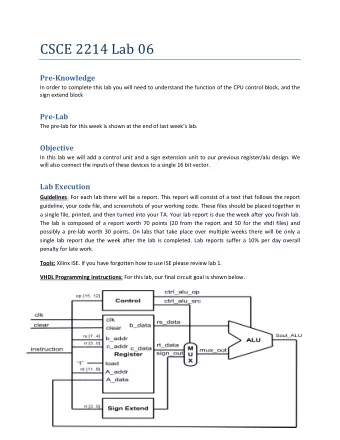

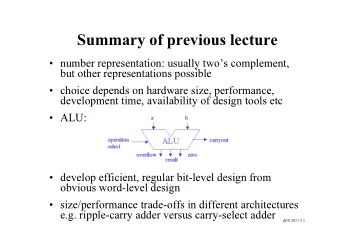

����������������� Pre-Knowledge In order to complete this lab you will need to understand the function of the CPU control block, especially how it interfaces with each of the elements in the circuit. Pre-Lab The pre-lab for this week is shown at the end of last lab. Objective In this lab the students will modify their previous CPU design and add more functionality to execute memory operations (Load and Store). Overview In previous labs, we have assembled a CPU up to the following level of functionality. ������ ���� ������� �������� ������ ������ ������ ����������� �������� ��� ������ � ������ � � ������ ���� ������ Fig.1 CPU of lab 6 This design allows for a user to do simple additions and subtractions with the possibility of using immediate values for these instructions. In this Lab we wish to add functionality for doing a range of instructions. We will do this by adding an improved control block with additional signals, several

multiplexers, and finally a Data Memory. A visual representation of what our circuit will now look like is shown below with the blue lines representing the new circuits: ������� ������ ������ ������ ���� ������� �������� �������� ���� ������ ������ ������ ������ ������ ����������� �������� ��� ���� �������� ��� ������� ������ ��� ��� ���� ������ ������ ������ ���� ������ Fig.2 CPU of lab 6 plus added circuitry. As you can see several signals have been added to the control block, a data memory block has been added, and finally a multiplexer has been added to the register input c_addr as well as on the output of the Data Memory (data_out). These modifications allow us to execute simple R-Type & I-Type instructions as well as Load word and Store Word as shown below. Note: You may have to zoom in using your word processor to make out all of the signal names.

������� ������ ������ ����� ������ ���� ������� �������� �������� ���� ���� ������ ������ ������ ������ ��� ������ ����������� �������� ��� ���� �������� ��� ��� ������� ������ ��� ��� ���� ���� ������ ������ ������ R-Type ��� ���� ������ Fig.3 Architecture of R-Type Instruction ������� ������ ������ ����� ������ ���� ������� �������� �������� ���� ���� ������ ������ ������ ������ ��� ������ ����������� �������� ��� ���� �������� ��� ��� ������� ������ ��� ��� ���� ���� ������ ������ I-Type ������ ��� ���� ������ Fig.4 Architecture of I-Type Instruction

������� ������ ������ ����� ������ ���� ������� �������� �������� ���� ���� ������ ������ ������ ������ ��� ������ ����������� �������� ��� ���� �������� � � � ��� ������� ������ � � ���� ���� ������ � � � � ������ Load Word ������ ��� ���� ������ Fig.5 Architecture of Load Instruction ������� ������ ������ ����� ������ ���� ������� �������� �������� ���� ���� ������ ������ ������ ������ ��� ������ ����������� �������� ��� ���� �������� � �� ��� ������� ������ � � ���� ���� ������ �� �� ������ ������ Store Word ��� ���� ������ Fig.6 Architecture of Store Instruction

The above figure is the final goal of this assignment. Some of the components are given to you as additional materials. It is your responsibility to implement the rest of the design. The test bench for this lab is provided in Table 1. Control Unit: In this lab, the previous control unit will be modified to add more instructions. The op code value is still 4 bits long and the corresponding instruction (to be used in this lab) is given in the table below : Opcode(Binary) Operation 0000 ADD 0001 SUB 0010 AND 0011 OR 0100 ADDI 0101 SUBI 1000 LW 1100 SW The following interface could be used to implement the control block: Entity Control is Port( op : in std_logic_vector( 3 downto 0); alu_op : out std_logic_vector( 1 downto 0); alu_src : out std_logic; reg_dest : out std_logic; reg_load : out std_logic; reg_src : out std_logic_vector(1 downto 0); mem_read : out std_logic; mem_write : out std_logic ); End control; e.g: In case of a SW Rd, off(Rs) instruction (opcode 1100), we will have the following configuration: alu_op = 0 => The offset will be added to the Rs address to compute the location where to store the Rd value inside the data memory. alu_src = 1 => Since the second operand of SW is an offset (integer), the output of the signExtend unit must be selected. reg_dest = 1 => Since the input address for c_addr should be Rd, this value is therefore set to 1. reg_load = 0 => No value is saved in the Register file. reg_src = 1 => The output of the ALU is the location where Rd has been saved in the Data memory. Setting reg_src to 1 allows us to monitor the value of that memory location. mem_read = 0 => This is not a memory read operation mem_write = 1 => Rd value is saved in the data memory. It’s therefore a memory write.

Data Memory Unit: this is the logic implementing the data memory. This unit will be provided to you as additional material, along with the file to initialize the memory. You will place those two file (memory.vhd and memory.txt) inside your project. Just make sure to look how its interface has been declared in order to instantiate it properly in the Toplevel file of your design. For the declaration of the Data Memory in the Toplevel entity and initialization with the values in the text file, use the following instructions: component Memory generic (INPUT : string := " memory.txt "); port ( clk : in std_logic; read_en : in std_logic; write_en : in std_logic; addr : in std_logic_vector(15 downto 0); data_in : in std_logic_vector(15 downto 0); data_out : out std_logic_vector(15 downto 0) ); end component; Lab Execution Guidelines : For each lab there will be a report. This report will consist of a text that follows the report guideline, your code file, and screenshots of your working code. These files should be placed together in a single file, printed, and then turned into your TA. Your lab report is due the week after you finish lab. The lab is composed of a report worth 70 points (20 from the report and 50 for the vhdl files) and possibly a pre-lab worth 30 points. On labs that take place over multiple weeks there will be only a single lab report due the week after the lab is completed. Lab reports suffer a 10% per day overall penalty for late work. Tools: Xilinx ISE. If you have forgotten how to use ISE please review lab 1. VHDL Programming instructions: An overview of each of the given components is below: ALU: This is a 16 bit ALU that functions as your previous ALU did. • Register: This is a 16 bit register that functions as your previous Register did. • Sign Extend: This block functions as your previous sign extension block did. • Multiplexers: 2-to-1 and 3-to-1 multiplexer units as already implemented in the previous labs. • CTRL : This block functions as your previous one did while adding the signals below: • o Reg_src – This control signal decides whether the value driving the a_data input is coming from Data Memory or an ALU operation. o Mem_wr & Mem_re – these signals enables or disables memory writing/reading. o Reg_load – this signal enables writing to the register. o Reg_dest – this signal decides which portion of the instruction is applied to c_addr. � It is set to 1 for the SW instruction

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.