Power dissipation! Electrical Engineering Department Technion Israel - PDF document

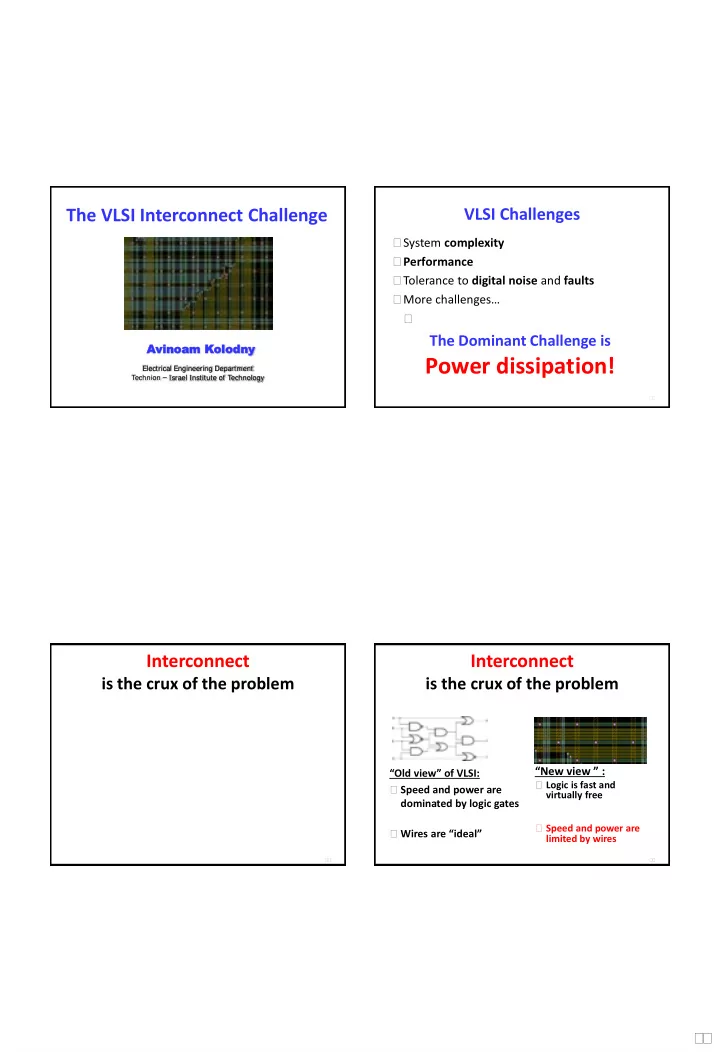

The VLSI Interconnect Challenge VLSI Challenges System complexity Performance Tolerance to digital noise and faults More challenges The Dominant Challenge is Avinoam Kolodny Power dissipation! Electrical Engineering

The VLSI Interconnect Challenge VLSI Challenges � System complexity � Performance � Tolerance to digital noise and faults � More challenges… � The Dominant Challenge is Avinoam Kolodny Power dissipation! Electrical Engineering Department Technion – Israel Institute of Technology � � Interconnect Interconnect is the crux of the problem is the crux of the problem “New view ” : “ Old view” of VLSI: � Logic is fast and � Speed and power are virtually free dominated by logic gates � Speed and power are � Wires are “ideal” limited by wires � � � � � � � � � �

2001 - Extrapolation Towards A Power Crisis Outline of this talk 10000 Power Density (W/cm 2 ) � Background of the VLSI interconnect challenge Rocket Nozzle 1000 � Implications for energy-efficient computing Nuclear Reactor 100 Pentium 4 � Research directions � Pentium 3 NMOS to CMOS transition 8086 Hot Plate 10 Pentium Pro i286 Pentium 8085 i486 i386 8080 4004 1 1970 1980 1990 2000 2010 2020 � � Year � � �� � � � � � � � � �� � � � � � � � � � � � � � ��� �� � � � Interconnect Power: VLSI hits the power wall A case study - 2004 10000 � Intel’s Pentium -M, low-power microprocessor, 0.13 micron CMOS � � � Bit-Transportation energy is larger than computation energy! � � � � � � � � � � Power Density (W/cm 2 ) � ���� � 1000 � � � � � � � �� 100 � � �� � � � � � � � � Pentium 4 � � � � NMOS to CMOS Pentium 3 transition 8086 � �� � � � � � � � � � � � � � � � � � � 10 Pentium Pro � � �� � � � � � � � � � � � i286 Pentium � � � � � � � � � � 8085 � i486 8080 i386 4004 1 � � � � � � � � � � � � � � � � � � � � � � � �� � � �� � � � � � � � � � � � �� � � � 1970 1980 1990 2000 2010 2020 � � � � � �� � � � � � � � � � � � � � � � �� � � �� � � � � � � � �� � � � � � � � � � � � � � � � � � ��� � �� � �� � � � � � � � �� � � � � �� � � � � � � � � �� � � � � � � � � � � � � � ��� �� � � � Year � �

Technology Scaling: Chips are Like Cities: Faster Transistors, Slower Wires Complexity is Shown in Connectivity � In each generation of technology: � More transistors � More interconect wires � � �� � � � � � � � � � � � � � � �� � � � � � �� � � ��� �� � � � � � � � � � � � � � �� � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � Technology Scaling: Trying to Keep Wire Resistance in Check Faster Transistors, Slower Wires Leads to Larger Capacitances � � � � � � � � � ��� � � � � � � � � � � � � � � � �� � � �� � � �� � � � � � � � � � � � � � � � � � �� � � � � � � � � � � � � � � �� � � � � � �� � � ��� �� � � � � � � � � � � � � � �� � 1 2 3 k � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � �� � � � � � � �

The Nature of Design for Low-Power If Bits Were Cars…. � � � � � � � � � � � � � � � � � � � � � � � � � � No critical root cause � � � � � � � Because power is cumulative � Need power-saving efforts at all levels! � � � � � � � � � � � � � � � � Wire layout optimization: 3 Types of Improvement Wire Widths and Spaces in a Wire Bundle � � � � �� � �� � � � � � �� � � � � �� � � � � � �� � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � � ��� � � 1 Reduce waste of energy � 2 (Optimal) Tradeoff power with delay (or other metric) � � � � 3 Change the algorithm or computational task � � � � � � � � � � � � � � � � � � �� �� � � � � �� ��� � � � � � �� � � �� � � � � � � � � � � � � � � � � � � � � � � � � � � � � �� � � � � � � �� �� � � � � � � � �� ��� � � � � � � � � � � �� � � �� �� � � � � � � � � �� � � � � � � � ��� � �� ��� � � � � � � � � � � � � � � � � � � � � � � � � � � � �� � � � � � � � � � � � �� � � � � � � � � � � � �� � � �� � � � � � � � � �� � � � � � � � � � � � �� � � � � � � � �� � � � � � � � � � � � � � � � � � � � � � � � � � � �� � �� � �� � � � � � iccad � � � � � � � � � � � � � �� � � � � � � � � � � � � � � � � � � � � � � � � � � � � �

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.