Motivation Physical implementation impacts power dissipation. - PDF document

Motivation Physical implementation impacts power dissipation. Implementation Techniques for Reduced Power and Energy Professor Per Larsson-Edefors Computer Science and Engineering Chalmers University of Technology Implementation

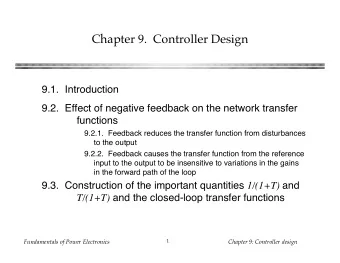

Motivation • Physical implementation impacts power dissipation. Implementation Techniques for Reduced Power and Energy Professor Per Larsson-Edefors Computer Science and Engineering Chalmers University of Technology Implementation Techniques for Reduced Power and Energy, March 16, 2012 Page 1 Implementation Techniques for Reduced Power and Energy, March 16, 2012 Page 2 Field-Effect Transistor Basics Switching Power Dissipation • MOSFET. • For one full transition, that is, rising + falling output signal: • Voltage is applied on gate. P sw = E / T = ( Q V )/ T = ( CV V ) f. • The electric field regulates the material properties • To reduce switching power… g beneath gate beneath gate. d d – reduce supply voltage ( V DD ). g • Threshold voltage ( V TH ): s – reduce clock frequency ( f ). V TH is the gate voltage – reduce signal activity ( α ). required to create a Source: USC conducting channel. Conducting channel – reduce nodal capacitance ( C ). can be created. P sw = f α C V DD 2 Body electrode. Implementation Techniques for Reduced Power and Energy, March 16, 2012 Page 3 Implementation Techniques for Reduced Power and Energy, March 16, 2012 Page 4 Energy, Speed, and Power Voltage Scaling for Reduced P sw • To maintain switching speed, V TH must follow V DD . Source: LPDE’09/Ch 1 Implementation Techniques for Reduced Power and Energy, March 16, 2012 Page 5 Implementation Techniques for Reduced Power and Energy, March 16, 2012 Page 6

Unwanted Consequences of Scaling, 1 Subthreshold Operation • But … as V TH decreases, the subthreshold leakage in the subthreshold leakage in 0 1 off-state transistors increases: P leak ∝ e - VTH . S = 60 mV/decade Implementation Techniques for Reduced Power and Energy, March 16, 2012 Page 7 Implementation Techniques for Reduced Power and Energy, March 16, 2012 Page 8 Unwanted Consequences of Scaling, 2 Projections on Power • Physical dimensions scaled down to the level when tunneling through g g insulators occurs. • High-K gate insulator and metal gate technology. Implementation Techniques for Reduced Power and Energy, March 16, 2012 Page 9 Implementation Techniques for Reduced Power and Energy, March 16, 2012 Page 10 Low-Power Technique 1: Body Biasing Binning for Performance and Power • Reverse body biasing (RBB) ⇒ V B < 0 V (NMOSFET) ⇒ V TH increases • In P ∝ e - VTH , V TH depends on ⇒ leakage decreases. MOSFET terminal voltages. MOSFET terminal voltages. 0 0 1 1 • Forward body biasing (FBB) • In an NMOSFET, ⇒ V B > 0 V (NMOSFET) V TH decreases with an ⇒ V TH decreases increasing body voltage ( V B ). ⇒ higher speed. Source: ABB’02 V B • Performance and power binning becomes possible. Implementation Techniques for Reduced Power and Energy, March 16, 2012 Page 11 Implementation Techniques for Reduced Power and Energy, March 16, 2012 Page 12

Delay Distribution of Logic Low-Power Technique 2: Multi-V T Source: LPDE 09/Ch 4 Source: LPDE’09/Ch 4 • Logic paths exhibit different delays. Source: LPDE’09/Ch 4 • Critical paths must satisfy clock rate constraint ⇒ • Assign fast paths to slow transistors ⇒ implementation must ensure gates are fast enough. use transistors with high V TH ⇒ • But what about the fast paths … can their leakage is reduced. intrinsic speed be converted to power reductions? Implementation Techniques for Reduced Power and Energy, March 16, 2012 Page 13 Implementation Techniques for Reduced Power and Energy, March 16, 2012 Page 14 Match V DD to Performance Need Low-Power Technique 3: Multi-V DD Source: LPDE’09/Ch 4 Source: LPDE 09/Ch 4 • First order delay ∝ 1/ V DD and P ∝ V DD 2 : • Reduce V DD for circuits that are not timing critical. • How many different V DD levels should be used? Dual- V DD ALU example from LPDE’09/Ch 4 Implementation Techniques for Reduced Power and Energy, March 16, 2012 Page 15 Implementation Techniques for Reduced Power and Energy, March 16, 2012 Page 16 Low-Power Technique 4: DVFS Circuit Adaptation for DVFS • Slack can be used for power reductions: power reductions: Dynamic Voltage and Frequency Scaling. • Aggressive V DD reduction causes timing violations! Read more in CATPE’08/Ch 3 • Implement a feedback system that regulates speed, in the process also handling variations. Read more in CATPE’08/Ch 3.5 Implementation Techniques for Reduced Power and Energy, March 16, 2012 Page 17 Implementation Techniques for Reduced Power and Energy, March 16, 2012 Page 18

Example on Variations Detection of Timing Failures • Clock arrival times are hard to synchronize. • High clock rates or extremely compute-intensive code expose timing issues. Source: POWER’11 Source: ARM’11 Implementation Techniques for Reduced Power and Energy, March 16, 2012 Page 19 Implementation Techniques for Reduced Power and Energy, March 16, 2012 Page 20 Recap 1: Low-Power Techniques Low-Power Technique 5: Operand Isolation • Body biasing � Feedback Distributed MUX Distributed State-Reg CRC5 STATE- MUX5 • Multi- V TH � REG5 • Multi- V DD � CRC8 STATE- MUX3 Input REG3 Output • DVFS � 32 32 CRC16 STATE- MUX8 MUX8 • Operand isolation REG8 STATE- • Factoring CRC32 REG16 ModeSel • Encoding [1:0] Enb Clk Bus width: 3-bit; 5-bit; 8-bit; 16-bit; 32-bit; • Clock gating • Reduce P sw by gating input signals • Power gating which are not needed. Implementation Techniques for Reduced Power and Energy, March 16, 2012 Page 21 Implementation Techniques for Reduced Power and Energy, March 16, 2012 Page 22 Multiplier Circuit for Variable Data Width Low-Power Technique 6: Factoring Source: Synopsys • Reduce P sw by reordering gates to minimize the Read more in CATPE’08/Ch 4.3 • 1x16-b mode ⇒ >60% power reduction. switched capacitance of f α C V DD 2 . Implementation Techniques for Reduced Power and Energy, March 16, 2012 Page 23 Implementation Techniques for Reduced Power and Energy, March 16, 2012 Page 24

Low-Power Technique 7: Encoding Low-Power Technique 8: Clock Gating Read more in LPDE’09/Ch 6 and CATPE’08/Ch 4.12 • Encode data before bus transmission. Source: LPDE’09/Ch 8 • Above: Bus invert coding reduces 64 trans. to 53. Implementation Techniques for Reduced Power and Energy, March 16, 2012 Page 25 Implementation Techniques for Reduced Power and Energy, March 16, 2012 Page 26 Recap 2: Low-Power Techniques The Energy Perspective, 1 • Body biasing • Accelerators ⇒ reduce execution time + energy. � • Multi- V TH � • Multi- V DD � • DVFS � • Operand isolation � • Factoring � • Encoding � • Clock gating � • Power gating Implementation Techniques for Reduced Power and Energy, March 16, 2012 Page 27 Implementation Techniques for Reduced Power and Energy, March 16, 2012 Page 28 The Energy Perspective, 2 Low-Power Technique 9: Power Gating • Accelerators reduce energy via execution time reductions ( E = T x P ). • But accelerators also increase Enable Power switch circuit area and, probably, power dissipation. Virtual supply rail • Will the addition of an accelerator pay off? This depends on the application(s) Power switch Logic that will be executed! driver circuit • Can we do something about the power overhead? – Power gating ⇒ reduced static power. – Operand isolation/clock gating ⇒ reduced P sw . Implementation Techniques for Reduced Power and Energy, March 16, 2012 Page 29 Implementation Techniques for Reduced Power and Energy, March 16, 2012 Page 30

Power Gating of Execution Unit Power-Gated FlexCore P&R Implementation Techniques for Reduced Power and Energy, March 16, 2012 Page 31 Implementation Techniques for Reduced Power and Energy, March 16, 2012 Page 32 Power-Gated Multiplier Identify Multiply Activity Implementation Techniques for Reduced Power and Energy, March 16, 2012 Page 33 Implementation Techniques for Reduced Power and Energy, March 16, 2012 Page 34 Multiplier Utilization in Application Overall Power Gains from Power Gating • Gray – EEMBC Autocorrelation post synthesis post synthesis • Black – post P&R EEMBC FFT Implementation Techniques for Reduced Power and Energy, March 16, 2012 Page 35 Implementation Techniques for Reduced Power and Energy, March 16, 2012 Page 36

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.

![Indoor Places Lukas Kuster Motivation GPS for localization [7] 2 Motivation Indoor](https://c.sambuz.com/951195/indoor-places-s.webp)