Performance Driven Optimizations in FPGA Based QAM Systems KIT - PowerPoint PPT Presentation

Institut fr Technik der Informationsverarbeitung Directors Master Thesis Prof. Dr.-Ing. Dr. h. c. J. Becker Prof. Dr.-Ing. E. Sax Prof. Dr. rer. nat. W. Stork Supervising Tutors Alberto Sonnino M. Tech G. Shalina Dipl.-Ing. P . Figuli

Institut für Technik der Informationsverarbeitung Directors Master Thesis Prof. Dr.-Ing. Dr. h. c. J. Becker Prof. Dr.-Ing. E. Sax Prof. Dr. rer. nat. W. Stork Supervising Tutors Alberto Sonnino M. Tech G. Shalina Dipl.-Ing. P . Figuli Institut für Technik der Informationsverarbeitung (ITIV) Performance Driven Optimizations in FPGA Based QAM Systems KIT – University of the State of Baden-Wuerttemberg and www.kit.edu National Laboratory of the Helmholtz Association

Introduction and Motivation Challenges in the current trend Pursuit of high SNR and high data rate Contribution to reach future terabit’s communication FPGAs clocked below 1GHz: need for parallelism [1] 2 09.11.2009 Institut für Technik der Informationsverarbeitung (ITIV) Alberto Sonnino – Performance driven optimization in FPGA based QAM systems 06.10.2015

Introduction and Motivation My work: performance optimization of QAM transmitter Exploiting parallelism FPGA platform Mixed-domains (time and frequency) approach Current state-of-the-art 2012: 128.6 MHz achieved (University of Shanghai, China) [2] Transmitter and receiver On Xilinx Virtex IV 2013: 625.0 MHz achieved (University of Paderborn, Germany) [3] Only transmitter On Xilinx Virtex VI 2015: 750.0 MHz achieved (E2v Semiconductor, UK) [4] Only transmitter and no filter On Xilinx Virtex VI 3 09.11.2009 Institut für Technik der Informationsverarbeitung (ITIV) Alberto Sonnino – Performance driven optimization in FPGA based QAM systems 06.10.2015

Introduction and Motivation Hardware Choice FPGA because of great configurability, flexibility and cost Growing technology Modulation Choice Quadrature Amplitude Modulation (QAM) Allow carrying many bits per symbol Filter Choice Avoid Inter Symbol Interferences (ISI) Finite impulse response (FIR) Squared Raised Root Cosine (SRRC) No filter optimizations in this work [5] 4 09.11.2009 Institut für Technik der Informationsverarbeitung (ITIV) Alberto Sonnino – Performance driven optimization in FPGA based QAM systems 06.10.2015

Outline Introduction and Motivation Fundamentals Standard transmission chain Fundamentals of each block Concepts & Methodology Strategy Ideal model Implementation Implementation of each block Experimental Results Achieved precision Achieved performances Summary & Further Improvements 5 09.11.2009 Institut für Technik der Informationsverarbeitung (ITIV) Alberto Sonnino – Performance driven optimization in FPGA based QAM systems 06.10.2015

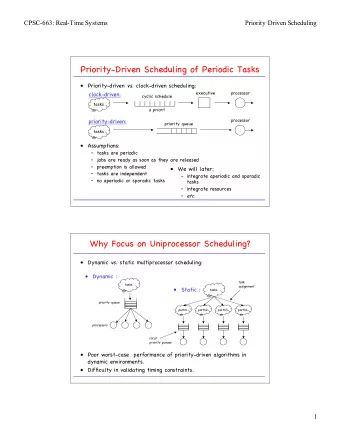

Fundamentals Standard Transmission Chain Generator Encryptor Encoder Smb. mapper Modulator Filter … 0101110101011 Z -1 Z -1 x 1011010011100110 I + + 011110 … III III C 0 C 1 C 1 - x V + + Decoder Demodulator Decryptor Smb. demapper Filter Z -1 Z -1 x Channel I + + III III C 0 C 1 C 1 x - V + + Focus of this work FIR Filter FIR Filter QAM mapper Z -1 Z -1 Z -1 Z -1 QAM QAM I I Re Re Modulator Modulator C 0 C 1 C N-1 C 0 C 1 C N Filter cos cos in + + out in + + out x x + + Modulator + FIR Filter + FIR Filter Q Im - Q Im x - x Z -1 Z -1 Z -1 Z -1 sin sin C 0 C 1 C N-1 C 0 C 1 C 1 + + + + 6 09.11.2009 Institut für Technik der Informationsverarbeitung (ITIV) Alberto Sonnino – Performance driven optimization in FPGA based QAM systems 06.10.2015

Fundamentals QAM Mapper Q M-QAM formats (M=8, 16, 32, etc.) 1101 1001 0001 0101 Clusterization in log 2 (M) bits 1100 1000 0000 0100 Gray code for hamming distance of 1 I Rectangular constellation is considered 1110 1010 0010 0110 Large M implies higher data rate 1111 1011 0011 0111 But symbol’s misinterpretation Modulator Local oscillator delivering trigonometric orthogonal carriers Multiplication and subtraction operation Re X n [ I ( t ) + iQ ( t )] e 2 π f 0 t o + out ( t ) = R cos + out LO - = I ( t ) cos(2 π f 0 t ) − Q ( t ) sin(2 π f 0 t ) sin 90° X Im 7 09.11.2009 Institut für Technik der Informationsverarbeitung (ITIV) Alberto Sonnino – Performance driven optimization in FPGA based QAM systems 06.10.2015

Fundamentals Fourier Transform Signal’s decomposition into an alternative representation Discrete Fourier Transform (DFT) sends in the Fourier domain Inverse Discrete Fourier Transform (IDFT) takes it back P N � 1 x [ n ] e � 2 π ikn/N X [ k ] = k ∈ Z 0 1 P N � 1 X [ k ] e 2 π ikn/N x [ n ] = n ∈ Z 0 N Linear operations have equivalent in Fourier domain Useful for this work: convolution becomes multiplication F � 1 {F{ f } · F{ g }} F{ f > g } F{ f } · F{ g } = = f > g F � 1 { G · F } = G · F = 8 09.11.2009 Institut für Technik der Informationsverarbeitung (ITIV) Alberto Sonnino – Performance driven optimization in FPGA based QAM systems 06.10.2015

Fundamentals Filter Nyquist criteria avoids ISI Pulse Shaping Filter to limit the transmission band FIR filter: linear phase, inherent stability, no feedback Matched filter improves SNR (if only stochastic noises) Good compromise: SRRC filter Time Domain Frequency Domain y [ n ] = x [ n ] > h [ n ] Y [ k ] = X [ k ] · H [ k ] • Convolution: difficultly parallelizable • Multiplication: easily parallelizable H 0 H 1 H N x[n] Z -1 Z -1 Z -1 X X 0 Y N X X 1 Y N C 0 C 1 C 2 C N + + + y[n] X X N Y N 9 09.11.2009 Institut für Technik der Informationsverarbeitung (ITIV) Alberto Sonnino – Performance driven optimization in FPGA based QAM systems 06.10.2015

Concepts & Methodology Strategy Reference MATLAB model Identify which part to implement in frequency domain Prototype a single channel (non parallel) transmitter Optimize for Xilinx Virtex 7 Generic model with parallelization and scalability c 0 = 0.022507907 c 1 = 0.028298439 Conceptual Model c 2 = - 0.07620194 FIR Filter c i QAM DFT IDFT Modulator I X X 00 d order 10 + 01 3d + xn xk xk xn LO 10 -d out in - FIR Filter 11 -3d 90° X Q 3d = c 5 X N-bit frame N-bit frame Carriers’s frequency f 0 c i order 10 c 3 = - 0.03750077 c 4 = 0.307673479 c 5 = 0.540985931 10 09.11.2009 Institut für Technik der Informationsverarbeitung (ITIV) Alberto Sonnino – Performance driven optimization in FPGA based QAM systems 06.10.2015

Concepts & Methodology Ideal Behaviour DFT re. part Filter re. part IDFT re. part I component c 0 = 0.022507907 c 0 = 0.022507907 c 1 = 0.028298439 c 1 = 0.028298439 c 2 = - 0.07620194 c 2 = - 0.07620194 FIR Filter FIR Filter c i c i QAM DFT IDFT Modulator Transmitter out QAM DFT IDFT Modulator I I X X 00 d X X order 10 00 d + 01 3d order 10 0001101010 … + + 01 xn xk xk xn 3d 0001101010 … LO 10 -d xn xk xk xn + out LO in 10 -d - out 11 FIR Filter in -3d - 11 -3d FIR Filter 90° X Q 90° X 3d = c 5 Q X 3d = c 5 N-bit frame N-bit frame X N-bit frame N-bit frame Carriers’s frequency f 0 Carriers’s frequency f 0 Q component c i DFT im. part c i order 10 order 10 IDFT im. part c 3 = - 0.03750077 Filter im. part c 3 = - 0.03750077 c 4 = 0.307673479 c 4 = 0.307673479 c 5 = 0.540985931 c 5 = 0.540985931 11 09.11.2009 Institut für Technik der Informationsverarbeitung (ITIV) Alberto Sonnino – Performance driven optimization in FPGA based QAM systems 06.10.2015

Implementation Implemented System clk 255 carriers.v dft_coeff.v 255 255 filter_coeff.v 255 16 N = 16 N = 16 N = 16 N = 16 255 add add 255 255 4096 last 4096 255 4096 255 4096 mult I xk_re Y_re mult 64 sn_re comb. comb. comb. com. mult 255 com. mult logic in logic logic add 4096 4096 out 255 255 N = 16 255 255 255 add mult add W = 16 4096 mult Q 4096 Y_im FORMAT = 4 sn_im xk_im srrc_filter.v modulator.v idft.v qam.v dft.v tvalid seq. reset logic transmitter.v Data Packing Parallel inputs/outputs packed into the same bus Precision fixed to 16 bits data N-1 data N-2 data 0 Each data i is a 16-bit vector N-1 N-2 N-3 1 0 12 09.11.2009 Institut für Technik der Informationsverarbeitung (ITIV) Alberto Sonnino – Performance driven optimization in FPGA based QAM systems 06.10.2015

Implementation Specifications Latency 17 cycles Parameters N # of parallel inputs FORMAT QAM format in tvalid Inputs clk Clock Transmitter reset Reset clock reset out in Cluseterd stream N Outputs tvalid Validity flag FORMAT out Output data Characteristics Input width: (FORMAT x N) Output width: 16N Uses 2N 2 complex multipliers, 4N 2 -2N adder and 4N multipliers 13 09.11.2009 Institut für Technik der Informationsverarbeitung (ITIV) Alberto Sonnino – Performance driven optimization in FPGA based QAM systems 06.10.2015

Implementation QAM Mapper clk 255 carriers.v dft_coeff.v 255 255 filter_coeff.v 255 16 N = 16 N = 16 N = 16 N = 16 255 add add 255 255 4096 last 4096 255 4096 255 4096 mult I xk_re Y_re mult 64 sn_re comb. comb. comb. com. mult 255 com. mult in logic logic logic add 4096 4096 out 255 255 N = 16 255 255 255 add mult add W = 16 4096 mult Q 4096 Y_im FORMAT = 4 sn_im xk_im srrc_filter.v modulator.v idft.v qam.v dft.v seq. tvalid reset logic transmitter.v Three parameters (N, W, FORMAT): number of inputs, bus width, QAM format 8-QAM, 16-QAM, 32-QAM, 64-QAM support Each format implemented in a separated Verilog file Generates only the circuit for the desired format 14 09.11.2009 Institut für Technik der Informationsverarbeitung (ITIV) Alberto Sonnino – Performance driven optimization in FPGA based QAM systems 06.10.2015

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.