Outline Combinational Element Combinational & sequential logic - PDF document

Outline Combinational Element Combinational & sequential logic Single-cycle CPU Multi-cycle CPU

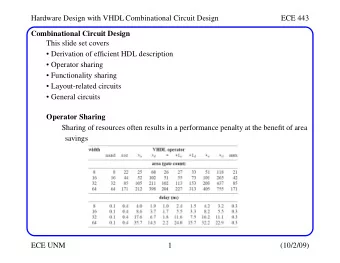

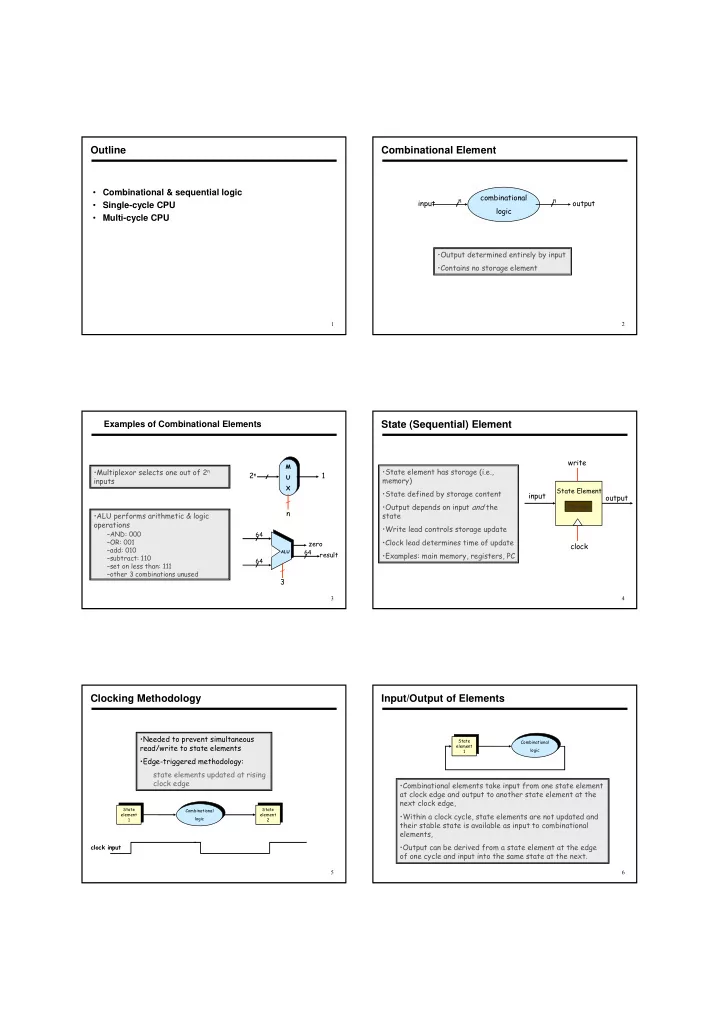

Outline Combinational Element • Combinational & sequential logic ������������� � � ����� ������ • Single-cycle CPU ����� • Multi-cycle CPU ������������������������������������ ���������������������������� � � State (Sequential) Element Examples of Combinational Elements ,���� � � ������������ �������������������� �� �*�������������������������.�/�/0� � � � � � ������1 ������ � � *�����+������ �*������������������������������� ����� ������ ������������������������� ��� ���� ������� � ��������������������������������� ����� ���������� �2��������������������������������� �!"#�$$$ '( �%#�$$� �����-������������������������������� )��� ����- ���#�$�$ '( ��� ������ �+�������#������������0����������0�3� ��������#���$ '( ����������������#���� ������&�������������������� & � � Clocking Methodology Input/Output of Elements �!������������4����������������� *����� ������������� *����� ������������� �������� ����5,���������������������� �������� ����� � ����� � �+���6���������������������# ��������������������������������� ����-����� ��������������������������-������������������������������� �������-������������������������������������������������� ���������-�����0 *����� *����� ������������� *����� *����� ������������� �������� �������� �������� �������� �2������������-������0������������������������������������ ����� � ����� � � � �����������������������4���������������������������������� ��������0 �������������������4������������������������������������ ����������� ������������������������������������������������������/� � �

Register File MIPS64 Instruction Formats �%����������������������������������� ����������������������8��&����������� '( 7 %��� %������� � ������ ��������������������������������������� %�������� 7 %������� � ���,���������������������������������� ������� ��������� ' 7 7 �' 7 2�������� ������ %��� '( 2��������� :6;��� ������ �� �� ��������� '( ������ "��� �%��������9���8��:5����������� !���������������������� ��������������������/�� &������������4���������������� ' 7 7 7 7 ' %��2���� ;��������������������� �������������������������������� ������ �� �� �� ����� ���� %6;��� �������������������������� ���������.��������������������� ,����1 �����������3�/ �%������������8����������������,���� ' �' �����������,����������������� <6;��� �4��������������������������� ������ ����������������3� �������� �%��������,��������������������� ����������������������������������� %��2���� ����� ������������������� � � Common Steps in Instruction Execution Differences in Instruction Execution • Data transfer (strictly load/store ISA) – load: access memory for read data {ld R1, 0(R2)} • Execution of all instructions require the following steps – store: access memory for write data {ld 0(R2), R1} – send PC to memory and fetch instruction stored at location • ALU instruction specified by PC – no memory access for operands – read 0-2 registers, using fields specifying the registers in the – access a register for write of result {add R1,R2, R3} instruction • Branch instruction • All instructions use ALU functionality – change PC content based on comparison {bnez R1, Loop} – data transfer instructions: compute address – ALU instructions: execute ALU operations – branch instructions: comparison & address compuation � �� Summary Data Path & Control path • Datapath is the signal path through which data in the CPU flows including the functional elements 9���� "����� %��� ������� ������ 2���� • Elements of Datapath %�������� ������ %�������� – combinational elements ���5��� = = = = = – state (sequential) elements ���� = = = = = = • Control path ����� = = = = = – the signal path from the controller to the Datapath ����������� = = = = elements ������ – exercises timing & control over Datapath elements ������������� = = = ������ �� ��

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.