Systems Multipliers and Other Circuits Shankar Balachandran* - PowerPoint PPT Presentation

Spring 2015 Week 9 Module 52 Digital Circuits and Systems Multipliers and Other Circuits Shankar Balachandran* Associate Professor, CSE Department Indian Institute of Technology Madras *Currently a Visiting Professor at IIT Bombay

Spring 2015 Week 9 Module 52 Digital Circuits and Systems Multipliers and Other Circuits Shankar Balachandran* Associate Professor, CSE Department Indian Institute of Technology Madras *Currently a Visiting Professor at IIT Bombay

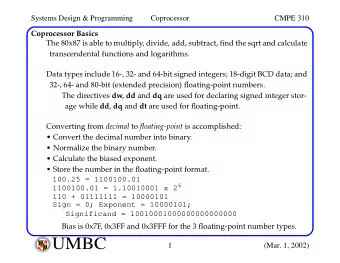

Arithmetic and Logic Unit (ALU) An ALU is a combinational circuit that can perform any of a number of different arithmetic and logical operation on a pair of n -bit operands. Operation to be performed is specified by a set of control (function-select) inputs. ALUs are designed in a bit-slice fashion and slices can be cascaded to form larger ALUs. Some ALUs are designed as an m -bit group instead of a single bit slice. m -bit group enables us to improve carry propagation within a group using carry lookahead or other similar enhancements. Arithmetic Circuits 2

Unsigned Binary Multiplication Consider unsigned m - and n -bit integers, X and Y m 1 n 1 i j X x 2 Y y 2 i j i 0 j 0 m n 1 m 1 n 1 m 1 n 1 k i j i j P X Y p 2 x 2 y 2 x y 2 k i j i j k 0 i 0 j 0 i 0 j 0 Arithmetic Circuits 3

Array Multiplier x 3 x 2 x 1 x 0 y 0 y 1 HA FA FA HA y 2 FA FA FA HA y 3 FA FA FA HA p 7 p 5 p 6 p 4 p 3 p 2 p 0 p 1 Arithmetic Circuits 4

Performance of Array Multiplier m x 3 x 2 x 1 x 0 y 0 y 1 HA FA FA HA n y 2 Critical path 1 FA FA FA HA Critical path 2 y 3 FA FA FA HA p 7 p 5 p 6 p 4 p 3 p 2 p 0 p 1 sum t t m 1 n 2 t n 1 t mult and carry Arithmetic Circuits 5

Signed Multiplication Positive Multiplicand Negative Multiplicand 0 1 1 1 0 1 0 0 1 0 (-14) (+14) (+11) (+11) x 0 1 0 1 1 x 0 1 0 1 1 0 0 0 0 1 0 0 1 0 1 1 1 1 0 1 1 1 0 0 0 0 1 0 0 1 0 1 1 1 0 1 1 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 1 0 1 0 1 1 1 0 0 0 0 0 0 0 0 0 0 0 + + 0 1 0 0 1 1 0 1 0 1 0 1 1 0 0 1 1 0 (-154) (+154) Negative Multiplier: Negate multiplier and multiplicand and use the above scheme for positive multiplier. Arithmetic Circuits 7

Modular Multiplication Using small multipliers to build larger multipliers A ≡ a 7 a 6 a 5 a 4 a 3 a 2 a 1 a 0 ≡ A 7-4 A 3-0 B ≡ b 7 b 6 b 5 b 4 b 3 b 2 b 1 b 0 ≡ B 7-4 B 3-0 A B A 7-4 A 3-0 x B 7-4 B 3-0 x A 7-4 *B 3-0 A 3-0 *B 3-0 A 3-0 * B 3-0 4 × 4 multiplier A 7-4 *B 7-4 A 7-4 * B 3-0 A 3-0 *B 7-4 4 × 4 multiplier A 3-0 * B 7-4 4 × 4 multiplier A 7-4 * B 7-4 4 × 4 multiplier A 3-0 * B 7-4 P 15-12 P 11-8 P 7-4 P 3-0 A 7-4 * B 7-4 A 3-0 * B 3-0 A 7-4 * B 3-0 a more convenient arrangement Arithmetic Circuits 8

Adding Three 4-Bit Numbers ( X, Y, Z ) x 3 y 3 z 3 x 2 y 2 z 2 x 1 y 1 z 1 x 0 y 0 z 0 FA FA FA FA FA FA FA 0 s 0 s 3 s 2 s 1 Arithmetic Circuits 9

Comparator – Equality Check x ... x x x y ... y y y ? Iterative algorithm: n 1 2 1 0 n 1 2 1 0 1. i 0; EQ 1; x i y i 0 2. if x y EQ 1 i i i then EQ 1; i 1 EQ i+1 else EQ 0; EQ i i 1 3. i i 1; 4. i n if 2; then go to step else end; x n-1 y n-1 y 2 x 2 y 1 x 0 y 0 x 1 x y x x y x y y EQUIV EQUIV EQUIV EQUIV EQ n EQ n-1 EQ 3 EQ 0 EQ 2 EQ 1 EQO EQI EQO EQI EQO EQI EQO EQI Arithmetic Circuits 10

4-Bit Comparator Magnitude comparator for n -bit unsigned binary numbers Inputs: a 3 a 2 a 1 a 0 4 4 b 3 b 2 b 1 b 0 b 3- 0 a 3- 0 altb in aeqb in agtb in altb in altb in Outputs: COMP4 aeqb in aeqb in altb out aeqb out agtb out agtb in agtb in Logic Equations: agtb a > b a = b ag tb out 3 0 3 0 3 0 3 0 in a eqb a = b aeqb out 3 0 3 0 in altb a b a b altb < = out 3 0 3 0 3 0 3 0 in a b a b a b a b a b a b a b a b a b a b a b 3 0 3 0 3 3 3 3 2 2 3 3 2 2 1 1 3 3 2 2 1 1 0 0 a b a b a b a b a b 3 0 3 0 3 3 2 2 1 1 0 0 a b a b a b 3 0 3 0 3 0 3 0 3 0 3 0 Arithmetic Circuits 11

12-Bit Comparator (unsigned) x 11…0 y 11…0 y 3…0 x 11…8 y 11…8 y 7…4 x 3…0 x 7…4 4 4 4 4 4 4 b 3- 0 a 3- 0 b 3- 0 a 3- 0 b 3- 0 a 3- 0 XLTY8 XLTY XLTY4 0 altb in altb in altb in altb in altb in altb in XEQY8 XEQY4 XEQY COMP4 COMP4 COMP4 aeqb in aeqb in aeqb in aeqb in aeqb in 1 aeqb in XGTY8 XGTY XGTY4 agtb in agtb in agtb in agtb in agtb in agtb in 0 Arithmetic Circuits 12

MIN/MAX Circuit Use a 4-bit comparator to design an 8-bit MIN/MAX circuit. Inputs: unsigned inputs, X ≡ x 7..0 , Y ≡ y 7..0 and a control signal MINMAX Output: min X Y , MINMAX 1 if Z max X Y , MINMAX 0 if MINMAX X>Y MINMAX Z S 0 0 1 Y X COMP 12 0 1 X 0 X>Y Y 1 0 X 0 12 S 1 1 1 Y 0 Z MUX 1 12 Arithmetic Circuits 13

End of Week 9: Module 52 Thank You Multipliers+Others 14

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.