Noise in High-Speed Digital to Analog Converters P .-Y. Bourgeois - PowerPoint PPT Presentation

2015 IFCS / EFTF Joint Meeting Denver, CO, USA, April 12-16, 2015 Noise in High-Speed Digital to Analog Converters P .-Y. Bourgeois , T. Imaike , G. Goavec-Merou , E. Rubiola CNRS FEMTO-ST Institute, Besancon, France

2015 IFCS / EFTF Joint Meeting Denver, CO, USA, April 12-16, 2015 Noise in High-Speed Digital to Analog Converters P .-Y. Bourgeois ∇ , T. Imaike ∇ ∃ , G. Goavec-Merou ∇ , E. Rubiola ∇ ∇ CNRS FEMTO-ST Institute, Besancon, France ∃ Nihon University, Japan • Hardware • Digital filtering • Transition noise • Phase noise • Cross spectrum home page http://rubiola.org

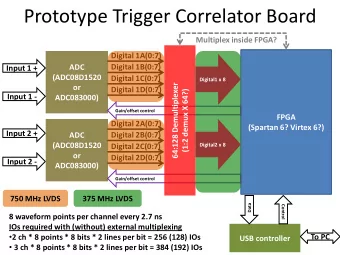

2 Hardware AD9467 / Single LTC2145 / Dual LTC2158 / Dual ADC type Alazartech Red Pitaya Eval board board) board Platform Computer Zynq (onboard) Zynq (separated) Sampling ƒ 250 MHz 125 MHz 310 MHz Input BW 900 MHz 750 MHz 1250 MHz Bits / ENoB 16 / 12 14 / 12 14 / 12 Exp.noise (2V fsr ) –158 dBV 2 /Hz –155 dBV 2 /Hz –159 dBV 2 /Hz 0? / 100 fs di ff Delay / Jitter 1.2 ns / 60 fs 1 ns / 150 fs 0? / 80 fs single 1.8 V & 3.3 V 1.8 V 1.8 V Power supply 1.33 W 190 mW 725 mW Dissipation is relevant to thermal stability For reference, 100 fs jitter is equivalent to carrier ƒ 𝛘 rms S 𝛘 (ƒ) = b 0 10 log 10 [L(f)] 10 MHz 6.3 µrad 4x10 –18 rad 2 /Hz –177 dBc/Hz 100 MHz 63 µrad 4x10 –17 rad 2 /Hz –167 dBc/Hz

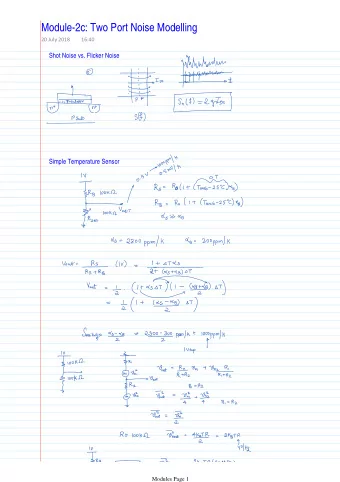

3 Digital Filter and Decimation Noise, Sampling, and Solution: V 2 σ 2 = FSR the Parseval theorem Fast sampling, and filter 12 × 2 2 m S (ƒ) S (ƒ) σ 2 = NB σ 2 = B σ 2 slow sampling digital filer n B n N 0 after sampling fast sampling fast sampling N 00 ƒ ƒ B n = 1 B 2 f N B 0 B 00 signal BW sampling BW h(t) • Convolution with low-pass h(t) 2 B 2 π B sin(2 π BT ) • 127 coe ff . Blackman-Harris kernel 2 π BT t provides 70 dB stop-band attenuation • Future: we will use H(ƒ) 1 / 2 B >>127 coe ffi cients 1 D ƒ − B B

4 Sampling Frequency S V (ƒ), dBV 2 /Hz AD9467 (Alazartech) 50 MHz 100 MHz 250 MHz The observed floor fits the theory We always use the highest sampling frequency

LTC2158-14: Shorted Input 5 Transition Noise Histogram 25000 20000 High-Speed Converters 15000 COUNT P(N) N 10000 +3 5000 +2 +1 V 0 0 8192 8196 8200 8204 8208 8212 8216 –1 –2 N –3 –8 –6 –4 –2 0 +2 +4 +6 +8 –8 –6 –4 –2 0 2 4 6 8 • Analog noise is higher than quantization noise • Given a voltage V –> random distribution of output N • This correct –> V 2 = V 2analog + V 2quant (don’t spoil the resolution with insu ffi cient no of bits) Information (bits) Equivalent No of Bits � V FSR X I = − p i log 2 ( p i ) ENoB = log 2 1 + √ 12 f N σ V i

6 Transition Noise Measurement channel a RF ADC input input τ a ADC + 10 MHz noise Σ V pp ≈ 0.95 V FSR ENoB FFT – channel b F F T W AVG RF ADC input clock distribution gain S v (ƒ) τ c τ b The di ff erential clock jitter introduces additional noise due to the asymmetry between AM and PM At 10 MHz input, ≈ 100 fs the e ff ect of jitter does not show up

7 LT 2158 Noise -40 S V (ƒ), dBV 2 /Hz "temp_g2p16_OK/dif_ab.dat" "temp_2stages/dif_ab.dat" -60 LT 2158 "temp_3stages/dif_ab.dat" -80 –104 dBV -100 2 /Hz @ 1 Hz -120 -140 –158 dBV 2 /Hz -160 ≈ 1 dB added -180 -200 -220 -240 0.001 0.01 0.1 1 10 100 1000 10000 100000 1e+06 1e+07 1e+08 10 MHz, V pp ≈ 0.95 V FSR

8 LT2145 (Red Pitaya) Noise -40 S V (ƒ), dBV2/Hz "temp_redp_0_di ff /dif_ab.dat" "temp_redp_1_di ff /dif_ab.dat" -60 LT 2145 "temp_redp_2_di ff /dif_ab.dat" -80 –110 dBV 2 /Hz @ 1 Hz -100 -120 -140 –153 dBV 2 /Hz ≈ 2 dB added -160 -180 -200 -220 -240 0.01 0.1 1 10 100 1000 10000 100000 1e+06 1e+07 1e+08 10 MHz, V pp ≈ 0.95 V FSR

9 AD9467 (Alazartech) Noise -90 "dif_cha_chb_avg100.dat" "dif_chc_chd_avg100.dat" -100 f(x) –110 dBV 2 /Hz @ 1 Hz -110 -120 -130 -140 -150 -160 –157 dBV 2 /Hz ≈ 1 dB added -170 -180 -190 1 10 100 1000 10000 100000 1e+06 1e+07 1e+08 10 MHz, V pp ≈ 0.95 V FSR

10 Digital Down Conversion input I-Q detector output data stream data stream I I-Q –> R- φ D R R cos(2 πν 0 t + θ ) Q θ D R= √ (I 2 +Q 2 ) sin(2 πν 0 t ) cos(2 πν 0 t ) φ =atan2(Q/I) sin cos DDS m n k = ( n k − 1 + N ) mod D register D = 2 m Σ ν 0 = N N D ν s DDC

Vol 21 p.27 11 Phase Noise each sample T ϕ = n noise n i cos θ V 0 V 0 θ (rad) weight t (seconds) avg over τ sampling h ϕ i i τ T s τ = mT s ( m samples) bandwidth B = 1 / 2 τ ⇢⌧ n S ϕ ( f ) = σ 2 � � ϕ V { h ϕ i τ } = V cos θ B V 0 τ σ 2 2 m = E { n 2 } = n 2 mV 2 2 mV 2 ν s 0 0 σ 2 σ 2 = n n = ν s V 2 2 mV 2 0 0 Independent of v 0 =1/T s and of tau The sampling jitter adds up

12 Application to 10 GHz Cryogenic Oscillators Uliss ADC card 횽 A–C φ ADC DDC + 횽 A – 횽 B R Σ FFT 10 τ a GHz φ – 7.03 MHz ADC DDC 횽 B–C AVG beat R τ b Marmotte S φ (ƒ) τ c clock • Rejects the common-path jitter • Takes in the di ff erential jitter

13 Results L(ƒ), dBc/Hz Background (2 channel) TSC5125 Background (4 channel) • Background noise 5–6 dB higher than that of the TSC5125 • We use 2 channel cross spectrum • TSC5125 uses 4 channel cross spectrum

14 The Four-Channel Scheme A ADC card 1 φ A–C ( φ A–B ) 1 ADC DDC + ( 횽 A – 횽 B ) 1 R Σ FFT τ a φ B–C – ADC DDC R τ b cross spectrum S φ (ƒ) τ c AVG clock ADC card 2 φ A–C ( φ A–B ) 2 ADC DDC + R Σ FFT τ a B ( 횽 A – 횽 B ) 2 φ B–C – ADC DDC R τ b τ c

15 Background Noise -40 L(ƒ), dBc/Hz -185 "dif_cross_avg1000.txt" Four-channel scheme -60 "dif_cross_avg1000.dat" "dif_ab_avg1000.dat_2chlimitpybAB" ff -80 i "dif_cha_chb_avg1000.dat" d l e n -100 n a h c -120 1E3 AVG -140 1E6 AVG -160 –185 dBc baseline -180 -200 -220 1 10 100 1000 10000 100000 1e+06

16 Compared to a Commercial Instrument – this is done only to make sure that there is no calibration mistake – -20 L(ƒ), dBc/Hz "sma-agilent-meas.dat" "sma-alazar.dat" u 1:($2-10*log10(2)) -40 Four-channel scheme "sma-datasheet.dat" -60 Measure a Rohde Schwarz synthesizer -80 Agilent Our (Alazartech) -100 -120 -140 -160 -180 -200 1 10 100 1000 10000 100000 1e+06 1e+07

17 Conclusions • White noise • Depends on Fs and ENoB • Fits well the expectation • Flicker –110 dBV 2 /Hz best found • First phase noise measurements, (direct & beat) • Background –185 dBc with 4-channel scheme • Modelling common-mode and di ff erential jitter in progress • Unwanted correlated e ff ects still unknown

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.