Multiplexer Goals Selectors: DEF: A MUX -gate (also known as a (2 : - PowerPoint PPT Presentation

Multiplexer Goals Selectors: DEF: A MUX -gate (also known as a (2 : 1) -multiplexer) is a combinational gate that has three inputs D [0] , D [1] , S and Chapter 5: Selectors and Shifters review definition of multiplexer. one output Y . The

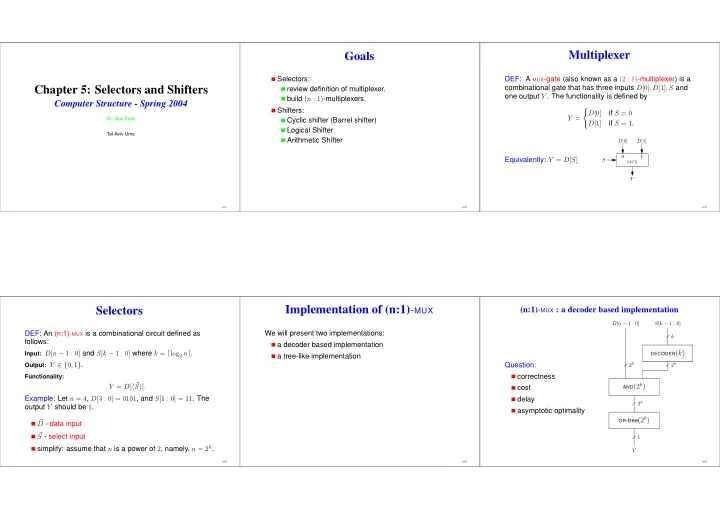

Multiplexer Goals Selectors: DEF: A MUX -gate (also known as a (2 : 1) -multiplexer) is a combinational gate that has three inputs D [0] , D [1] , S and Chapter 5: Selectors and Shifters review definition of multiplexer. one output Y . The functionality is defined by build ( n : 1) -multiplexers. Computer Structure - Spring 2004 Shifters: � D [0] if S = 0 Y = Dr. Guy Even Cyclic shifter (Barrel shifter) D [1] if S = 1 . Logical Shifter Tel-Aviv Univ. Arithmetic Shifter D [0] D [1] 0 1 Equivalently: Y = D [ S ] S mux Y – p.1 – p.2 – p.3 Implementation of (n:1) - MUX Selectors (n:1) - MUX : a decoder based implementation D [ n − 1 : 0] S [ k − 1 : 0] DEF: An (n:1) - MUX is a combinational circuit defined as We will present two implementations: k follows: a decoder based implementation Input: D [ n − 1 : 0] and S [ k − 1 : 0] where k = ⌈ log 2 n ⌉ . DECODER ( k ) a tree-like implementation Output: Y ∈ { 0 , 1 } . Question: 2 k 2 k correctness Functionality: Y = D [ � � AND (2 k ) S � ] . cost Example: Let n = 4 , D [3 : 0] = 0101 , and S [1 : 0] = 11 . The delay 2 k output Y should be 1 . asymptotic optimality OR -tree (2 k ) � D - data input � S - select input 1 simplify: assume that n is a power of 2 , namely, n = 2 k . Y – p.4 – p.5 – p.6

Which design is better? Cyclic shift - example (n:1) - MUX : a tree-like implementation D [ n − 1 : n 2 ] D [ n 2 − 1 : 0] both designs are asymptotically optimal. 12 12 n/ 2 n/ 2 1 1 1 1 1 1 based on the tables of Müller & Paul, the tree-like 12 6 0 1 5 4 8 ( n ( n 0 0 2 : 1) - MUX 2 : 1) - MUX design is better. 2 2 S [ k − 2 : 0] S [ k − 2 : 0] 1 1 1 8 3 2 0 rotate clockwise decision is based on specific gate costs in the 1 1 Y L Y R by 3 positions 12 9 6 1 3 9 7 3 technology one uses. 1 4 9 5 1 0 1 fast MUX -gates in CMOS (transmission gates) do not 8 4 8 4 S [ k − 1] 1 MUX 2 9 3 1 Question: restore the signals well. 7 1 7 5 7 5 ⇒ long paths consisting only of MUX -gates are not correctness 1 6 6 allowed. cost "clock"reads: "clock"reads: Y 5,3,1,11,...,8,10,12 8,10,12,...,2,4,6� delay asymptotic optimality – p.7 – p.8 – p.9 CLS ( n, i ) - Cyclic Left Shift by 2 i positions Cyclic shift - definition Barrel Shifter The string b [ n − 1 : 0] is a cyclic left shift by i positions of the DEF: A BARREL - SHIFTER ( n ) is a combinational circuit defined DEF: A CLS ( n, i ) is a combinational circuit defined as string a [ n − 1 : 0] if as follows: follows: Input: x [ n − 1 : 0] and sa [ k − 1 : 0] where k = ⌈ log 2 n ⌉ . Input: x [ n − 1 : 0] and s ∈ { 0 , 1 } . ∀ j : b [ j ] = a [ mod ( j − i, n )] . Output: y [ n − 1 : 0] . Output: y [ n − 1 : 0] . y is a cyclic left shift of � x by � � sa � positions. Functionality: � Functionality: Example: Let a [3 : 0] = 0010 . A cyclic left shift by one position Formally, y [ j ] = x [ mod ( j − s · 2 i , n )] . ∀ j ∈ [ n − 1 : 0] : of � a is the string 0100 . A cyclic left shift by 3 positions of � a is ∀ j ∈ [ n − 1 : 0] : y [ j ] = x [ mod ( j − � � sa � , n )] . Equivalently, the string 0001 . x - data input � � x [ j ] if s = 0 sa - shift amount input � y [ j ] = x [ mod ( j − 2 i , n )] if s = 1 . simplify - assume that n is a power of 2 , namely, n = 2 k . ⇒ can implement CLS ( n, i ) with a row of n MUX -gates. – p.10 – p.11 – p.12

CLS (4 , 1) BARREL - SHIFTER ( n ) - a chain of CLS ( n, i ) BARREL - SHIFTER ( n ) - correctness x [ n − 1 : 0] Define the strings y i [ n − 1 : 0] , for 0 ≤ i ≤ k − 1 , recursively x [3] x [2] x [1] x [0] as follows: sa [0] cls ( n, 0) y 0 [ n − 1 : 0] ← CLS n, 0 ( x [ n − 1 , 0] , sa [0]) y i +1 [ n − 1 : 0] ← CLS n,i +1 ( y i [ n − 1 , 0] , sa [ i + 1]) sa [1] cls ( n, 1) 1 0 1 0 1 0 1 0 s s s s mux mux mux mux 1 1 1 1 Claim: y k − 1 [ n − 1 : 0] is a cyclic left shift of x [ n − 1 : 0] by y [3] y [2] y [1] y [0] � sa [ k − 1 : 0] � positions. Proof: Induction. k = 0 - trivial because CLS ( n, 0) shifts by sa [ k − 1] cls ( n, k − 1) Evident that a CLS ( n, i ) requires a lot of area for the wires. zero/one position. Our model does not capture routing cost. y [ n − 1 : 0] – p.13 – p.14 – p.15 induction step Logical Shifting - motivation Bi-Directional Logical Shifter - definition Used for shifting binary strings that represent unsigned A LOG - SHIFT ( n ) is a combinational circuit defined as follows: integers in binary representation. y i [ j ] = CLS n,i ( y i − 1 [ n − 1 , 0] , sa [ i ])[ j ] (by definition of y i ) Input: = y i − 1 [ mod ( j − 2 i · sa [ i ] , n )] Shifting to the left by s positions corresponds to x [ n − 1 : 0] ∈ { 0 , 1 } n , (by definition of CLS n,i ). sa [ k − 1 : 0] ∈ { 0 , 1 } k , where k = ⌈ log 2 n ⌉ , and x � · 2 s , 2 n ) . � � y � ← mod ( � � Let ℓ = mod ( j − 2 i · sa [ i ] , n ) . ℓ ∈ { 0 , 1 } . Shifting to the right by s positions corresponds to Ind. Hyp. ⇒ y i − 1 [ ℓ ] = x [ mod ( ℓ − � sa [ i − 1 : 0] � , n ) . Output: y [ n − 1 : 0] ∈ { 0 , 1 } n . Note that � � � x � � Functionality: If ℓ = 1 , then logical left shift as follows: � � y � ← . 2 s mod ( ℓ − � sa [ i − 1 : 0] � , n ) = mod ( j − 2 i · sa [ i ] − � sa [ i − 1 : 0] � , n ) △ sa � : 0] · 0 � � sa � . y [ n − 1 : 0] = x [ n − 1 − � � = mod ( j − � sa [ i : 0] � , n ) . If ℓ = 0 , then logical right shift as follows: Therefore y i [ j ] = x [ mod ( j − � sa [ i : 0] � , n )] , and the claim sa � · x [ n − 1 : � � follows. = 0 � � △ y [ n − 1 : 0] sa � ] . – p.16 – p.17 – p.18

Bi-Directional Logical Shifter - example Bi-Directional Logical Shifter - implementation LBS ( n, i ) - definition Example: Let x [3 : 0] = 0010 . If sa [1 : 0] = 10 and ℓ = 1 , then As in the case of cyclic shifters, we break the task of DEF: An LBS ( n, i ) is a combinational circuit defined as designing a logical shifter into sub-tasks of logical shifts follows: LOG - SHIFT (4) outputs y [3 : 0] = 1000 . If ℓ = 0 , then the output by powers of two. Input: x [ n − 1 : 0] and s, ℓ ∈ { 0 , 1 } . equals y [3 : 0] = 0000 . Loosely speaking, an LBS ( n, i ) is a logical bi-directional Output: y [ n − 1 : 0] . shifter that outputs one of three possible strings: Functionality: Define x ′ [ n − 1 + 2 i : − 2 i ] ∈ { 0 , 1 } n +2 · 2 i as the input shifted to the left by 2 i positions, follows: the input shifted to the right by 2 i positions, or � if n < j ≤ 0 x [ j ] x ′ [ j ] △ the input without shifting. = 0 otherwise. We now formally define this circuit.... The value of the output y [ n − 1 : 0] is specified by y [ j ] = x ′ [ j + ( − 1) ℓ · s · 2 i ] . ∀ j ∈ [ n − 1 : 0] : – p.19 – p.20 – p.21 y [ j ] = x ′ [ j + ( − 1) ℓ · s · 2 i ] A bit-slice of an implementation of LBS ( n, i ) A bit-slice of an implementation of LBS ( n, i ) x ′ [ n − 1 + 2 i : − 2 i ] = 0 2 i · x [ n − 1 : 0] · 0 2 i . x ′ [ j + 2 i ] x ′ [ j − 2 i ] x [ j ] x ′ [ j + 2 i ] x ′ [ j − 2 i ] x [ j ] ℓ - determines if the shift is a left shift or a right shift. If 2 2 2 1 0 2 2 ℓ = 1 then ( − 1) ℓ = − 1 , and the shift is a left shift (since 2 1 0 decoding s, ℓ (3 : 1)- mux decoding s, ℓ (3 : 1)- mux increasing indexes from j − 2 i to j has the effect of a left shift). y [ j ] y [ j ] s - determines if a shift (in either direction) takes place Question: This question deals with various aspects and at all. If s = 0 , then y [ j ] = x [ j ] , and no shift takes place. details concerning the design of a logical shifter. 1. (3 : 1) - MUX . Implemented either by a “pruned” tree-like 1. Design a “pruned” tree-like (3 : 1) - MUX . construction or we can simply consider a (3 : 1) - MUX as a basic gate. Simple circuit ⇒ best option can be easily 2. Design the decoding box. determined based on the technology at hand. 3. Show how LBS ( n, i ) circuits can be cascaded to obtain a 2. decoding circuit - not a decoder! Decoding of s and ℓ LOG - SHIFT ( n ) . causes the (3 : 1) - MUX to select the correct input. Hint: follow the design of a BARREL - SHIFTER ( n ) . – p.22 – p.23 – p.24

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.