Flash Memory Suzhen Wu*, Sijie Lan *, Jindong Zhou*, Hong Jiang, - PowerPoint PPT Presentation

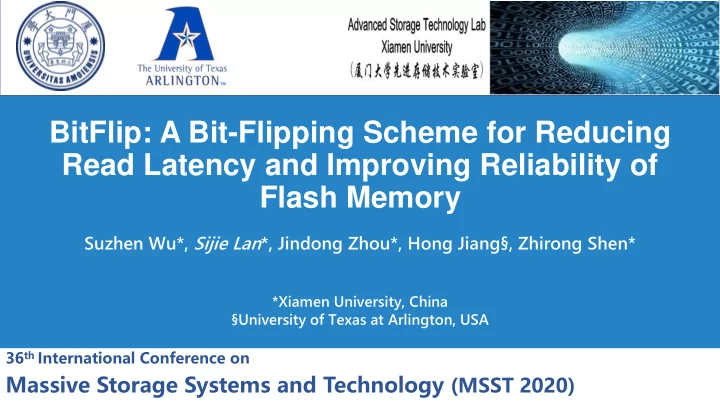

BitFlip: A Bit-Flipping Scheme for Reducing Read Latency and Improving Reliability of Flash Memory Suzhen Wu*, Sijie Lan *, Jindong Zhou*, Hong Jiang, Zhirong Shen* *Xiamen University, China University of Texas at Arlington, USA 36 th

BitFlip: A Bit-Flipping Scheme for Reducing Read Latency and Improving Reliability of Flash Memory Suzhen Wu*, Sijie Lan *, Jindong Zhou*, Hong Jiang§, Zhirong Shen* *Xiamen University, China §University of Texas at Arlington, USA 36 th International Conference on Massive Storage Systems and Technology (MSST 2020)

Ou Outl tline ine • Bac ackgro kground und an and Motivatio ivation • Bit itFli lip p De Desi sign gn • Eval aluatio uation • concl clus usio ion

Ho How w er errors rors occ ccur ur ? • P/E Cyclin ing Erro rors rs • Progr gram am Erro rors rs • Program am Inter erfer erenc ence e Error ors • Reten entio ion n Error ors (domi mina nant nt source e of fl flash h me memo mory ry error ors) • …… Our work focus on the Retention errors

Wh Why re y rete tention ntion er errors rors occ ccur? ur? After multiple erase and program operations, the insulating property Control Gate of tunnel oxide degrade gradually. Gate Oxide Floating Gate So, more electrons leakage Tunnel Oxide happen and more retention Source n+ Drain n+ errors occur. Substrate

Wh Why re y rete tention ntion er errors rors occ ccur? ur? In MLC cell, there are four states which store four kinds of bits respectively. Errors happen.

ECC CC meth ethods ods in in SS SSDs Ds LDPC code tolerate more errors, but more errors cause more sensing level, which degrade performance. The figure above from the work of Zhao et al.

LDPC LD C in in SSD SSDs Start with hard-decision decoding (X=0) Yes Decoding successes? No Level X is the No Soft-decision decoding maximum level in soft- with level X++ decision decoding ? Yes Read Read fails succeeds

Ch Char aracter acterist istic ics s of of re rete tentio ntion n er errors rors Most retention errors are 00->01 (46%), 01->10 (44%). Which means, higher threshold voltages are more likely to leak charge. The figure above from the work of Cai et al.

Fil ile e Ana naly lysis sis In our analysis, the proportion of four kinds of states are quit different in different files.

Motiva tivation tion • So, , highe gher r Vth th (th thre reshold shold volt ltages) ages) means ans higher gher rete tenti tion n erro rors rs. . • Can n we reduce duce th the e sta tate tes s number mber with th higher gher Vth th ? e Bi BitFli tFlip • We desig ign th the character ‘a’ BitFlip 01 00 00 01 10 11 11 10 Data with higher Vth Data with lower Vth Data store with lower Vth states means less errors will occur

Ou Outl tline ine • Ba Background kground and nd Mo Motiv ivati ation on • Bi BitFli lip p De Desi sign gn • Eval aluatio uation • concl nclusio usion

Arc rchitecture hitecture of B f Bit itFlip Flip Host Read Write FTL 1. BitFlip design in FTL 2. Bit counter module: Split a page to equal size BitFlip units. Calculate the state's number of units to Bit counter Reorganization module module determine which unit needs to be flipped 3. Reorganization module: Base on tag-bits, flip the units which need flip, then reorganize (data LDPC decoder LDPC encoder store in Flash) NAND Flash Write data Read data

Wr Write ite proces rocess Host 1.Bit Counter Module: Read Write • Split page to several equal units. • Count states’ number of each unit FTL • Generate tag bit of each unit to mark BitFlip whether it should be flipped Bit counter Reorganization module module Bit Counter Module For each unit Count states Unit Unit LDPC decoder LDPC encoder Unit Yes Tag bit = 1 Sum(00+01)>Sum(10+11)? Unit NAND Flash No Write data Read data Tag bit = 0

Write Wr ite proces rocess Host 2.Reorganization Module: • Judging from tag bits, flip the units and Write Read reorganize the units to a page . FTL BitFlip Bit counter Reorganization Reorganization Module 512 Bytes module module tag bits 1 0 1 0 1 0 1 0 1111 1111 1111 1111 LDPC decoder LDPC encoder Generate units for bit flips NAND Flash Data to be stored in flash after reorganization Write data Read data

Rea ead d proces rocess Host Read Write FTL 1.Reorganization Module: BitFlip • decoding data Bit counter Reorganization • Base on tag bits, flip the units to restore module module original data LDPC decoder LDPC encoder NAND Flash Write data Read data

Wr Write ite A page ‘00’+’01’>’10’+’11’ …… ‘00’+’01’<’10’+’11’ Bit Counter Module 0 1 0 0 1 1 1 1 Count states’ number Tag bits Data area Spare area Flip 01001111 Reorganization Module Reorganize

Rea ead Data area Spare area 01 0 01111 Flip host

Ou Outl tline ine • Ba Backgr kground ound and nd Mo Motiv ivati ation on • Bit itFli lip p De Desi sign gn • Eva valuat luation ion • concl clus usio ion

Eva valuat luation ion Se Setu tup p ➢ Configurations of SSD ➢ Test environment • SSDsim Simulator • We range the RBER from 4e-3 to 13 e-3, ➢ Test on real world files and traces files (MSR)

Red educe uce er error ror-prone prone st stat ates es ➢ BitFlip can reduce about 2.3%-53.9% of the error- prone states for different file types, thereby demonstrating the effectiveness of BitFlip.

Co Comparison mparison on th n the de e deco coding ding le leve vels ls ➢ where BitFlip can reduce 27.1%-31.6% of the decoding levels on average.

Co Comparison mparison on th n the rea e read d la late tency. ncy. ➢ BitFlip can reduce the read latency by 25.9%-34.2% for each trace compared with the baseline approach.

The he nu number ber of P/ f P/E cy cycles cles th that at ca can be n be en endur ured. ed. ➢ BitFlip can increase 2.9%-33.3% of P/E cycles that the flash memory can endure.

Su Summary mmary ➢ BitFlip lip can reduce e the erro ror-pr prone one st states ➢ Comp mparison ison on the de deco codi ding ng levels els • BitFlip can reduce the decoding levels on average. ➢ Comp mparison ison on the read latenc ncy. • By reducing the error-prone states, BitFlip significantly reduce the decoding time needed in read operations. ➢ The numb mber r of P P/E cycles that can be endure red. • BitFlip increase P/E cycles that the flash memory can endure

Thanks! Q&A BitFlip: A Bit-Flipping Scheme for Reducing Read Latency and Improving Reliability of Flash Memory Suzhen Wu*, Sijie Lan *, Jindong Zhou*, Hong Jiang§, Zhirong Shen* *Xiamen University, China §University of Texas at Arlington, USA

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.