Coding Schemes for Inter-Cell Interference in Flash Memory Sarit - PowerPoint PPT Presentation

Coding Schemes for Inter-Cell Interference in Flash Memory Sarit Buzaglo UCSD Joint work with Paul H. Siegel and Eitan Yaakobi Flash Memory and Inter-Cell Interference Flash memory structure: Block of cells: m word lines of length n.

Coding Schemes for Inter-Cell Interference in Flash Memory Sarit Buzaglo UCSD Joint work with Paul H. Siegel and Eitan Yaakobi

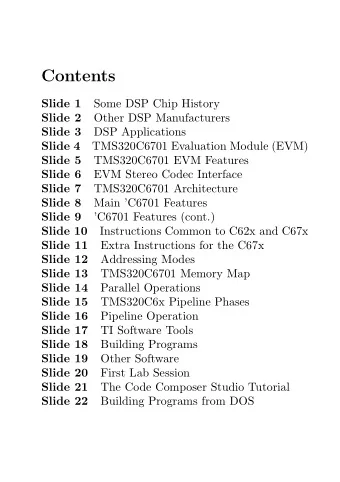

Flash Memory and Inter-Cell Interference • Flash memory structure: – Block of cells: m word lines of length n. – A cell is a floating-gate transistor. The state of the cell is determined by a voltage threshold. – Row-by-row programming. – The cells of a word line are programmed at the same time.

Flash Memory and Inter-Cell Interference • Inter-Cell Interference (ICI) • The pattern “ 101 ” causes more ICI errors when appears along bit line than along word line 1 . 1. V. Taranalli , H. Uchikawa, and P. H. Siegel, “Error Analysis and Inter -Cell Interference Mitigation in Multi- Level Cell Flash Memories,” to appear in Proc. IEEE International Conference on Communications (ICC 2015) , London, UK, June 8 - 12, 2015 .

What is Our Goal? • To design coding scheme s.t.: – Word lines are programmed row-by-row. – All the cell of a word line can be programmed simultaneously. – Program each word line with the same rate. – Avoid bit line ICI errors. – Obviously: rate should be high as possible.

Results • Construction 1: – Row-by-row fixed rate coding scheme that avoids the pattern “ 101 ” along bit line. – The rate asymptotically achieves the rate of the ICI constraint. – The construction is based on the work of Tal et al. 1 for general constraints and uses constant weight codes. 1. I. Tal, T. Etzion, and R. ,Roth, ``On row-by-row coding for 2-D constraints ,'' IEEE Trans. on Information Theory , vol. 55, pp. 3565--3576, 2009.

Results • Construction 2: – Row-by-row fixed rate coding scheme. – M aintains a fixed number of appearances of “ 101 ” along bit lines. – Use ECC to correct the bit line ICI errors. – The rate can be much higher than the rate of the ICI constraint, if the probability of bit line ICI error is small.

Thank you for your attention!!

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.