Combinational Building Blocks Multiplexers Decoders Chapter 2 - PowerPoint PPT Presentation

Combinational Building Blocks Multiplexers Decoders Chapter 2 <155> Multiplexer (Mux) Selects between one of N inputs to connect to output log 2 N -bit required to select input control input S S Example: D 0 0 Y

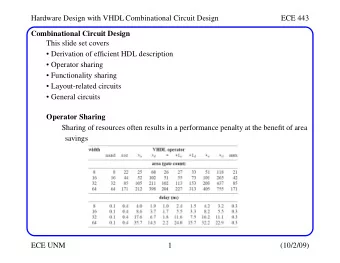

Combinational Building Blocks • Multiplexers • Decoders Chapter 2 <155>

Multiplexer (Mux) • Selects between one of N inputs to connect to output • log 2 N -bit required to select input – control input S S • Example: D 0 0 Y 2:1 Mux (2 inputs to 1 output) D 1 1 • 𝑂 = 2 S D 1 D 0 Y S Y • log 2 2 = 1 control bit required 0 0 0 0 0 D 0 0 0 1 1 1 D 1 0 1 0 0 0 1 1 1 1 0 0 0 1 0 1 0 1 1 0 1 1 1 1 1 Chapter 2 <156>

Multiplexer Implementations • Logic gates • Tristates • • Sum-of-products form For an N-input mux, use N tristates • Turn on exactly one to Y D 0 D 1 select the appropriate 00 01 11 10 S input 0 0 0 1 1 S 1 0 1 1 0 D 0 Y = D 0 S + D 1 S Y D 0 D 1 S D 1 Y 2-<157> Chapter 2 <157>

Logic using Multiplexers • Using the mux as a lookup table A B Y 0 0 0 • Zero outputs tied to GND 0 1 0 1 0 0 • One output tied to VDD 1 1 1 Y = AB A B 00 01 Y 10 11 Chapter 2 <158>

Logic using Multiplexers • Reducing the size of the mux A A Y A B Y 0 0 0 0 0 0 0 1 0 Y Y = AB 1 0 0 1 1 B B 1 1 1 Chapter 2 <159>

Decoders • N inputs, 2 N outputs 2:4 • One-hot outputs: only Decoder one output HIGH at once 11 Y 3 A 1 10 Y 2 A 0 01 Y 1 00 Y 0 • Example 2:4 Decoder (2 inputs to 4 outputs) A 1 A 0 Y 3 Y 2 Y 1 Y 0 • 𝐵 𝑗 decimal value selects the 0 0 0 0 0 1 0 1 0 0 1 0 corresponding output 1 0 0 1 0 0 1 1 1 0 0 0 Chapter 2 <160>

Decoder Implementation A 1 A 0 Y 3 Y 2 Y 1 Y 0 Chapter 2 <161>

Logic Using Decoders • OR minterms 2:4 Decoder Minterm 11 AB A 10 AB B 01 AB 00 AB Y = AB + AB = A B Y XNOR function Chapter 2 <162>

Timing • Delay between input change and output changing A Y delay A Y Time • How to build fast circuits? Chapter 2 <163>

Propagation & Contamination Delay • Propagation delay: t pd = max delay from input to final output • Contamination delay: t cd = min delay from input to initial output change A Y t pd Note: Timing diagram shows a A signal with a high and low and transition time as an ‘X’. Cross hatch indicates Y unknown/changing values t cd Time Chapter 2 <164>

Propagation & Contamination Delay • Delay is caused by • Capacitance and resistance in a circuit • Speed of light limitation • Reasons why t pd and t cd may be different: • Different rising and falling delays • Multiple inputs and outputs, some of which are faster than others • Circuits slow down when hot and speed up when cold Chapter 2 <165>

Critical (Long) & Short Paths Critical Path A n1 B n2 C Y D Short Path Critical (Long) Path: t pd = 2 t pd _AND + t pd _OR Short Path: t cd = t cd _AND Chapter 2 <166>

Glitches • When a single input change causes an output to change multiple times Chapter 2 <167>

Glitch Example • What happens when A = 0, C = 1, B falls? A B Y C Y AB 00 01 11 10 C 0 1 0 0 0 1 1 1 1 0 Y = AB + BC Chapter 2 <168>

Glitch Example (cont.) Critical Path A = 0 0 1 B = 1 0 n1 Y = 1 0 1 n2 C = 1 1 0 Short Path B Note: n1 is slower than n2 n2 because of the extra inverter for B to n1 go through Y glitch Time Chapter 2 <169>

Fixing the Glitch Y AB 00 01 11 10 C 0 1 0 0 0 1 1 1 1 0 Consensus term AC Y = AB + BC + AC A = 0 B = 1 0 Y = 1 C = 1 Chapter 2 <170>

Why Understand Glitches? • Glitches shouldn’t cause problems because of synchronous design conventions (see Chapter 3) • It’s important to recognize a glitch: in simulations or on oscilloscope • Can’t get rid of all glitches – simultaneous transitions on multiple inputs can also cause glitches Chapter 2 <171>

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.