MrDP: Multiple-row Detailed Placement of Heterogeneous-sized Cells - PowerPoint PPT Presentation

MrDP: Multiple-row Detailed Placement of Heterogeneous-sized Cells for Advanced Nodes Yibo Lin 1 Bei Yu 2 Xiaoqing Xu 1 Jhih-Rong Gao 3 Natarajan Viswanathan 3 Wen-Hao Liu 3 Zhuo Li 3 Charles J. Alpert 3 David Z. Pan 1 1 University of Texas at

MrDP: Multiple-row Detailed Placement of Heterogeneous-sized Cells for Advanced Nodes Yibo Lin 1 Bei Yu 2 Xiaoqing Xu 1 Jhih-Rong Gao 3 Natarajan Viswanathan 3 Wen-Hao Liu 3 Zhuo Li 3 Charles J. Alpert 3 David Z. Pan 1 1 University of Texas at Austin 2 The Chinese University of Hong Kong 3 Cadence Design Systems 1 / 28

Outline Introduction Problem Formulation Detailed Placement Algorithms Experimental Results Conclusion 2 / 28

Introduction: Technology Scaling Transistors Patterning Interconnect Complexity [Courtesy ARM] Planar CMOS LE AI / Cu / W wires 2005 2010 2015 2020 2025 3 / 28

Introduction: Technology Scaling Transistors Patterning Interconnect Complexity [Courtesy ARM] LELE FinFET W LI Planar CMOS LE AI / Cu / W wires 2005 2010 2015 2020 2025 3 / 28

Introduction: Technology Scaling Transistors Patterning Interconnect Complexity [Courtesy ARM] LELE FinFET W LI Planar CMOS LE 10 nm 7 nm 5 nm 3 nm AI / Cu / W wires 2005 2010 2015 2020 2025 3 / 28

Introduction: Technology Scaling Opto Connect eNVM EUV DSA EUV LELE Transistors CNT 3D IC VNW Graphene Patterning SAQP EUV EBL Interconnect SADP HNW Complexity LELELE [Courtesy ARM] LELE EUV FinFET W LI Cu Doping Planar CMOS LE 10 nm 7 nm 5 nm 3 nm AI / Cu / W wires 2005 2010 2015 2020 2025 3 / 28

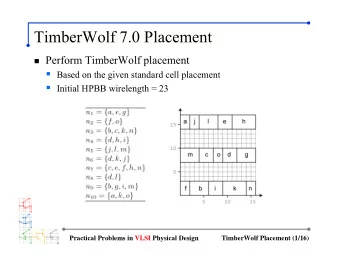

Technology Scaling: Fewer Tracks Track # per row decreases: ◮ From 10 to 7.5 ◮ Exploring 7.5T for 7nm technology node ◮ Even with EUV, additional metal layer may be required (a) And-or-invert (AOI); (b) 2-finger inverter [Liebman+,SPIE’15]. 4 / 28

Motivation of Multiple-Row Cells 1 ◮ Complex standard cells, such as flip-flops, MUXes, etc. ◮ Intra-Cell Routability (a) Cell size 54 grids (b) Cell size 48 grids 5 / 28

Motivation of Multiple-Row Cells 2 Pin access problem [Taghavi+,ICCAD’10] M1 pin V1 M2 V2 M3 Blocked pin Cell 1 Cell 2 Cell 1 Cell 2 (a) (b) (a) pin access failure; (b) pin access success. [Xu+,DAC’14] 6 / 28

Motivation of Multiple-Row Cells 3 Multi-bit flip-flops (MBFF) [Jiang+,ISPD’11] [Pokala+,ASIC’92] 7 / 28

Power Line Alignment Odd-row height cells ◮ Misalignment fixable with vertical flipping Even-row height cells ◮ Misalignment NOT fixable with vertical flipping ◮ New placement techniques are highly necessary VDD GND a e VDD c f g b GND d VDD 8 / 28

Power Line Alignment Odd-row height cells ◮ Misalignment fixable with vertical flipping Even-row height cells ◮ Misalignment NOT fixable with vertical flipping ◮ New placement techniques are highly necessary VDD GND a b e VDD c d f g GND VDD 8 / 28

Power Line Alignment Odd-row height cells ◮ Misalignment fixable with vertical flipping Even-row height cells ◮ Misalignment NOT fixable with vertical flipping ◮ New placement techniques are highly necessary VDD GND a b e VDD c d f g GND VDD 8 / 28

Previous Works Double-row height cells [Wu+,TCAD’15] ◮ Group and extend single-row height cells into double-row height blocks ◮ Re-use existing detailed placement frameworks ◮ Incapable to handle three- and four-row height cells ◮ Power alignment not addressed Legalization for Multiple-row height cells [Chow+,DAC’16] ◮ General to heterogeneous-sized cells ◮ Minimize total displacement while removing overlaps ◮ Power alignment addressed ◮ No performance optimization 9 / 28

Wirelength and Density Metrics Cell Density: ABU [ICCAD’13 Contest] overflow γ = max ( 0 , ABU γ − 1 ) d t � γ ∈ Γ w γ · overflow γ ABU = , Γ ∈ { 2 , 5 , 10 , 20 } � γ ∈ Γ w γ Scaled wirelength (sHPWL) sHPWL = HPWL · ( 1 + ABU ) 10 / 28

Wirelength and Density Metrics Cell Density: ABU [ICCAD’13 Contest] overflow γ = max ( 0 , ABU γ − 1 ) d t � γ ∈ Γ w γ · overflow γ ABU = , Γ ∈ { 2 , 5 , 10 , 20 } � γ ∈ Γ w γ Scaled wirelength (sHPWL) sHPWL = HPWL · ( 1 + ABU ) APU Average Pin Utilization: capture pin distribution of the layout. 10 / 28

Problem Formulation: MrDP Multi-row Detailed Placement (MrDP) Input: ◮ A netlist with heterogeneous-sized cells ◮ Initial placement with fixed macro blocks Output: ◮ Legal placement ◮ Minimize wirelength and density cost, i.e., sHPWL and APU 11 / 28

Conventional Global Move ◮ Pick a cell and move to better position ◮ More difficult with heterogeneous-sized cells a b c d e f g i h j k l m t ? 12 / 28

Conventional Global Move ◮ Pick a cell and move to better position ◮ More difficult with heterogeneous-sized cells a b c d e f g i h j k l m t 12 / 28

Conventional Global Move ◮ Pick a cell and move to better position ◮ More difficult with heterogeneous-sized cells a b c d e f g i t h j k l m 12 / 28

Chain Move ◮ Cell Pool : A queue structure used for temporary storage of cells within a chain move ◮ Scoreboard : Consists of an array of chain move entries with corresponding changes in wirelength cost for each chain move ◮ Inspired by KL and FM algorithms in partitioning [KL’70][FM,DAC’82] ◮ Look for cumulatively good cost c d f g h j k t 13 / 28

Chain Move ◮ Cell Pool : A queue structure used for temporary storage of cells within a chain move ◮ Scoreboard : Consists of an array of chain move entries with corresponding changes in wirelength cost for each chain move ◮ Inspired by KL and FM algorithms in partitioning [KL’70][FM,DAC’82] ◮ Look for cumulatively good cost c d f t h k j g 13 / 28

Chain Move ◮ Cell Pool : A queue structure used for temporary storage of cells within a chain move ◮ Scoreboard : Consists of an array of chain move entries with corresponding changes in wirelength cost for each chain move ◮ Inspired by KL and FM algorithms in partitioning [KL’70][FM,DAC’82] ◮ Look for cumulatively good cost c d f g t h k j 13 / 28

Chain Move ◮ Cell Pool : A queue structure used for temporary storage of cells within a chain move ◮ Scoreboard : Consists of an array of chain move entries with corresponding changes in wirelength cost for each chain move ◮ Inspired by KL and FM algorithms in partitioning [KL’70][FM,DAC’82] ◮ Look for cumulatively good cost Scoreboard c d . . . f g Chain move entry t h j k Cell t : p 0 1 → p 1 , ∆WL Cell g : p 0 2 → p 2 Cell j : p 0 3 → p 3 Cell pool . . . 13 / 28

Chain Move Discussion ◮ Order is important ◮ Max prefix sum of wirelength improvement ◮ Discard long chains Cost for a Cell: cost = ∆ WL · ( 1 + α · c d ) + β · c ov ◮ ∆ WL: wirelength cost ◮ c d : density cost (average of cell and pin densities) ◮ c ov : overlap cost 14 / 28

Chain Move Discussion ◮ Order is important ◮ Max prefix sum of wirelength improvement ◮ Discard long chains Cost for a Cell: cost = ∆ WL · ( 1 + α · c d ) + β · c ov ◮ ∆ WL: wirelength cost ◮ c d : density cost (average of cell and pin densities) ◮ c ov : overlap cost Theorem If the input is legal, then the output is guaranteed legal 14 / 28

Ordered Single-Row (OSR) Placement Well explored for single-row height cells ◮ Free-to-move [Vygen,DATE’98] [Kahng+,ASPDAC’99] ◮ Max displacement [Taghavi+,ICCAD’10] [Lin+,ASPDAC’16] How to deal with multiple-row height cells? f a b d i c e Limited movements by multiple rows. 15 / 28

Ordered Double-Row (ODR) Placement ◮ Extend single-row to double-row placement ◮ Some definitions Double-row region Splitting cells j a b f l e i c d h k m g Crossing cells Partition 1 Partition 2 Partition 3 16 / 28

Problem Formulation: ODR Placement Ordered Double-Row (ODR) Placement Input: ◮ Two rows of cells in a double-row region ◮ Ordered from left to right within each row ◮ Maximum displacement M for each cell ◮ All other cells outside double-row region are fixed Output: ◮ Horizontally shift cells ◮ Optimize HPWL while keep the order of cells within each row 17 / 28

ODR Placement: Ideal Cases ◮ Only double-row splitting cells ◮ No crossing cells ◮ No inter-row connection within double-row region ◮ Solve ideal case optimally Fixed Fixed Independent Independent Independent a b f j l e i c d g h k m Partition 1 Partition 2 Partition 3 18 / 28

Nested Dynamic Programming Fixed Fixed Independent Independent Independent a b f j l e i c d g h k m Partition 1 Partition 2 Partition 3 Outer-level shortest path f i ( e 1 , i 1 ) e 1 i 1 f t ( i 1 , t ) f e ( s, e 1 ) e 2 i 2 t s . . . . . . f e ( s, e k ) f t ( i k , t ) e k i k f i ( e k , i k ) Partition 1 Partition 2 Partition 3 19 / 28

Nested Dynamic Programming Fixed Fixed Independent Independent Independent a b f j l e i c d g h k m Partition 1 Partition 2 Partition 3 Outer-level shortest path Inner-level shortest path f i ( e 1 , i 1 ) e 1 i 1 f i ( e 1 , i 1 ) f t ( i 1 , t ) f 1 g 1 h 1 f e ( s, e 1 ) e 2 i 2 g 2 f 2 h 2 . . . t + s s e 1 s e 1 t i 1 . t i 1 . . . . . . . . . . . g k f e ( s, e k ) f k h k f t ( i k , t ) e k i k f i ( e k , i k ) Partition 1 Partition 2 Partition 3 19 / 28

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.