Mitigating Wordline Crosstalk using Adaptive Trees of Counters - PowerPoint PPT Presentation

Mitigating Wordline Crosstalk using Adaptive Trees of Counters Mohammad Seyedzadeh , Alex Jones, Rami Melhem University of Pi8sburgh Wordline Crosstalk in DRAM DRAM Scaling High Memory Capacity Voltage Fluctua<ons DRAM Cells

Mitigating Wordline Crosstalk using Adaptive Trees of Counters Mohammad Seyedzadeh , Alex Jones, Rami Melhem University of Pi8sburgh

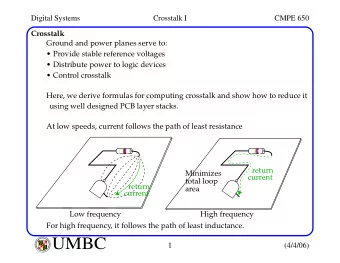

Wordline Crosstalk in DRAM DRAM Scaling ✔ High Memory Capacity ✖ Voltage Fluctua<ons DRAM Cells Deep-scaled DRAM Cells 2 DRCAT: Dynamically Reconfigured Counter based Adaptive Tree

Wordline Crosstalk in DRAM Row of Cells Row of Cells Vic@m Row Wordline Aggressor Row Vic@m Row DRAM Bank DRAM Cells Deep-scaled DRAM Cells 2 DRCAT: Dynamically Reconfigured Counter based Adaptive Tree

Wordline Crosstalk in DRAM Row of Cells Row of Cells Vic@m Row Wordline Aggressor Row Vic@m Row DRAM Bank DRAM Cells Deep-scaled DRAM Cells The malicious exploit of this crosstalk by repeatedly accessing a row to induce this effect is known as • row hammering. 2 DRCAT: Dynamically Reconfigured Counter based Adaptive Tree

Outline • Wordline Crosstalk in DRAM • Probabilistic and Deterministic Solutions • CAT: Counter based Adaptive Tree • Evaluation • Conclusion 3 DRCAT: Dynamically Reconfigured Counter based Adaptive Tree

Wordline Crosstalk in DRAM: Related Work Probabilis<c Determinis<c Approach Approach Deep-scaled DRAM Cells Probabilistic Row Activation (PRA) Static Counter Assignment (SCA) 4 DRCAT: Dynamically Reconfigured Counter based Adaptive Tree

Probabilistic Row Activation (PRA) Probabilis<c Approach RNG(p) Deep-scaled DRAM Cells • Using a Random Number Generator to refresh the vic@m rows with the probability of ‘p’. 5 DRCAT: Dynamically Reconfigured Counter based Adaptive Tree

Probabilistic Row Activation (PRA) Refresh Threshold (T) 32k 24k 16k 8k 1.E+00 PRA Failure Probability PRA Unsurvivability 1.E-04 for 5 Years 1.E-08 for 5 years 1.E-12 1.E-16 1.E-20 1.E-24 1.E-28 p=0.001 p=0.002 p=0.003 p=0.004 p=0.005 p=0.006 Chipkill Pseudo Random Number Generator (PRNG) LFSR-based RNG Refresh threshold: # of aggressor row accesses before read disturbance errors occur in vic@m rows. 6 DRCAT: Dynamically Reconfigured Counter based Adaptive Tree

Probabilistic Row Activation (PRA) Refresh Threshold (T) 32k 24k 16k 8k 1.E+00 PRA Failure Probability PRA Unsurvivability 1.E-04 for 5 Years 1.E-08 for 5 years 1.E-12 1.E-16 1.E-20 1.E-24 1.E-28 p=0.001 p=0.002 p=0.003 p=0.004 p=0.005 p=0.006 Chipkill LFSR-based RNG Refresh threshold: # of aggressor row accesses before read disturbance errors occur in vic@m rows. 6 DRCAT: Dynamically Reconfigured Counter based Adaptive Tree

Probabilistic Row Activation (PRA) Refresh Threshold (T) 32k 24k 16k 8k 1.E+00 PRA Failure Probability PRA Unsurvivability 1.E-04 for 5 Years 1.E-08 for 5 years 1.E-12 1.E-16 1.E-20 1.E-24 1.E-28 p=0.001 p=0.002 p=0.003 p=0.004 p=0.005 p=0.006 Chipkill LFSR-based RNG Refresh threshold: # of aggressor row accesses before read disturbance errors occur in vic@m rows. 6 DRCAT: Dynamically Reconfigured Counter based Adaptive Tree

Static Counter Assignment (SCA) C 0 C 0 . . . . . . . . . C m C n . . . C N-1 Deep-scaled DRAM Cells Deep-scaled DRAM Cells e P s o w c i e e r r t P o m r a e i n w t a i n o P i n g h s C e o Power to maintaining r u f n Conservative e t e R r s Refresh Power Counters 7 DRCAT: Dynamically Reconfigured Counter based Adaptive Tree

Static Counter Assignment (SCA) Counters (Sta:c+Dynamic) Counters (Sta:c+Dynamic) Counters (Sta:c+Dynamic) Refresh Refresh Refresh Total (refresh+counter energy) Total (refresh+counter energy) Total (refresh+counter energy) 1.E+07 1.E+07 1.E+07 1.E+06 1.E+06 1.E+06 Energy (nJ) Energy (nJ) Energy (nJ) 1.E+05 1.E+05 1.E+05 Unu<lized Counters 1.E+04 1.E+04 1.E+04 1.E+03 1.E+03 1.E+03 1.E+02 1.E+02 1.E+02 1.E+01 1.E+01 1.E+01 1.E+00 1.E+00 1.E+00 16 16 16 32 32 32 64 64 64 128 128 128 256 256 256 512 512 512 1024 1024 1024 2048 2048 2048 4096 4096 4096 8192 8192 8192 16384 16384 16384 32768 32768 32768 65536 65536 65536 # of Counters # of Counters # of Counters • Non-uniform row access pa8erns in DRAM banks because of data locality 8 DRCAT: Dynamically Reconfigured Counter based Adaptive Tree

How to Efficiently Leverage Counters in the Crosstalk Mitigation? 8 DRCAT: Dynamically Reconfigured Counter based Adaptive Tree

Our Solution: Counter-based Adap@ve Tree (CAT) Row Address Ac@ve Counter Expired Counter DRAM BANK (N rows) × 10 4 × 10 4 × 10 4 × 10 4 × 10 4 × 10 4 × 10 4 10 10 10 10 10 10 10 Access Frequency Access Frequency Access Frequency Access Frequency Access Frequency Access Frequency Access Frequency 8 8 8 8 8 8 8 6 6 6 6 6 6 6 4 4 4 4 4 4 4 2 2 2 2 2 2 2 0 0 0 0 0 0 0 0 0 0 1 1 1 2 2 2 3 3 3 4 4 4 5 5 5 6 6 6 0 0 1 1 2 2 3 3 4 4 5 5 6 6 0 1 2 3 4 5 6 0 1 2 3 4 5 6 Row Address Row Address Row Address Row Address Row Address × 10 4 × 10 4 × 10 4 × 10 4 × 10 4 Row Address × 10 4 Row Address × 10 4 9 DRCAT: Dynamically Reconfigured Counter based Adaptive Tree

Our Solution: Counter-based Adap@ve Tree (CAT) Row Address Ac@ve Counter Expired Counter DRAM BANK (N rows) × 10 4 × 10 4 × 10 4 × 10 4 × 10 4 × 10 4 × 10 4 10 10 10 10 10 10 10 Access Frequency Access Frequency Access Frequency Access Frequency Access Frequency Access Frequency Access Frequency 8 8 8 8 8 8 8 6 6 6 6 6 6 6 4 4 4 4 4 4 4 2 2 2 2 2 2 2 0 0 0 0 0 0 0 0 0 1 1 2 2 3 3 4 4 5 5 6 6 0 0 0 0 0 1 1 1 1 1 2 2 2 2 2 3 3 3 3 3 4 4 4 4 4 5 5 5 5 5 6 6 6 6 6 Row Address Row Address × 10 4 × 10 4 Row Address Row Address Row Address Row Address Row Address × 10 4 × 10 4 × 10 4 × 10 4 × 10 4 10 DRCAT: Dynamically Reconfigured Counter based Adaptive Tree

CAT: Counter based Adaptive Tree ² PRCAT: Periodically Reset CAT Ø Burst Refresh Mechanism Ø Reset CAT at the end of each refresh Interval ² DRCAT: Dynamically Reconfigured CAT Ø Distributed Refresh Mechanism Ø Reconfigure CAT during consecutive refresh intervals 11 DRCAT: Dynamically Reconfigured Counter based Adaptive Tree

PRCAT: Periodically Reset CAT C0 Burst Refresh 64ms 64ms 12 DRCAT: Dynamically Reconfigured Counter based Adaptive Tree

PRCAT: Periodically Reset CAT I0 C1 C0 Burst Refresh 64ms 64ms 12 DRCAT: Dynamically Reconfigured Counter based Adaptive Tree

PRCAT: Periodically Reset CAT I0 I1 C0 I2 I3 C1 I4 C3 C6 I5 C4 C2 C5 Burst Refresh 64ms 64ms 12 DRCAT: Dynamically Reconfigured Counter based Adaptive Tree

PRCAT: Periodically Reset CAT I0 I1 C0 I2 I3 C1 I4 C3 I6 C6 C7 I5 C4 C2 C5 Burst Refresh 64ms 64ms 12 DRCAT: Dynamically Reconfigured Counter based Adaptive Tree

PRCAT: Periodically Reset CAT C0 I0 I1 C0 I2 I3 C1 I4 C3 I6 C6 C7 I5 C4 C2 C5 Reset CAT Burst Refresh 64ms 64ms 12 DRCAT: Dynamically Reconfigured Counter based Adaptive Tree

PRCAT: Periodically Reset CAT C0 Build CAT from the Root Reset CAT Burst Refresh 64ms 64ms 12 DRCAT: Dynamically Reconfigured Counter based Adaptive Tree

DRCAT: Dynamically Reconfigured CAT I0 I1 C0 I2 I3 C1 I4 C3 I6 C6 C7 I5 C4 C2 C5 Distributed Refresh 64ms 64ms 12 DRCAT: Dynamically Reconfigured Counter based Adaptive Tree

DRCAT: Dynamically Reconfigured CAT I0 I1 C0 I2 I3 C1 I4 C3 I6 C6 C6 C7 I5 C4 C2 C2 C5 C5 Distributed Refresh 64ms 64ms 13 DRCAT: Dynamically Reconfigured Counter based Adaptive Tree

DRCAT: Dynamically Reconfigured CAT I0 I1 C0 I2 I3 C1 I4 C3 I6 I5 C7 C5 I5 C4 C2 C6 Distributed Refresh 64ms 64ms 13 DRCAT: Dynamically Reconfigured Counter based Adaptive Tree

DRCAT: Dynamically Reconfigured CAT W C I I0 I0 I1 I0 I1 C0 1 0 C0 0 C0 I1 C0 I1 I2 I3 1 1 C1 0 I2 I3 I2 I3 I2 C1 I4 0 1 C2 1 M-1 I3 C3 I6 0 1 C3 1 I4 I6 C1 C3 M C1 I4 C3 I6 I4 C5 C4 0 0 C4 0 I5 C5 C4 C7 I5 C6 C2 0 0 C5 0 I5 C7 C5 I5 C4 I6 I5 C7 1 0 C6 1 C6 C2 C2 C6 L-ptr R-ptr L-leaf R-leaf C7 1 (a) (b) (c) (d) • During each row access, the tree structure is traversed sequen@ally by chasing the pointers to find the counter assigned to a specific row address. 13 DRCAT: Dynamically Reconfigured Counter based Adaptive Tree

Experimental Settings USIMM Simulator: Two 3.2GHz cores, 2 channels(each 8GB DIMM), 1 rank/ channel 8 banks/rank, 64K rows/bank Synopsys Design Compiler Power Overhead Performance Overhead PARSEC, SPEC, Commercial and Biobench Kernel Malicious A8ack 14 DRCAT: Dynamically Reconfigured Counter based Adaptive Tree

Power Overhead 30% Probabilis<c Row Ac<va<on Sta<c Counter Assignment 25% PRCAT DRCAT 20% 15% 10% 5% 0% com1 com2 com3 com4 com5 swapt fluid str black ferret face MTC MTF libq leslie mum <gr Mean freq COMM PARSEC SPEC BIO Power overhead for DRCAT in dual-core systems is 4.5%, which is an improvement over the 12% and • 13% incurred in PRA and SCA. 15 DRCAT: Dynamically Reconfigured Counter based Adaptive Tree

Performance Overhead 4% Probabilis<c Row Ac<va<on Sta<c Counter Assignment 3% PRCAT DRCAT 2% 1% 0% com1 com2 com3 com4 com5 swapt fluid str black ferret face freq MTC MTF libq leslie mum <gr Mean COMM PARSEC SPEC BIO • DRCAT, PRCAT and PRA incur very low performance overhead (<0.5%). 16 DRCAT: Dynamically Reconfigured Counter based Adaptive Tree

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.