Metal-Density Driven Placement for CMP Variation and Routability - PowerPoint PPT Presentation

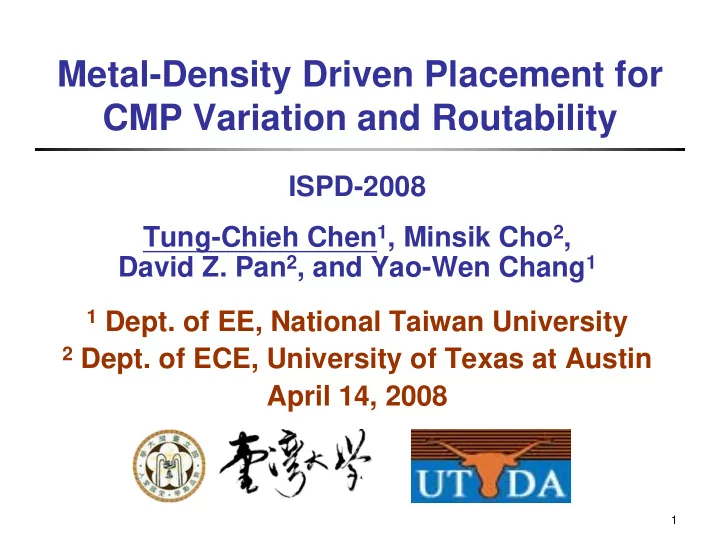

Metal-Density Driven Placement for CMP Variation and Routability ISPD-2008 Tung-Chieh Chen 1 , Minsik Cho 2 , David Z. Pan 2 , and Yao-Wen Chang 1 1 Dept. of EE, National Taiwan University 2 Dept. of ECE, University of Texas at Austin April 14,

Metal-Density Driven Placement for CMP Variation and Routability ISPD-2008 Tung-Chieh Chen 1 , Minsik Cho 2 , David Z. Pan 2 , and Yao-Wen Chang 1 1 Dept. of EE, National Taiwan University 2 Dept. of ECE, University of Texas at Austin April 14, 2008 1

Outline • Introduction • Review of NTUplace3 • Metal-density driven placement • Experimental results • Conclusion 2

Placement • Fundamental VLSI problems ⎯ Placement ⎯ Routing • Significant impact on VLSI Placement ⎯ Wirelength � Performance ⎯ Routability � Routing complete rate Routing ⎯ Manufacturability � Topography variation after CMP 3

Chemical Mechanical Polishing (CMP) • CMP: Key multilevel metallization technique in deep submicron design • CMP variation ⎯ Performance degradation due to increase resistance ⎯ Printability issues due to non-uniform surface (depth-of-focus) ⎯ Systematic variation due to non-uniform metal density distribution (dummy fills) 4

Placement Objectives • Placement is a fundamental VLSI physical synthesis problem ⎯ Wirelength-driven placement ⎯ Timing-driven placement ⎯ Routability-driven placement ⎯ Cell-density driven placement Metal-density has never been considered! 5

Metal-Density Driven Placement • Metal-density driven routing was studied by Cho et al., in ICCAD-2006. ⎯ The average CMP variation is reduced by 7.5%. ⎯ Metal density is highly related to placement since the metal density optimization in routing is often limited by pin locations. • Effectively distributing pins and cells into a placement region with metal density consideration can provide better flexibility for routing, leading to better wire density topography. 6

Outline • Introduction • Review of NTUplace3 • Metal-density driven placement • Experimental results • Conclusion 7

NTUplace3 • T.-C. Chen, Z.-W. Jiang, T.-C. Hsu, H.-C. Chen and Y.-W. Chang, "A high-quality mixed-size analytical placer considering preplaced blocks and density constraints" [ICCAD-2006] • NTUplace3 ⎯ Handles preplaced blocks and density constraints ⎯ Is based on the multilevel framework ⎯ Uses an analytical model ⎯ Obtained the best average placement quality based on the results reported in [Viswanathan et al., DAC- 2007] (Was tied with RQL.) 8

Placement with Density Constraint • Given the chip region and block dimensions, divide the placement region into bin grids • Determine (x, y) for all movable blocks min W(x, y) -- wirelength function 1. Density b (x, y) ≤ MaximumDensity b s.t. for each bin b 2 . No overlap between blocks A block Density = bins A bin 9

Multilevel Global Placement Cluster the blocks based on Iteratively decluster the connectivity/size to reduce clusters and further the problem size. refine the placement Initial placement declustering & refinement clustering declustering clustering & refinement clustered block chip boundary 10

Analytical Placement Model • Global placement problem (allow overlaps) min W( x, y ) Minimize HPWL D b ( x, y ) ≤ D b max s.t. D b : density for bin b max : max density for bin b D b • Relax the constraints into the objective function W( x, y ) + λ Σ (D b ( x, y ) – D b max ) 2 min ⎯ Use the gradient method to solve it ⎯ Increase λ gradually to find the optimal (x, y) 11

Spreading 12 enough! STOP! Placement Process Increase density weight Increase density weight

Outline • Introduction • Review of NTUplace3 • Metal-density driven placement • Experimental results • Conclusion 13

Framework Move cells to reduce Placement metal density variation. Database 5 1 2 Predictive Wire Density Analytical CMP model Estimator Placer 3 4 Wire Density / Metal Density 14

Wire Density Estimator • Wire density of a bin is computed by the number of track go through the bin boundary and the internal routing in the bin. • To predict the predict track usage, we decompose multi-terminal nets into Steiner trees using FLUTE. [Chu, ISPD04] • Track usage is estimated by the probabilistic routing model. [Lou, Thakur, and Krishnamoorthy, TCAD02] T T 1/5 2/5 3/5 1/5 1/5 1/5 2/5 1/5 1/5 1/5 2/5 1/5 1/5 1/5 S 3/5 2/5 1/5 S 15

Predictive CMP Model • A fast CMP model is desired ⎯ Use the predictive CMP model [ICCAD-2007] • Cu thickness is systematically dependent on metal density • Metal density = wire density + dummy fill density • Wire density � Dummy fill � Metal density 16

Concept of Reducing Metal Density • Move cells out from high • Result in more uniform metal-density regions. metal density. • Add forces to blocks in high metal-density regions. 17

Metal-Density Driven Placement Formulation min W • v M b metal density in the D b ≤ D b s.t. max vertical routing layer v ≤ M b v,max M b h M b metal density in the h ≤ M b h,max M b horizontal routing layer • Relax all constraints to objective function may cause instability of the solver and may not converge to a feasible solution. v – M b W + λ 1 Σ (D b – D b max ) 2 + λ 2 Σ (M b v,max ) 2 min h – M b + λ 3 Σ (M b h,max ) 2 • Instead, we solve the following equation to ensure the stability: max maximum combined D’ b W + λ Σ (D b – D’ b density (preplaced density max ) 2 min + metal density) 18

Computing Maximum Combined Density max = target_utilization(1.0 – combined_density) D’ b combined_density = preplaced_density + scaled_metal_density v – min M b v ) + s 2 (M b h – min M b h ) scaled_metal_density = s 1 ( M b 0 0.2 0.4 0.6 0.8 1 + = Preplaced block density Scaled metal density Combined density 19

Density Smoothing • A smooth objective function helps the gradient method to find a desired solution. Level smoothing Gaussian smoothing • Three smoothing parameters ⎯ k gradually increases to the user-specified whitespace ratio ⎯ σ controls the range of the Gaussian smoothing (15% to 1%) ⎯ δ controls the degree of level smoothing (5 to 1) 20

Flow • Loop 1 (L1) ⎯ Multilevel Loop 2 (L2) • ⎯ Objective function Loop 3 (L3) • ⎯ Solver Update smoothing parameters; • The metal density is updated inside the L3, and the base potential Estimate wire and metal density; Update combined density; is updated accordingly. The smoothing • parameters are updated in L2. 21

Outline • Introduction • Review of NTUplace3 • Metal-density driven placement • Experimental results • Conclusion 22

Experiment Setup • CPU: AMD Opteron 2.2GHz • Benchmarks: adaptec from ISPD ’ 06 • Placement: NTUplace3 (ICCAD ’ 06) • Routing: BoxRouter (DAC ’ 06,ICCAD ’ 07) • Routing configurations (from ISPD ’ 07) ⎯ Six metal layers; 20% tracks available in metal 1 and metal 2 ⎯ Block porosity: the reaming routing resource above the macros • Predictive CMP model for computing Cu thickness B.P.: macro block porosity 23

Placement Techniques Compared � Wirelength-driven placement (WLD) ⎯ Minimize wirelength ⎯ Target utilization = 1.0 � Cell-density driven placement (CDD) ⎯ Evenly distribute cells over the chip ⎯ Target utilization = design density � Metal-density driven placement (MDD) ⎯ Spread cells to minimize metal density variation ⎯ Set max k = 90% to use 90% whitespace for metal density optimization 24

25 Results � � �

Result Summary CMP Routability Place Thickness Dummy Total Routing CPU variation fills Overflow CPU time WLD 1.12 1.06 30,399 33.42 0.81 CDD 1.03 1.02 903 4.67 0.92 MDD 1.00 1.00 0 1.00 1.00 26

Metal-Density Map for adaptec5 Vertical Routing Layer � WLD: Cu-Std = 5.70 � CDD: Cu-Std = 4.54 � MDD: Cu-Std = 4.45 Horizontal Routing Layer � WLD: Cu-Std = 5.73 � CDD: Cu-Std = 4.58 � MDD: Cu-Std = 4.52 27

Outline • Introduction • Review of NTUplace3 • Metal-density driven placement • Experimental results • Conclusion 28

Conclusion • Presented the first metal-density driven placement ⎯ Predictive CMP model ⎯ Metal-density-aware cell spreading ⎯ Density smoothing • Compared with the wirelength-driven placement, we ⎯ Reduced the copper thickness variation by 12% ⎯ Reduced the dummy fills by 6% • Results also led to higher routability ⎯ Less overflow ⎯ Less routing time 29

30 Thank You! Questions?

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.