Memory Virtualization: Paging Speed Prof. Patrick G. Bridges 1 - PowerPoint PPT Presentation

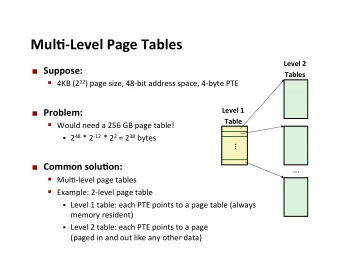

University of New Mexico Memory Virtualization: Paging Speed Prof. Patrick G. Bridges 1 University of New Mexico Speeding up Translation with a TLB Page table entries (PTEs) are cached in L1 like any other memory word PTEs may be

University of New Mexico Memory Virtualization: Paging Speed Prof. Patrick G. Bridges 1

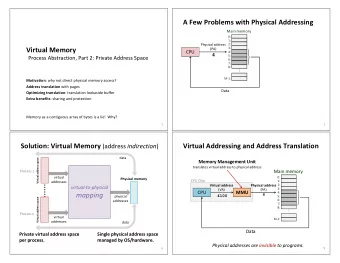

University of New Mexico Speeding up Translation with a TLB Page table entries (PTEs) are cached in L1 like any other memory word ▪ PTEs may be evicted by other data references ▪ PTE hit still requires a small L1 delay Solution: Translation Lookaside Buffer (TLB) ▪ Small set-associative hardware cache in MMU ▪ Maps virtual page numbers to physical page numbers ▪ Contains complete page table entries for small number of pages 2

University of New Mexico TLB Part of the chip’s memory -management unit(MMU). A hardware cache of popular virtual-to-physical address translation. TLB MMU TLB Hit Lookup Physical Logical TLB Address Address popular v to p TLB Miss Page 0 Page Table CPU Page 1 all v to p entries Page 2 … Page n Address Translation with MMU Physical Memory 3

University of New Mexico Accessing the TLB MMU uses the VPN portion of the virtual address to access the TLB: T = 2 t sets VPN TLBT matches tag of n-1 p+t p+t-1 p p-1 0 line within set TLB tag (TLBT) TLB index (TLBI) VPO Set 0 v tag PTE v tag PTE TLBI selects the set Set 1 v tag PTE v tag PTE … Set T-1 v tag PTE v tag PTE 4

University of New Mexico TLB Hit CPU Chip TLB PTE 2 3 VPN 1 VA PA CPU MMU Cache/ 4 Memory Data 5 A TLB hit eliminates a memory access 5

University of New Mexico TLB Miss CPU Chip TLB 4 2 PTE VPN 1 3 VA PTEA CPU MMU Cache/ PA Memory 5 Data 6 A TLB miss incurs an additional memory access (the PTE) Fortunately, TLB misses are rare. Why? 6

University of New Mexico Example: Accessing An Array How a TLB can improve its performance. OFFSET 00 04 08 12 16 VPN = 00 0: int sum = 0 ; VPN = 01 1: for( i=0; i<10; i++){ VPN = 03 2: sum+=a[i]; VPN = 04 3: } VPN = 05 VPN = 06 a[0] a[1] a[2] The TLB improves performance VPN = 07 a[3] a[4] a[5] a[6] due to spatial locality VPN = 08 a[7] a[8] a[9] 3 misses and 7 hits. VPN = 09 Thus TLB hit rate is 70%. VPN = 10 VPN = 11 VPN = 12 VPN = 13 VPN = 14 VPN = 15 7

University of New Mexico Who Handles The TLB Miss? Option 1: Hardware handles the TLB miss (x86, ARM). ▪ The hardware has to know exactly where the page tables are located in memory. ▪ The hardware would “walk” the page table, find the correct page - table entry and extract the desired translation, update and retry instruction. ▪ Hardware specifies the exact format of the page table! ▪ Hardware-managed TLB. 8

University of New Mexico Who Handles The TLB Miss? (Cont.) Option 2: Software-managed TLB (MIPS, some others) ▪ On a TLB miss, the hardware raises exception( trap handler ). ▪ Trap handler is code within the OS that is written with the express purpose of handling TLB miss. ▪ Allows for much wider range of page table organizations 9

University of New Mexico TLB entry TLB is generally a small fully associative cache . ▪ A typical TLB might have 32, 64, or 128 entries. ▪ Hardware search the entire TLB in parallel to find the desired translation. ▪ other bits: valid bits , protection bits, address-space identifier, dirty bit VPN PFN other bits Typical TLB entry look like this 10

University of New Mexico Issue: Context Switching and Shared TLB TLB is a hardware structure shared by all processes Page 0 Insert TLB Entry Page 1 TLB Table Page 2 VPN PFN valid prot access VPN10 … Process A 10 100 1 rwx Page n - - - - Virtual Memory - - - - - - - - Page 0 Page 1 Process B Page 2 … Page n Virtual Memory 11

University of New Mexico TLB Issue: Context Switching Page 0 Page 1 TLB Table Page 2 … Process A VPN PFN valid prot Page n 10 100 1 rwx Virtual Memory - - - - Context 10 170 1 rwx Switching - - - - Page 0 Insert TLB Entry Page 1 access VPN10 Process B Page 2 … Can’t Distinguish which entry is Page n meant for which process Virtual Memory 12

University of New Mexico Options Flush TLB on context switch 1. Provide an address space identifier (ASID) field in the TLB. 2. Page 0 Page 1 TLB Table Page 2 VPN PFN valid prot ASID Process A … 10 100 1 rwx 1 Page n - - - - - Virtual Memory 10 170 1 rwx 2 Page 0 - - - - - Page 1 Process B Page 2 … Page n Virtual Memory 13

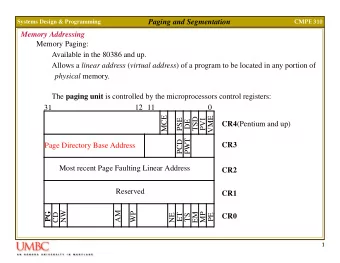

University of New Mexico Simple Memory System Example Addressing ▪ 14-bit virtual addresses ▪ 12-bit physical address ▪ Page size = 64 bytes 13 12 11 10 9 8 7 6 5 4 3 2 1 0 VPN VPO Virtual Page Offset Virtual Page Number 11 10 9 8 7 6 5 4 3 2 1 0 PPN PPO Physical Page Number Physical Page Offset 14

University of New Mexico 1. Simple Memory System TLB 16 entries 4-way associative TLBT TLBI 13 12 11 10 9 8 7 6 5 4 3 2 1 0 VPN VPO Set Tag PPN Valid Tag PPN Valid Tag PPN Valid Tag PPN Valid 0 03 – 0 09 0D 1 00 – 0 07 02 1 1 03 2D 1 02 – 0 04 – 0 0A – 0 2 02 – 0 08 – 0 06 – 0 03 – 0 3 07 – 0 03 0D 1 0A 34 1 02 – 0 15

University of New Mexico 2. Simple Memory System Page Table Only show first 16 entries (out of 256) VPN PPN Valid VPN PPN Valid 00 28 1 08 13 1 01 – 0 09 17 1 02 33 1 0A 09 1 03 02 1 0B – 0 04 – 0 0C – 0 05 16 1 0D 2D 1 06 – 0 0E 11 1 07 – 0 0F 0D 1 16

University of New Mexico 3. Simple Memory System Cache 16 lines, 4-byte block size Physically addressed Direct mapped CT CI CO 11 10 9 8 7 6 5 4 3 2 1 0 PPN PPO Idx Tag Valid B0 B1 B2 B3 Idx Tag Valid B0 B1 B2 B3 0 19 1 99 11 23 11 8 24 1 3A 00 51 89 1 15 0 – – – – 9 2D 0 – – – – 2 1B 1 00 02 04 08 A 2D 1 93 15 DA 3B 3 36 0 – – – – B 0B 0 – – – – 4 32 1 43 6D 8F 09 C 12 0 – – – – 5 0D 1 36 72 F0 1D D 16 1 04 96 34 15 6 31 0 – – – – E 13 1 83 77 1B D3 7 16 1 11 C2 DF 03 F 14 0 – – – – 17

University of New Mexico Address Translation Example #1 Virtual Address: 0x03D4 TLBT TLBI 13 12 11 10 9 8 7 6 5 4 3 2 1 0 0 0 0 0 1 1 1 1 0 1 0 1 0 0 VPN VPO VPN ___ TLBI ___ TLBT ___ TLB Hit? __ Page Fault? __ PPN: ____ 0x0F 0x3 0x03 Y N 0x0D Physical Address CT CI CO 11 10 9 8 7 6 5 4 3 2 1 0 0 0 1 1 0 1 0 1 0 1 0 0 PPN PPO CO ___ CI__ CT ___ Hit? __ Byte: ____ 0 0x5 0x0D Y 0x36 18

University of New Mexico Address Translation Example #2 Virtual Address: 0x0020 TLBT TLBI 13 12 11 10 9 8 7 6 5 4 3 2 1 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 VPN VPO VPN ___ TLBI ___ TLBT __ TLB Hit? __ Page Fault? __ PPN: ____ 0x00 0 0x00 N N 0x28 Physical Address CT CI CO 11 10 9 8 7 6 5 4 3 2 1 0 1 0 1 0 0 0 1 0 0 0 0 0 PPN PPO CO___ CI___ CT ____ Hit? __ Byte: ____ 0 0x8 0x28 N Mem 19

University of New Mexico Address Translation Example #3 Virtual Address: 0x0020 TLBT TLBI 13 12 11 10 9 8 7 6 5 4 3 2 1 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 VPN VPO 0x00 0 0x00 N N 0x28 VPN ___ TLBI ___ TLBT ____ TLB Hit? __ Page Fault? __ PPN: ____ Physical Address CT CI CO 11 10 9 8 7 6 5 4 3 2 1 0 1 0 1 0 0 0 1 0 0 0 0 0 PPN PPO 0 0x8 0x28 N Mem CO___ CI___ CT ____ Hit? __ Byte: ____ 20

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.