Memory Memory Decoders M bits M bits RWM NVRWM ROM S 0 S 0 - PDF document

Memory Memory Decoders M bits M bits RWM NVRWM ROM S 0 S 0 Word 0 Word 0 S 1 Word 1 Word 1 A 0 S 2 Storage Storage Random Non-Random Word 2 Word 2 N Words Cell A 1 Cell EPROM Mask-Programmed Decoder Access Access E 2 PROM

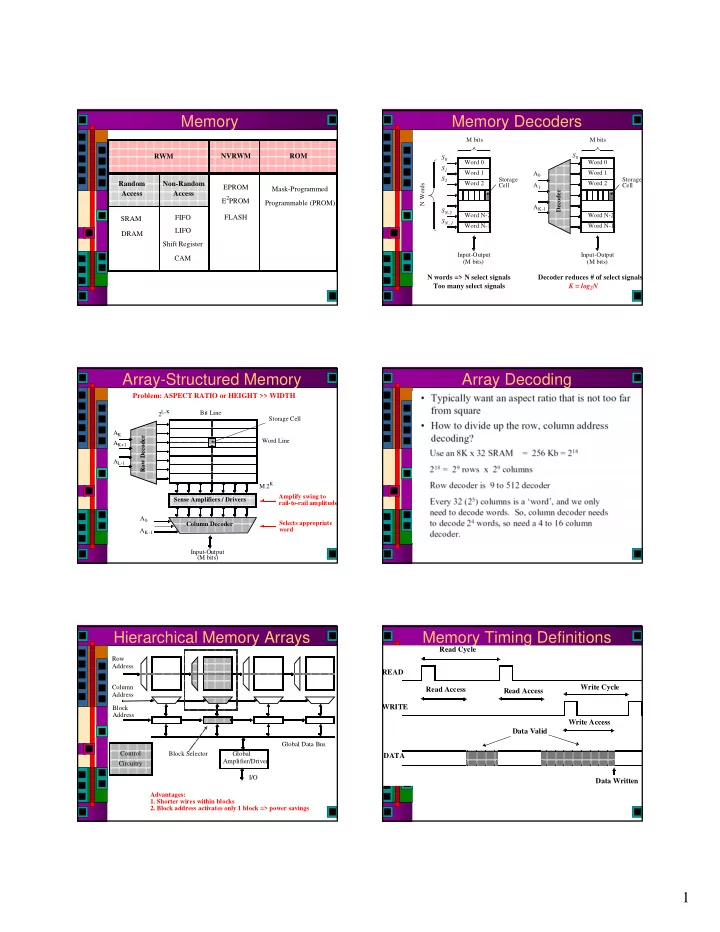

Memory Memory Decoders M bits M bits RWM NVRWM ROM S 0 S 0 Word 0 Word 0 S 1 Word 1 Word 1 A 0 S 2 Storage Storage Random Non-Random Word 2 Word 2 N Words Cell A 1 Cell EPROM Mask-Programmed Decoder Access Access E 2 PROM Programmable (PROM) A K-1 S N-2 Word N-2 Word N-2 FIFO FLASH SRAM S N_1 Word N-1 Word N-1 LIFO DRAM Shift Register Input-Output Input-Output CAM (M bits) (M bits) N words => N select signals Decoder reduces # of select signals Too many select signals K = log 2 N Array-Structured Memory Array Decoding Problem: ASPECT RATIO or HEIGHT >> WIDTH 2 L-K Bit Line Storage Cell A K Row Decoder Word Line A K+1 A L-1 M.2 K Amplify swing to Sense Amplifiers / Drivers rail-to-rail amplitude A 0 Selects appropriate Column Decoder word A K-1 Input-Output (M bits) Hierarchical Memory Arrays Memory Timing Definitions Read Cycle Row Address READ Write Cycle Column Read Access Read Access Address WRITE Block Address Write Access Data Valid Global Data Bus Control Block Selector Global DATA Amplifier/Driver Circuitry I/O Data Written Advantages: 1. Shorter wires within blocks 2. Block address activates only 1 block => power savings 1

Memory Timing Approaches Example: HM6264 8kx8 SRAM MSB LSB Address Row Address Column Address Bus RAS Address Address Bus Address transition CAS initiates memory operation RAS-CAS timing DRAM Timing SRAM Timing Multiplexed Adressing Self-timed HM6264 Interface Function Table Timing Read Cycle 1 2

Read Cycle 1 Read Cycle 2 85ns min 85ns max 85ns max 10ns min 30ns min 85ns max 10ns min 45ns max 30ns min 5ns min 30ns min 10ns min Read Cycle 2 Write Timing 85ns max 10ns min 10ns min Write Cycle Write Cycle 85ns min 75ns min 0ns min 75ns min 55ns min 0ns min 0ns min, 30ns max 40ns min 0ns min 3

What Does All This Mean R/W Memories In General • STATIC (SRAM) � For a read: Data stored as long as supply is applied � If you assert CS1, CS2, address, and OE all Large (6 transistors/cell) at the same time, it will be max 85ns before Fast valid data are available at chip outputs Differential � For a write: � You can assert CS1, CS2, address, data, and WE all at the same time if you want to • DYNAMIC (DRAM) � You need to wait 55ns from WE edge, or Periodic refresh required 75ns from CS1/CS2 edge for write to have Small (1-3 transistors/cell) happened Slower Single Ended SRAM Circuits SRAM Cell, Transistors SRAM, Resistive Pullups Array-Structured Memory Problem: ASPECT RATIO or HEIGHT >> WIDTH 2 L-K Bit Line Storage Cell A K Row Decoder Word Line A K+1 A L-1 M.2 K Amplify swing to Sense Amplifiers / Drivers rail-to-rail amplitude A 0 Selects appropriate Column Decoder word A K-1 Input-Output (M bits) 4

Memory Column Reading the Bit � Each column has all the support circuits � Single-ended read using an inverter � Dynamic pre-charge on the bit lines � P-types pull bit lines high Reading the Bit 2 Reading the Bit 3 � Single-ended read using an inverter � Differential read using sense amp � Dynamic pre-charge on the bit lines � Static N-type pullup on the bit lines � Note the N-types used as pull-ups Read Waveforms Sense Amp 5

Sense Amp Transistors Column Organization Write Circuits Write Circuit Simulation 0 Analog Sim, Circuit Analog Analysis, Write WL WL V DD V DD M 4 M 2 M 4 Q = 0 M 6 Q Q = 1 M 5 M 6 Q M 5 M 1 V DD BL = 1 BL = 0 M 1 M 3 BL BL V DD 2 V DD 2 V DD V DD (W / L ) n,M 6 ≥ 0.33 ( W / L ) p,M 4 ⎛ ⎞ ⎛ ⎞ ( ) - - - - - - - - - - - ( ) - - - - - - - - - - - k n M6 V DD – V Tn – - - - - - - - - - - - = k p M4 V DD – V Tp – - - - - - - - - - - - ⎝ ⎠ ⎝ ⎠ , 2 , 2 8 8 k n M5 V DD 2 V DD 2 - V DD V DD , ⎛ ⎛ ⎞ ⎞ ⎛ ⎞ ( ) (W / L ) n,M 5 ≥ 10 ( W / L ) n,M 1 - - - - - - - - - - - - - - - - - - - - - - - – V Tn - - - - - - - - - - - = k n M1 V DD – V Tn - - - - - - - - - - - – - - - - - - - - - - - ⎝ ⎝ ⎠ ⎠ , ⎝ ⎠ 2 2 2 2 8 6

Analog Analysis, Read 6T SRAM Layout WL V DD M 4 BL BL Q = 0 M 6 M 5 Q = 1 M 1 V DD V DD V DD C bit C bit k n M5 V DD 2 V DD 2 , - V DD V DD ⎛ ⎛ ⎞ ⎞ ⎛ ⎞ -- - -- - -- -- - - -- - - -- - -- - -- - - ( ) -- -- - - -- - -- - -- - -- - -- - -- - – V Tn = k n M1 V DD – V Tn – - - -- - -- - -- - - ⎝ ⎝ ⎠ ⎠ , ⎝ ⎠ 2 2 2 2 8 (W / L ) n,M 5 ≤ 10 ( W / L ) n,M 1 (supercedes read constraint) Another 6T SRAM Layout SRAM bit from makemem (v1) SRAM bit from makemem (v2) Array-Structured Memory Problem: ASPECT RATIO or HEIGHT >> WIDTH 2 L-K Bit Line Storage Cell A K Row Decoder Word Line A K+1 A L-1 M.2 K Amplify swing to Sense Amplifiers / Drivers rail-to-rail amplitude A 0 Selects appropriate Column Decoder word A K-1 Input-Output (M bits) 7

Row Decoders Row Decoder Gates � Standard gates � Or, pseudo-nmos gates with static pull up � Select exactly one of the memory rows � Easier to make large fan-in NOR � Simple versions are just gates Pre-decode Row Decoder Pre-decode Row Decoder � Multiple levels of decoding can be more efficient layout � Other circuit tricks for building row decoders… Array-Structured Memory Array-Structured Memory Problem: ASPECT RATIO or HEIGHT >> WIDTH 2 L-K Bit Line Storage Cell A K Row Decoder Word Line A K+1 A L-1 M.2 K Amplify swing to Sense Amplifiers / Drivers rail-to-rail amplitude A 0 Selects appropriate Column Decoder word A K-1 Input-Output (M bits) 8

Sharing Sense Amps Sense Amp Mux Sense Amp Mux Decoded Column Decode Improving Speed, Power Multi-Port Memory � Very common to require multiple read ports � Think about a register file, for example 9

Multi-Port Register Register File Re1 Re0 � Slightly larger cell, but with single-ended � Slightly larger cell, but with single-ended read – makes a great register file read – makes a great register file Dynamic RAM Dynamic RAM… � Once you agree to use a capacitor for charge storage � Get rid of the pull-ups! there are other � Store info on capacitors ways to build � Means that stored information leaks away this… 3T DRAM Circuit 3T DRAM Layout BL 1 BL 2 BL2 BL1 GND WWL WWL RWL RWL RWL M3 X M 3 V DD -V T X M2 M 2 V DD M 1 BL 1 C S Δ V BL 2 V DD -V T WWL M1 No constraints on device ratios Reads are non-destructive Value stored at node X when writing a “1” = V WWL -V Tn 10

1 T DRAM Circuit 2-T (1-T) DRAM layout � Note the increased gate size of the storage transistor � Increases the capacitance 1T DRAM Observations 1T DRAM Read/Write BL 1T DRAM requires a sense amplifier for each bit line, due to WL Write "1" Read "1" charge redistribution read-out. WL DRAM memory cells are single ended in contrast to SRAM cells. M 1 C S X V DD − V T GND The read-out of the 1T DRAM cell is destructive; read and refresh operations are necessary for correct operation. V DD BL Unlike 3T cell, 1T cell requires presence of an extra capacitance sensing V DD /2 V DD /2 C BL that must be explicitly included in the design. When writing a “1” into a DRAM cell, a threshold voltage is lost. This charge loss can be circumvented by bootstrapping the Write: C S is charged or discharged by asserting WL and BL. Read: Charge redistribution takes places between bit line and storage capacitance word lines to a higher value than V DD . C S Δ V ( ) - - -- - -- - -- - -- -- - - -- - -- - - = V BL – V PRE = V BIT – V PRE C S + C BL Voltage swing is small; typically around 250 mV. 1T DRAM Cell Array of DRAM Cells “Folded Bit Line” “Folded bit line” 11

Reading a 1T DRAM Cell DRAM Sense Amp Charge Sharing Photo of 1T DRAM Advanced DRAM Cells Try to get more capacitance per unit area… Trench Capacitor Examples of Advanced DRAMs Memory Timing Approaches MSB LSB Word line Capacitor dielectric layer Cell plate Insulating Layer Address Row Address Column Address Bus Address Cell Plate Si RAS Address Bus Transfer gate Isolation Capacitor Insulator Refilling Poly Storage electrode Address transition CAS initiates memory operation Storage Node Poly Si Substrate 2nd Field Oxide RAS-CAS timing DRAM Timing SRAM Timing Self-timed Multiplexed Adressing Trench Cell Stacked-capacitor Cell 12

DRAM Interface Extended Data Out Page Mode Comments on Timing Architectural Issues SDRAM - Use CAS for Bursts DDR SDRAM � Double Data Rate 13

DRAM Timing RAMBUS DRAM (RDRAM) RDRAM Bandwidth Maximum Bandwidth Normal Bus for DRAM DIMMs RDRAM Bus 14

Deep Pipelining - High Latency RDRAM Addressing Row Activate Command RDRAM System Arch RDRAM Internal Arch Regular DRAM 15

Single Bank DRAM Multi-Bank DRAM Peak Bandwidth ROM ROM ROM V DD Pull-up devices WL [0] GND WL [1] WL [2] GND WL [3] BL [0] BL [1] BL [2] BL [3] 16

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.