Input Output Patrick Happ Raul Queiroz Feitosa Parts of these - PowerPoint PPT Presentation

Input Output Patrick Happ Raul Queiroz Feitosa Parts of these slides are from the support material provided by W. Stallings Objective This chapter presents concepts, structures and functions involved in I/O operation. 2 Input Output

Input Output Patrick Happ Raul Queiroz Feitosa Parts of these slides are from the support material provided by W. Stallings

Objective This chapter presents concepts, structures and functions involved in I/O operation. 2 Input Output

Outline I/O Modules I/O Techniques Programmed I/O Interrupt driven I/O Direct Memory Access (DMA) I/O Channels and I/O Processors 3 Input Output

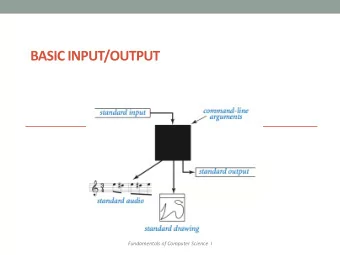

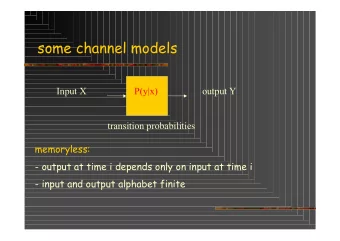

Generic Model of I/O Module Wide variety of peripherals Delivering different amounts of data At different speeds In different formats Most of them slower than CPU and RAM Need I/O modules as interface to CPU and Memory via bus or central switch to one or more peripherals 4 Input Output

External Device Block Diagram 5 Input Output

I/O Module Function Control & Timing 1. CPU Communication 2. Device Communication 3. Data Buffering 4. Error Detection 5. 6 Input Output

I/O Module Function Control & Timing : The data transfer will typically involve the following steps: a) CPU checks I/O module device status b) I/O module returns status c) If ready, CPU requests data transfer d) I/O module gets data from device d) I/O module transfers data from CPU e) I/O module transfers data to CPU e) I/O module sends data to device 7 Input Output

I/O Module Function Processor Communication : involves the following steps: Command decoding: typically word commands are sent a) through the bus to the I/O module. Data: exchanged between cpu and I/O module through b) the bus. Status reporting: because peripherals are slow the cpu c) must know the status of the I/O module – is it ready to receive one more data unit ? Address recognition: I/O modules are accessed quite in d) the same way as memory locations 8 Input Output

I/O Module Function Device Communication Commands, status information and data INTERFACE TO EXTERNAL DEVICE Data INTERFACE TO SYSTEM BUS Data registers External Status device Data interface lines Control logic Status/control registers . . . . . . Data Address External External lines I/O Status device device logic interface interface Control Control logic logic lines BLOCK DIAGRAM OF AN I/O MODULE 9 Input Output

I/O Module Function Data Buffering to cope with the different transfer rates between memory and peripheral devices. Error Detection and reporting to the processor 10 Input Output

Outline I/O Modules I/O Techniques Programmed I/O Interrupt driven I/O Direct Memory Access (DMA) I/O Channels and I/O Processors 11 Input Output

Input Output Techniques Task I/O Technique Read Status Data Transfer 1. Programmed I/O CPU CPU I/O module CPU 2. Interrupt driven I/O 3. Direct Memory Access (DMA) DMA module DMA module 12 Input Output

Programmed I/O busy waiting 13 Input Output

Programmed I/O CPU has direct control over I/O Sensing status Read/write commands Transferring data CPU waits for I/O module to complete operation Wastes CPU time Simplest implementation 14 Input Output

I/O Commands CPU issues address Identifies module (& device if >1 per module) Very like memory accesses with separated or common address spaces CPU issues command Control - telling module what to do e.g. spin up disk Test - check status e.g. power? Error? CPU reads/writes information Module transfers data via buffer from/to device 15 Input Output

I/O Mapping Memory mapped I/O Devices and memory share a common address space I/O looks just like memory read/write No special commands for I/O Large selection of memory access commands available Isolated I/O Separate address spaces Need I/O or memory select lines Special commands for I/O Limited set 16 Input Output

Memory Mapped I/O 516 same instruction to 517 access memory ADDRESS INSTRUCTION OPERAND COMMENT “1” 200 Load AC Load accumulator Store AC 517 Initiate keyboard read 202 Load AC 517 Get status byte Branch if Sign=0 202 Loop until ready Load AC 516 Load data byte 17 Input Output

Isolated I/O 5 specific instructions to 6 access … I/O... ADDRESS INSTRUCTION OPERAND COMMENT “1” 200 Load AC Load accumulator Out 6 Initiate keyboard read 202 In 6 Get status byte Branch if Sign=0 202 Loop until ready In 5 Load data byte 18 Input Output

I/O Mapping INTERFACE TO EXTERNAL DEVICE Data INTERFACE TO SYSTEM BUS Data registers External Status device Data interface lines Control logic Status/control registers . . . . . . Data Address External External lines I/O Status device device logic interface interface Control logic logic RD WR Control memory read lines i/o read memory write i/o write up → memory mapped I/O down → isolated I/O BLOCK DIAGRAM OF AN I/O MODULE 19 Input Output

Interrupt Driven I/O Overcomes CPU waiting No repeated CPU checking of device I/O module interrupts when ready 20 Input Output

Interrupt Driven I/O 21 Input Output

Simple Interrupt Processing 22 Input Output

On Interrupt Acknowledge T-M control stack Processor acknowledges 1. T N+1 interrupt request, while N+1 N+1 Y program executing instruction at counter start Y interrupt location N . service routine return Y+L Processor saves current 2. PC and register contents program . general user’s registers N Processor loads the entry 3. program N+1 T-M T T+1 location of the interrupt- stack handling program . pointer Main Processor Memory 23 Input Output

On Interrupt Return T-M control stack Processor retrieves saved T 1. N+1 N+1 Y+L register contents from the program stack . counter start Y interrupt service Processor retrieves saved 2. routine return Y+L PC and PSW from the stack . general user’s registers N program N+1 T-M T T+1 stack pointer Main Processor Memory 24 Input Output

Design Issues How do you identify the module issuing 1. the interrupt? How do you deal with multiple interrupts? 2. i.e. an interrupt handler being interrupted 25 Input Output

Identifying Interrupting Module (1) Different line for each module PC Limits number of devices Software poll CPU asks each module in turn Slow 26 Input Output

Identifying Interrupting Module (2) Daisy Chain or Hardware poll Interrupt Acknowledge ( ≈ read access) sent down a chain, or parallel to all devices. Module responsible places vector on bus CPU uses vector to identify handler routine Bus Master Module must claim the bus before it can raise interrupt e.g. PCI & SCSI 27 Input Output

Direct Memory Access Drawbacks with previous I/O strategies : both require active CPU intervention Transfer rate is limited CPU is tied up DMA is the answer! Additional Module (hardware) on bus DMA controller takes over from CPU for I/O 28 Input Output

Direct Memory Access 29 Input Output

DMA controller diagram Data registers DMA request External device Data DMA interface lines acknowledge logic Status/control registers Status/control registers Address . . Address . . registers lines . . interrupt request request DMA Control memory read External DMA request Control lines i/o read device logic memory write DMA interface i/o write acknowledge logic 30 Input Output RD WR

DMA Operation CPU tells DMA controller: DMA controller command registers Read/Write Device address Starting address of memory block for data Amount of data to be transferred CPU carries on with other work DMA controller deals with transfer DMA controller sends interrupt when finished 31 Input Output

DMA transfer modes block mode cycle stealing DMA controller DMA controller takes over bus takes over bus till a whole bock till a whole bock is transferred is transferred DMA controller DMA controller transfer one word transfer one word DMA controller DMA controller return bus return bus control control 32 Input Output

DMA transfer modes In block mode as well as in cycle stealing CPU is suspended, not interrupted CPU does not switch context CPU suspended just before it accesses bus i.e. before an operand or data fetch or a data write Slows down CPU but not as much as CPU doing transfer. 33 Input Output

DMA and Interrupt Breakpoints During an Instruction Cycle 34 Input Output

DMA Configurations (1) (a) Single-bus, detached DMA Single Bus, Detached DMA controller 35 Input Output

DMA Configurations (2) (b) Single-bus, Integrated DMA-I/O Single Bus, Integrated DMA – I/Ocontroller Controller may support >1 device 36 Input Output

DMA Configurations (3) (c) I/O Bus Separate I/O Bus Bus supports all DMA enabled devices 37 Input Output

Outline I/O Modules I/O Techniques Programmed I/O Interrupt driven I/O Direct Memory Access (DMA) I/O Channels and I/O Processors 38 Input Output

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.