Impact of Gate Placement on RF Degradation in GaN HEMTs Jungwoo Joh - PowerPoint PPT Presentation

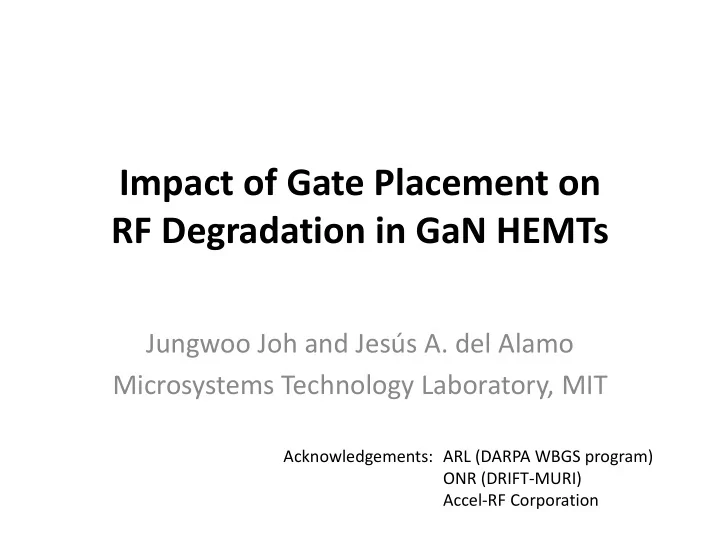

Impact of Gate Placement on RF Degradation in GaN HEMTs Jungwoo Joh and Jess A. del Alamo Microsystems Technology Laboratory, MIT Acknowledgements: ARL (DARPA WBGS program) ONR (DRIFT MURI) Accel RF Corporation Motivation RF

Impact of Gate Placement on RF Degradation in GaN HEMTs Jungwoo Joh and Jesús A. del Alamo Microsystems Technology Laboratory, MIT Acknowledgements: ARL (DARPA WBGS program) ONR (DRIFT ‐ MURI) Accel ‐ RF Corporation

Motivation • RF reliability – main concern in GaN HEMT RF power amplifier • Compared to DC stress, little known about degradation mechanisms Increasing T under RF stress – P out ↓ , Gain ↓ – I D ↓ , dispersion ↑ , g m ↓ , |I G | ↑ – RF introduces more degradation than DC [Conway, IRPS 2007; Joh, ROCS 2008; Chini, IEDM 2009; Joh, IEDM 2010] • Goal: – Develop methodology for RF reliability studies Chini, IEDM 2009 – Identify dominant RF degradation mechanisms 2 – Correlate RF and DC reliability

Experimental Setup Accel ‐ RF AARTS RF10000 ‐ 4/S system: Accel ‐ RF System • two 2 ‐ 4 GHz channels Hardware DC/Pulsed • two 7 ‐ 12 GHz channels Characterization DUT Switching Matrix • Max P in =30 dBm ‐ KeithleySources ‐ Agilent B1500A • T base =50 ‐ 200 ° C Heater RF/DC Units T base Windows ‐ based PC MIT RF/DC Accel ‐ RF Software Characterization Suite ‐ RF measurement ‐ DC FOMs ‐ Temperature control ‐ Current collapse ‐ Stressing Accel ‐ RF system augmented with: • external instrumentation for DC/pulsed characterization • software to control external instrumentation and extract DC and RF FOMs 3

RF Experiment Flowchart: Conventional Approach Limitations: START • Bias point shifts during stress T stress • Limited RF characterization RF Stress • No DC characterization P out , PAE, Gain, I DQ , I GQ • No trap characterization • If examining different RF conditions, RF characterization END confusing 4

RF Experiment Flowchart: Improved Approach START Short characterization: • – Every few minutes at T base =50 ° C Detrapping – DC FOMs: I Dmax , R S , R D , V T , I Goff , … – RF FOMs @ V DS =28 V & I DQ =100 Full Characterization (DC, RF, CC) mA/mm RT • Saturated conditions (P in =23 dBm): P out,sat , G sat , PAE Short Characterization (DC, RF) • Linear conditions (P in =10 dBm): G lin T base =50°C • Full Characterization: RF (DC) Stress – After key events at room temperature T stress – Full DC I ‐ V sweep – Current collapse (after 1” V DS =0, V GS = ‐ Key 10 V pulse) Event? YES NO – Full RF power sweep @ V DS =28 V, I DQ =100 mA/mm END: detrapping + Detrapping: T base =100 ° C for 30 mins • Full characterization 5

P in Step ‐ Stress: Centered Gate • Motivation: – higher P in larger V waveform at output • MMIC: – single ‐ stage internally ‐ matched – 4x100 μ m GaN HEMT – Gate placed at the center btw S & D 14 25 Gain 12 20 10 Gain (dB) • Step P in stress: PAE (%) 15 8 PAE 6 – V DS = 40 V, I DQ = 100 mA/mm 10 4 – P in = 0 (DC), 1, 20 ‐ 27 dBm 5 2 V DS =40 V, I DQ =100 mA/mm – 300 min stress at each step 0 0 – T stress =50 ° C 10 15 20 25 30 6 P in (dBm)

Characterization during RF Stress P in P out P out 30 33 START 25 32 Detrapping 20 P out (dBm) P in (dBm) 15 31 Full Characterization (DC, RF, CC) 10 RT 30 5 Short Characterization (DC, RF) DC DC T base =50°C 0 29 0 10 20 30 40 50 60 0 10 20 30 40 50 60 Time (hr) Time (hr) RF (DC) Stress PAE I DQ T stress Gain 400 30 Key 25 Event? YES NO 300 20 I DQ (mA/mm) 200 PAE (%) END: detrapping + 15 Full characterization 100 10 0 5 -100 0 0 20 40 60 0 10 20 30 40 50 60 Time (hr) Time (hr) • RF FOMs changing because P in changing • Degradation apparent but not easily quantifiable 7

DC FOM during Short Characterization DC|P in =1 20 21 22 23 24 25 26 27 dBm START 1.2 1.E+01 1.E+00 Detrapping I Dmax /I Dmax (0), R/R(0) I Goff 1.1 |I Goff | (mA/mm) Full Characterization (DC, RF, CC) 1.E-01 R D RT 1.E-02 Short Characterization (DC, RF) 1 T base =50°C R S 1.E-03 RF (DC) Stress T stress 1.E-04 0.9 Key I Dmax 1.E-05 Event? YES NO T base =50 ° C 0.8 1.E-06 END: detrapping + 0 1000 2000 3000 Full characterization Time (min) • Little degradation under DC and low P in • Beyond P in =20 dBm: — RF induces degradation of I Dmax and R D — Sharp degradation in I Goff 8

DC/RF/CC Full Characterization 9 33 Permanent I Dmax Degradation (%) T base =RT 8 START 7 Current Collapse (%) Saturated P out (dBm) 32 P out Detrapping 100 °C 6 Full Characterization (DC, RF, CC) 5 RT 31 Current 4 Short Characterization (DC, RF) Collapse T base =50°C 3 DC RF RF (DC) Stress 30 2 T stress Initial 1 Key Δ |I Dmax | Event? YES NO 0 29 END: detrapping + ‐ 10 0 10 20 30 Full characterization Stress Input Power P in (dBm) • Similar critical behavior. Beyond P in =20 dBm: ― Sharp P out degradation ― permanent degradation of I Dmax ― Evidence of new traps created (increased CC) 9

Structural Degradation (Planar View) AFM SEM • Pit formation along the drain side of gate edge • Same degradation mechanism as in DC high field OFF ‐ state 10

Correlation between DC and RF FOM 32.5 Short characterization @ 50 ° C 32 P out (dBm) 31.5 31 30.5 30 V DS =28 V, T base =50 C 650 700 750 800 850 I Dmax (mA/mm) • Good correlation between P out and I Dmax degradation Δ P out =1 dB ↔ Δ I Dmax =9% 11

Step P in Stress: Offset Gate RF FOM DC FOM 32.5 DC RF P in =20 23 26 dBm 3 1.E+01 15 DC RF P in =20 23 26 dBm Small Signal Gain G lin (dB) 32 2.5 Saturated P out (dBm) I Dmax /I Dmax (0), R/R(0) Inner loop (50°C) R S 1.E+00 14.5 |I Goff | (mA/mm) 2 31.5 Gain 1.5 1.E-01 14 R D 31 P out 1 I Dmax 1.E-02 13.5 30.5 0.5 I Goff Inner loop (50°C) 0 1.E-03 30 13 0 300 600 900 1200 0 300 600 900 1200 Time (min) Time (min) Joh, IEDM 2010 • More degradation under RF stress @ high P in • No I Goff degradation (high V crit ) • Degradation in I Dmax and R S , not in R D • No structural degradation 12

Pulsed Stress: High ‐ power State 1.4 100 pulses, 500 us, 0.05% duty I Dpulse =950 mA/mm 1.3 Normalized R S I D Offset gate High-power 1.2 1.1 RF Load Line Centered gate 1 V DS 0 20 40 60 80 Stress V DS (V) • High ‐ power stress not accessible in DC pulsed stress • Pulsed stress reproduces large R S degradation in offset gate • No R S degradation in centered gate 13

Summary • Developed new RF reliability testing methodology • Critical behavior in RF stress on centered gate : – P in ↑ P out ↓ (>> DC stress) – I Dmax ↓ , current collapse ↑ , I Goff ↑ – Good correlation between DC and RF FOMs – Structural degradation on drain ‐ side gate edge – Same degradation mechanism under high ‐ voltage OFF ‐ state DC stress • Offset gate : – Different degradation mechanism is present – Significant R S degradation 14

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.