FPGA language ( HDL ). Overview 3 4 Component-Based Software - PDF document

11/05/2016 Agenda The topics that will be addressed are: Overview on basic characteristics of the FPGA; Scheduling tasks on Reconfigurable FPGA reconfiguration capabilities; FPGA architectures Timing analysis for reconfigurable

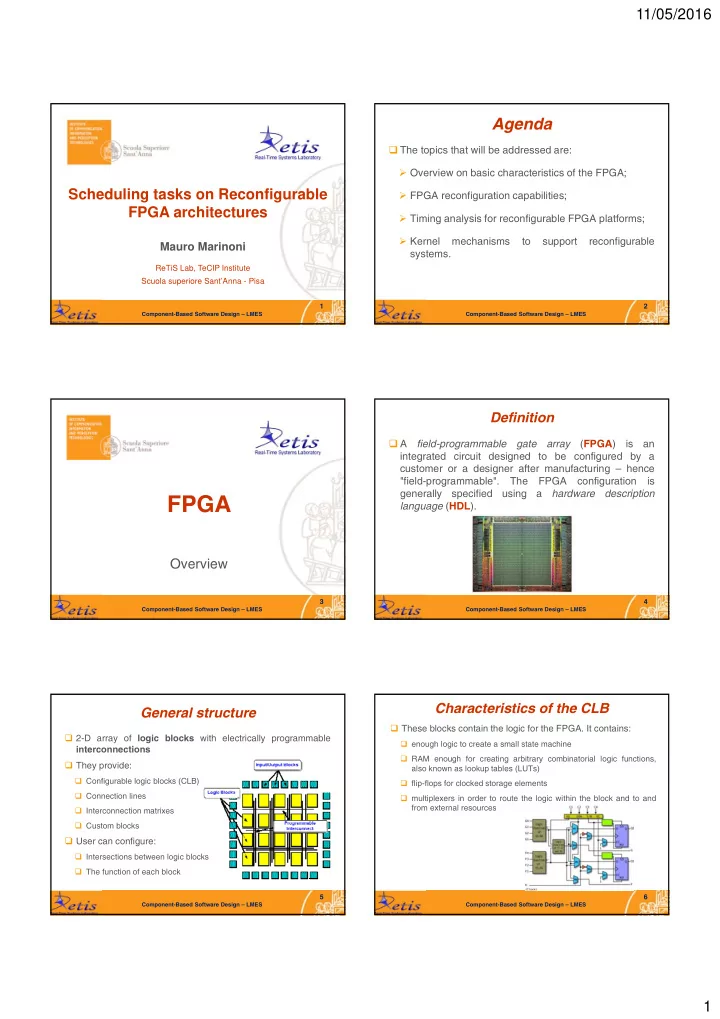

11/05/2016 Agenda The topics that will be addressed are: Overview on basic characteristics of the FPGA; Scheduling tasks on Reconfigurable FPGA reconfiguration capabilities; FPGA architectures Timing analysis for reconfigurable FPGA platforms; Kernel mechanisms to support reconfigurable Mauro Marinoni systems. ReTiS Lab, TeCIP Institute Scuola superiore Sant’Anna - Pisa 1 2 Component-Based Software Design – LMES Component-Based Software Design – LMES Definition A field-programmable gate array ( FPGA ) is an integrated circuit designed to be configured by a customer or a designer after manufacturing – hence "field-programmable". The FPGA configuration is generally specified using a hardware description FPGA language ( HDL ). Overview 3 4 Component-Based Software Design – LMES Component-Based Software Design – LMES Characteristics of the CLB General structure These blocks contain the logic for the FPGA. It contains: 2-D array of logic blocks with electrically programmable enough logic to create a small state machine interconnections RAM enough for creating arbitrary combinatorial logic functions, They provide: also known as lookup tables (LUTs) Configurable logic blocks (CLB) flip-flops for clocked storage elements Connection lines multiplexers in order to route the logic within the block and to and from external resources Interconnection matrixes Custom blocks User can configure: Intersections between logic blocks The function of each block 5 6 Component-Based Software Design – LMES Component-Based Software Design – LMES 1

11/05/2016 Pros and Cons Performances Advantages FPGAs excel at computing non-data dependent algorithms in Performance: Online analysis of high-rate data streams parallel . Reliability: Deterministic hardware dedicated to every task Customizable data path and ALU allow very large amounts Reconfigurability: Nonrecurring engineering expenses of data to be transferred and computed within several clock Durability: Radiation Hardened and Program Integrity cycles. Time to market: Flexible and rapid prototyping and debugging Despite lower clock frequencies , FPGA’s can outperform Drawbacks conventional CPU’s on certain data processing tasks Lower working frequencies Higher power consumption Higher cost 7 8 Component-Based Software Design – LMES Component-Based Software Design – LMES Integration with microprocessors Programming technologies Fuse and anti-fuse: In order to provide an execution environment to those fuse makes or breaks link between two wires tasks not fitted for the FPGA execution paradigm smaller and faster Soft-core : a microcontroller wholly implemented inside the one-time programmable FPGA ( NIOS II ) Flash: System on Chip (SoC) : integrates a microcontroller and an high density FPGA inside a single chip ( Zynq ) dedicated production process ( in the past… ) RAM-based: memory bit controls a switch that connects/disconnects two wires can be programmed and re-programmed easily (using bitstreams) standard technology volatile SRAM memory 9 10 Component-Based Software Design – LMES Component-Based Software Design – LMES RAM-based programming Initially seen as a drawback imposing an initialization phase the volatility of SRAM-based FPGAs is not a liability , but was in fact the key to many new types of RECONFIGURABLE applications. COMPUTING the programming of such an FPGA could be changed by a completely electrical process… Characteristics 11 12 Component-Based Software Design – LMES Component-Based Software Design – LMES 2

11/05/2016 FPGA reconfiguration Selecting a Target FPGA Characteristics of the different reconfiguration approaches: While the previous uses of FPGAs still treat these Granularity chips purely as methods for implementing digital logic , the reprogrammability of modern FPGAs allows Dynamic reconfigurability to download algorithms onto the FPGAs and change Partial vs Full reconfiguration these algorithms just as general-purpose computers Reconfiguration time can change programs. “Fine-grain Dynamic Partial Reconfigurable devices” 13 14 Component-Based Software Design – LMES Component-Based Software Design – LMES Granularity Dynamic reconfigurability Two main architectures: It is the ability of a FPGA to modify operation during runtime Course grained : consists of small number of large logic blocks The primary advantages of runtime reconfiguration in devices Small bitstream is required to configure them (low config. time) Power/Size/Cost Reduction Faster because of easy routing Hardware reuse and flexibility Less complexity and less flexibility Application Portability Fine grained : consists of large number of small logic blocks Customization at the bit level => Greater flexibility & more complexity The disadvantage of dynamic reconfiguration Large bitstream is required to configure them (high config. time) Suffer from the time needed to load the configuration bitstream before starting its execution Easy conversion to ASIC Less speedy 15 16 Component-Based Software Design – LMES Component-Based Software Design – LMES Partial vs Full reconfiguration Partial Reconfiguration Partial reconfiguration (PR) allows Partial Reconfiguration (PR) allows the ability to reconfigure a the ability to reconfigure a portion portion of an FPGA of an FPGA ICAP Module A Controlling Agent It allows for critical parts of the design to continue operating while Mem controller Module B Real advantages arise when PR is Central done during runtime also know as loading a partial design into a reconfigurable module dynamic partial reconfiguration Module C Reconfiguration time of partial reconfiguration is much smaller Dynamic Reconfiguration allows (~4-5 ms) than full reconfiguration(~12 ms) Module D the reconfiguration of a portion of an FPGA while the remainder Wide variety of dynamically reconfigurable FPGA devices continues operating without any Static modules Reconfigurable Modules (PRMs) loss of data available in the market offer PR today Two types of Regions Lattice ORCA Architecture Modules: A & B FPGA PRR 1 Static – Keeps operating Static region Atmel AT40K Architecture Reconfigurable – Can be AItera APEX 20K reconfigured with a new module Static PRR 2 Modules: C & D modules Xilinx Virtex FPGAs 17 18 Component-Based Software Design – LMES Component-Based Software Design – LMES 3

11/05/2016 Partial Reconfiguration - Timing How to choose the FPGA model? Exploitation of Partial Reconfiguration for a design requires significant knowledge on targeted device An evaluation of the performance and limitations of your selection is required Also the support provided by design tools must be evaluated Correct FPGA selection matters! Xilinx’s FPGA’s (the Virtex Family is a widespread solution) is chosen as the example FPGA 19 20 Component-Based Software Design – LMES Component-Based Software Design – LMES Xilinx Virtex-II/Pro Architecture Basic Xilinx FPGA Layout Composed of a fine-grain 2D heterogeneous array that includes Configurable logic blocks (CLBs) Memory blocks (BRAMs) DSP units (MULTs) Embedded Processor I/O blocks (IOBs) (PowerPC/MicroBlaze) FIFOs buffers Processor Local Bus Each CLB contains LUTs, FFs, Gates & Multiplexers that can be configured to implement any design efficiently. On-Chip Peripheral Bus This 2D array can configured either externally or internally. Internal Configuration Acces Port 21 22 Component-Based Software Design – LMES Component-Based Software Design – LMES Xilinx FPGA Layout – Inside CLBs Xilinx Virtex – Reconfiguration FPGA is reconfigured by writing bits into Configuration Memory (CM). CM is arranged in vertical frames (1bit wide) stretching from top to bottom. bit bit_b word So Configuration data is organized into frames that target specific areas of the FPGA through frame addresses. 6T SRAM CELL To reconfigure any portion of that frame the partial bitstream contain configuration data for a whole frame. 23 24 Component-Based Software Design – LMES Component-Based Software Design – LMES 4

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.