Formation of Structural Defects in AlGaN/GaN High Electron Mobility - PowerPoint PPT Presentation

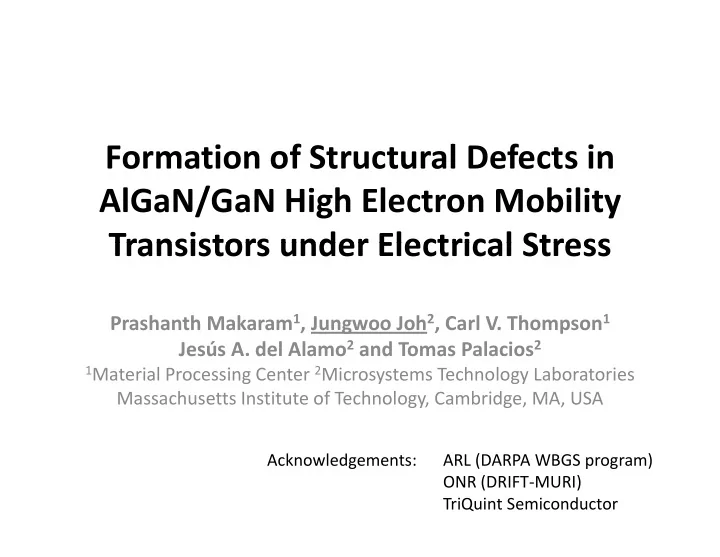

Formation of Structural Defects in AlGaN/GaN High Electron Mobility Transistors under Electrical Stress Transistors under Electrical Stress Prashanth Makaram 1 , Jungwoo Joh 2 , Carl V. Thompson 1 Jess A. del Alamo 2 and Tomas Palacios 2 1

Formation of Structural Defects in AlGaN/GaN High Electron Mobility Transistors under Electrical Stress Transistors under Electrical Stress Prashanth Makaram 1 , Jungwoo Joh 2 , Carl V. Thompson 1 Jesús A. del Alamo 2 and Tomas Palacios 2 1 Material Processing Center 2 Microsystems Technology Laboratories g y gy Massachusetts Institute of Technology, Cambridge, MA, USA Acknowledgements: ARL (DARPA WBGS program) ( ) ONR (DRIFT ‐ MURI) TriQuint Semiconductor

Introduction Introduction • GaN HEMT Reliability: big concern GaN HEMT Reliability: big concern – RF power degradation – I D decrease, R D increase, I G increase, V T change… I decrease R increase I increase V change • Goal: understand degradation mechanism 0 0 -0.2 (dB) RF stress -0.4 10 GHz,V D =28 V ∆ P out -0.6 I DQ =150 mA/mm -0.8 P in =23 dBm P P out =33.7 dBm =33 7 dBm -1 0 5 10 15 Time (hr) 2

High Voltage Degradation in GaN HEMTs HEMTs 1.2 1.E+01 OFF-state, V GS =-10 V V V DS 1 15 1.15 1 E 00 1.E+00 V GS = ‐ 10 V 0), R/R(0) 1.1 1.E-01 R D A/mm) G S D R S 1.05 1.E-02 AlGaN I Dmax /I Dmax (0 |I Goff | (A 1 1.E-03 2DEG 0.95 1.E-04 I Dmax I G ff I Goff 0 9 0.9 1 E 05 1.E-05 I GaN V crit 0.85 1.E-06 Joh, EDL 2008 10 20 30 40 50 V V DGstress (V) (V) I Dmax : V DS =5 V, V GS =2 V I Goff : V DS =0.1 V, V GS = ‐ 5 V I D , R D , and I G start to degrade beyond critical voltage (V crit ) D D G crit (+ trapping behavior – current collapse) Common physical origin in I D and I G degradation 3

Material Degradation around V it Material Degradation around V crit V DG =0 V V DG =16 V~V crit 50 50 egradation (%) 40 30 ermanent I Dmax De 20 10 Joh ROCS 2010 Joh, ROCS 2010 Pe V DG =25 V V DG =37 V 0 0 2 4 6 8 Pit depth (nm) Good correlation between pit depth and electrical degradation degradation Initial dimple followed by deeper pitting and cracking. 4

Plan View Approach Plan View Approach • Limitation of TEM: costly extremely local Limitation of TEM: costly, extremely local • This work: hi k – Removal of SiN passivation and gate • SiN passivation: HF etch (1:10 HF: H 2 O) • Contact and gate metals: aqua regia (3:1 HCl: HNO 3 ) at 80 ˚ C for 20 minutes 80 C for 20 minutes • Surface cleaning: piranha solution (H 2 SO 4 : H 2 O) for 5 minutes at 115 ˚ C – Plan view imaging through SEM and AFM 5

SiN and Gate Removal SiN and Gate Removal Source Gate G Drain Stressed (> V crit ) 6 Unstressed (high T storage)

Experimental Experimental • OFF ‐ state step stress OFF state step stress – V GS = ‐ 7 V – V DS stepped from 5 to 8, 12, 20, 35, 50 V (1V/min) V stepped from 5 to 8 12 20 35 50 V (1V/min) – T base =150C • Detailed device characterization: D t il d d i h t i ti – DC device parameters: I Dmax , R S , R D , V T … – Trap characterization: current collapse • Removal of passivation and gate metal • SEM and AFM plan view imaging 7

Electrical Degradation Electrical Degradation 12 1.E+01 OFF ‐ state step stress OFF state step stress dation (%) 10 1.E+00 e (%) m) nent Degrad 8 8 off | (mA/mm nt Collapse 1.E ‐ 01 I Goff CC 6 1.E ‐ 02 Dmax Perman |I Go Curre 4 V crit I Dmax 1.E ‐ 03 2 I D 0 1.E ‐ 04 Current collapse: 0 10 20 30 40 50 60 Fresh 1s pulse V V DGstress (V) (V) V V DS =0, V GS = ‐ 10V 0 V 10V Typical critical behavior beyond 19 V 8

Structural Degradation Structural Degradation V DG =15 V V DG =19 V 200 nm 200 nm Unstressed 200 nm DG DG (V crit ) 200 nm V DG =42 V V DG =57 V 200 nm Initial continuous groove formation Deeper pit formation along the groove 9

Pit Cross Section Area Pit Cross Section Area Source Drain Gate 0.5 140 120 0 nm) m 2 ) 100 100 ge Pit Depth ( ge Pit Area (n -0.5 80 -1 60 -1.5 1 5 Averag Avera 40 -2 20 V DGstress =57 V 0 -2.5 5 0 0 0.2 0 2 0 4 0.4 0 6 0.6 0 10 20 30 40 50 60 x ( m) Stress Voltage V DGstress (V) Drain side pit area also shows critical behavior. 10

Correlation between Electrical and Structural Degradation l d 12 12 12 12 gradation (%) ) ) t Collapse (%) 10 10 8 8 nent I Dmax Deg tress Current 6 6 4 4 2 2 2 2 Perman Post ‐ St 0 0 0 50 100 150 0 50 100 150 Average Defect Area (nm 2 ) 2 ) Average Defect Area (nm 2 ) 2 ) f ( f ( Good correlation between electrical degradation and pit area Good correlation between electrical degradation and pit area 11

Time Evolution Time Evolution OFF ‐ state stress V DGstress =50 V (>V crit ), T base =150 C S Source side groove formation id f ti Pits grow in density and merge with each other. 12

Symmetric Stress (V DS =0) Symmetric Stress (V DS 0) Stress conditions: Stress conditions: ‐ V DS =0, V GS = ‐ 50 V (stressed on both sides) ‐ 40 min. 40 min Drain ‐ Room temperature V GS G S D Gate AlGaN 2DEG 2DEG Source GaN Grooves and pits on both sides of the gate 13

Degradation Mechanisms Degradation Mechanisms • Consistent observation in TEM and plan ‐ view Co s ste t obse at o a d p a e – Grooves and pits are not by ‐ product of etching • Groove formation – Field induced oxidation? – Electrochemical etching? • Pit formation – Degradation is E ‐ field driven (Little current is needed) – Field/stress induced diffusion of material away from gate? • In any event mass transport is involved • In any event, mass transport is involved. 14

Summary Summary • Developed a simple process for plan ‐ view e e oped a s p e p ocess o p a e assessment of structural degradation • Evolution of structural damage: g – Below V crit : shallow continuous groove formation at gate edge – Above V crit : local pit formation along the Ab V l l i f i l h groove – Number of pits increases with V stress and time Number of pits increases with V stress and time and pits merge • Field induced mass transport is involved in GaN HEMT degradation 15

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.