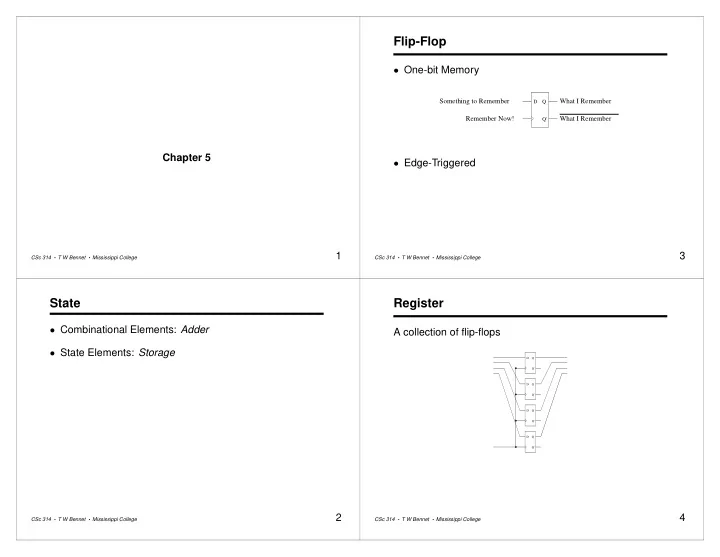

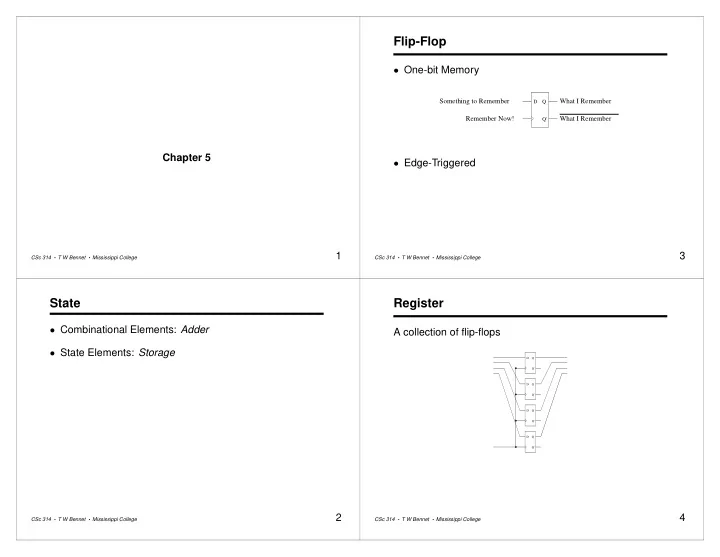

Flip-Flop • One-bit Memory Something to Remember What I Remember D Q Remember Now! What I Remember Q’ Chapter 5 • Edge-Triggered 1 3 CSc 314 · T W Bennet · Mississippi College CSc 314 · T W Bennet · Mississippi College State Register • Combinational Elements: Adder A collection of flip-flops • State Elements: Storage D Q Q’ D Q Q’ D Q Q’ D Q Q’ 2 4 CSc 314 · T W Bennet · Mississippi College CSc 314 · T W Bennet · Mississippi College

State Machines Counter: A State Machine • Stored bit describes the state of the object. 1 • A clock generates a regular pattern of voltage changes. D Q Q’ • The state changes when the clock “ticks.” D Q Q’ D Q Q’ D Q Q’ Oflow 5 7 CSc 314 · T W Bennet · Mississippi College CSc 314 · T W Bennet · Mississippi College Clocks and State Machines • At each tick, the machine does the “next” thing. • The faster the clock, the faster the machine. • The clock must be slow enough for changes to propagate back to the registers during a clock cycle. • This is what those computer ads are talking about. State changes when the clock rises. · 6 8 CSc 314 · T W Bennet · Mississippi College CSc 314 · T W Bennet · Mississippi College

Building the Datapath • Parts. • Sub-assemblies. • Complete datapath. 9 11 CSc 314 · T W Bennet · Mississippi College CSc 314 · T W Bennet · Mississippi College Datapath and Control • Datapath: Moving, storing, and creating data. • Control: Making each of those happen at right place and time. 10 12 CSc 314 · T W Bennet · Mississippi College CSc 314 · T W Bennet · Mississippi College

Datapath For Fetching 13 15 CSc 314 · T W Bennet · Mississippi College CSc 314 · T W Bennet · Mississippi College Datapath For R-Type Instructions Read reg 1 Read reg 2 Write reg op sreg1 sreg2 destreg shft amt funct 6 5 5 5 5 6 14 16 CSc 314 · T W Bennet · Mississippi College CSc 314 · T W Bennet · Mississippi College

Datapath For Loading and Storing Datapath Combined Write register Read Reg 1 Read Reg 2 Others Loads op Rbase Rdest Offset 6 5 5 16 17 19 CSc 314 · T W Bennet · Mississippi College CSc 314 · T W Bennet · Mississippi College Datapath for Branching Control • Signals the devices what they must do. • Interprets the instruction. • A large combinational circuit. 18 20 CSc 314 · T W Bennet · Mississippi College CSc 314 · T W Bennet · Mississippi College

Add Control Units ALU Control Signals ALU Control Input ALU Function 0000 and 0001 or 0010 add 0110 subtract 0111 set on less than 1100 NOR 21 23 CSc 314 · T W Bennet · Mississippi College CSc 314 · T W Bennet · Mississippi College ALU Controller Secondary Controller • Inputs: Low six bits of the instruction (function code), From Main Func Output and two bits sent from the main controller. 00 XXXXXX 0010 X1 XXXXXX 0110 op sreg1 sreg2 destreg shft amt funct R 1X XX0000 0010 6 5 5 5 5 6 1X XX0010 0110 1X XX0100 0000 • Outputs: ALU Function selection. 1X XX0101 0001 1X XX1010 0111 Determine what ALU needs to do based on the main controller’s direction and the function code from the instruction. 22 24 CSc 314 · T W Bennet · Mississippi College CSc 314 · T W Bennet · Mississippi College

Main Control Main Control: Input Signals • Input: High six bits of the instruction (op code). Op Code: First Six Instruction Bits Instruction Op5 Op4 Op3 Op2 Op1 Op0 op sreg1 sreg2 destreg shft amt funct R R-Format 0 0 0 0 0 0 6 5 5 5 5 6 lw 1 0 0 0 1 1 op Rbase Rdest Offset I sw 1 0 1 0 1 1 6 5 5 16 beq 0 0 0 1 0 0 • Outputs: RegDst, Branch, MemRead, MemtoReg, • Just a large, combinational circuit. AULOp, MemWrite, ALUSrc, RegWrite. 25 27 CSc 314 · T W Bennet · Mississippi College CSc 314 · T W Bennet · Mississippi College Main Control: Output Signals Single-Cycle Implementation Mem- Instruction RegDst ALUSrc toReg RegWrite R-Format 1 0 0 1 lw 0 1 1 1 sw X 1 X 0 beq X 0 X 0 Mem- Mem- ALU ALU Instruction Read Write Branch Op1 Op2 R-Format 0 0 0 1 0 lw 1 0 0 0 0 sw 0 1 0 0 0 beq 0 0 1 0 1 26 28 CSc 314 · T W Bennet · Mississippi College CSc 314 · T W Bennet · Mississippi College

Single-Cycle Changes for Multi-Cycle Problems: • A single memory unit for both instructions and data. • The cycle must be long enough for the longest • A single ALU, rather than an ALU and two adders. instruction. • Add internal registers to hold the results of each cycle for • Components must be duplicated, as the second ALU. the next. A Solution: • Shorter cycle. • Multiple cycles per instruction. • Different numbers of cycles for different instructions. 29 31 CSc 314 · T W Bennet · Mississippi College CSc 314 · T W Bennet · Mississippi College High-Level View 30 32 CSc 314 · T W Bennet · Mississippi College CSc 314 · T W Bennet · Mississippi College

Full Multi-Cycle Implementation 33 35 CSc 314 · T W Bennet · Mississippi College CSc 314 · T W Bennet · Mississippi College 34 36 CSc 314 · T W Bennet · Mississippi College CSc 314 · T W Bennet · Mississippi College

37 39 CSc 314 · T W Bennet · Mississippi College CSc 314 · T W Bennet · Mississippi College 38 40 CSc 314 · T W Bennet · Mississippi College CSc 314 · T W Bennet · Mississippi College

Multi-Cycle Operation 41 43 CSc 314 · T W Bennet · Mississippi College CSc 314 · T W Bennet · Mississippi College Control Logic Compute the Outputs from the Inputs • Lots of gates. • ROM • Etc. 42 44 CSc 314 · T W Bennet · Mississippi College CSc 314 · T W Bennet · Mississippi College

An Alternative: Microcode Microinstructions • One large instruction for each state. • Specifies the signals to generate. • Specifies the next instruction. 45 47 CSc 314 · T W Bennet · Mississippi College CSc 314 · T W Bennet · Mississippi College Address Select Logic Next Address (State) 11 10 01 00 0 Data Out Data Out ROM 2 ROM 1 Sequence Addr In Addr In Control (From microinstruction) Curr Address + 1 Op Code (From IR) Microcontroller Address Select Logic 46 48 CSc 314 · T W Bennet · Mississippi College CSc 314 · T W Bennet · Mississippi College

Exceptions and Interrupts Jump to the O/S upon certain events. Event Source MIPS Term I/O Device Request External Interrupt User Program Calls O/S (Syscall) Internal Exception Arithmetic Overflow Internal Exception Undefined Instruction Internal Exception Hardware Malfunction Either Either 49 51 CSc 314 · T W Bennet · Mississippi College CSc 314 · T W Bennet · Mississippi College Types of Exceptions • Vectored: Jumps to different locations based on type of exception or interrupt. • Cause Register: Store a code for the cause of the exception in a special register, then jump to a standard place. • MIPS uses the later. 50 52 CSc 314 · T W Bennet · Mississippi College CSc 314 · T W Bennet · Mississippi College

MIPS Exception Registers Exception Datapath • EPC: Holds the address of the offending instruction. • Cause: Holds a code for the cause of the exception. 53 55 CSc 314 · T W Bennet · Mississippi College CSc 314 · T W Bennet · Mississippi College Exceptions For the example implementation, we consider two exceptions • Undefined instruction: Code 0. • Arithmetic overflow: Code 32. 54 56 CSc 314 · T W Bennet · Mississippi College CSc 314 · T W Bennet · Mississippi College

Recommend

More recommend