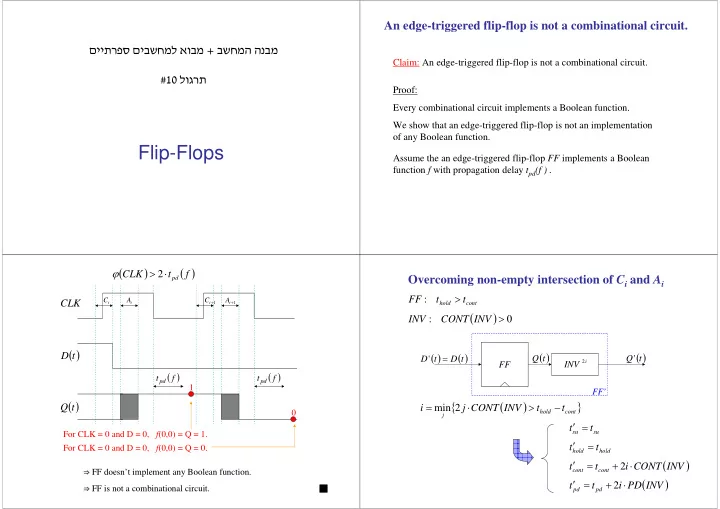

� � An edge-triggered flip-flop is not a combinational circuit. �������������������� �� ����������� Claim: An edge-triggered flip-flop is not a combinational circuit. ��� �� ������ Proof: Every combinational circuit implements a Boolean function. We show that an edge-triggered flip-flop is not an implementation of any Boolean function. Flip-Flops Assume the an edge-triggered flip-flop FF implements a Boolean function f with propagation delay t pd (f ) . � � � � � � 2 � CLK t f Overcoming non-empty intersection of C i and A i pd � FF : t t C A C A CLK � � i i i 1 i 1 hold cont � � � INV : CONT INV 0 � � � � � � � � � � D t � D ' t D t Q t Q ' t INV 2 i FF � � � � t pd f t pd f 1 FF’ � � � � � � � � � � Q t i min 2 j CONT INV t t 0 hold cont j � � t t su su For CLK = 0 and D = 0, f (0,0) = Q = 1. � � t t For CLK = 0 and D = 0, f (0,0) = Q = 0. hold hold � � � � � � t t 2 i CONT INV cont cont FF doesn’t implement any Boolean function. � � � � � � t t 2 i PD INV FF is not a combinational circuit. pd pd

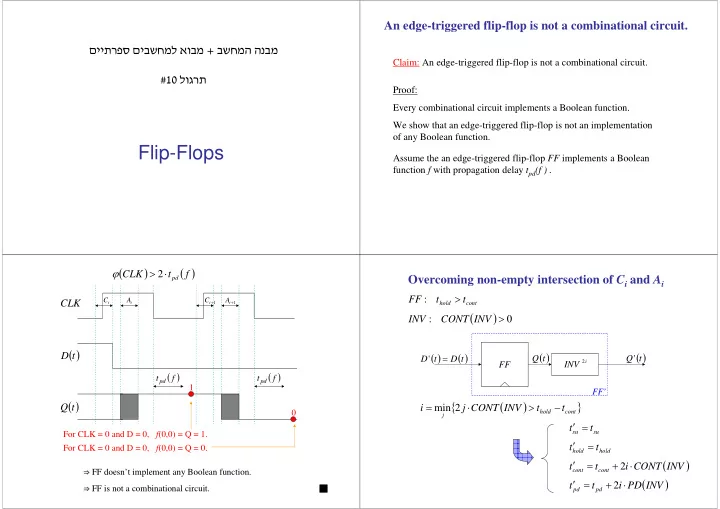

� � Clock enabled edge-triggered flip-flop An edge-triggered flip-flop with a reset signal � � D t Definition: An edge-triggered flip-flop with a reset signal is defined as follows: � � CE t MUX � � � � Inputs : Digital signals D t , RST t and a clock CLK . C A CLK � � . i i Output : Digital signal Q t FF CLK � � � � Functional ity : If D t and RST t are stable during the critical � � � � � � � � � segment C , then for every t t t , t t � 1 D t , CE t � � i i pd i cont Q t � � � � � � � � D t if RST t 0 PD(MUX) � � � D t i i 0 � � � Q t CONT(MUX) � � � � � � t t PD MUX � 0 if RST t 1 � � su su i � � D FF t RST t � � MUX � � � t t CONT MUX hold hold � � t t � � FF CLK cont cont Q t � � t t � � pd pd Q t Changing the flip-flop parameters (0) Changing the flip-flop parameters (1) G � � � � Q t D t � � � � � � � � � FF D t Q ' t Q t D ' t i � � � � G FF � � t G t G 0 pd cont FF’ A concatenation of i G gates: CLK CLK � � � � � � � � � � t F F t FF i t G � � � � i su su pd G � t FF , t FF 0 � � � � � � su hold � � � � � � � � t F F t FF i t G � � i hold hold cont t G i t G pd pd � � � � � � � � � � t F F t FF � � i t G i t G cont cont cont cont � � � � � � t F F t FF pd pd Goal: � � � � (1) Design an edge-triggered flip-flop FF’ with t hold ( FF ) 0. t FF � � � � � hold t hold F F 0 i � � � � � � (2) Design an edge-triggered flip-flop FF’’ with t su ( FF ) 0. t G cont

Changing the flip-flop parameters (2) � � � � � � � � CLK � � � � � � D t D t Q t Q t FF PD(G i ) PD(G i ) X X i CONT(G i ) CONT(G i ) G � � � � � � � � � � � t F F t FF i t G su su cont FF’’ � � � � � � � � � � � t F F t FF i t G CLK hold hold pd � � � � � � � � � � � t F F t FF i t G cont cont cont � � � � � � � � � � � t F F t FF i t G pd pd pd � � � � t FF � � � � � � su t su F F 0 i � � � � � � t G cont

Recommend

More recommend