Fast Electronics for Future Experiments Gary S. Varner University - PowerPoint PPT Presentation

Fast Electronics for Future Experiments Gary S. Varner University of Hawaii University of Hawai i Joint CPAD and IFCM, Jan. 11, 2013 Overview Further advances at the Discovery Frontier Depends upon developing new instruments and

Fast Electronics for Future Experiments Gary S. Varner University of Hawai’i University of Hawai i Joint CPAD and IFCM, Jan. 11, 2013

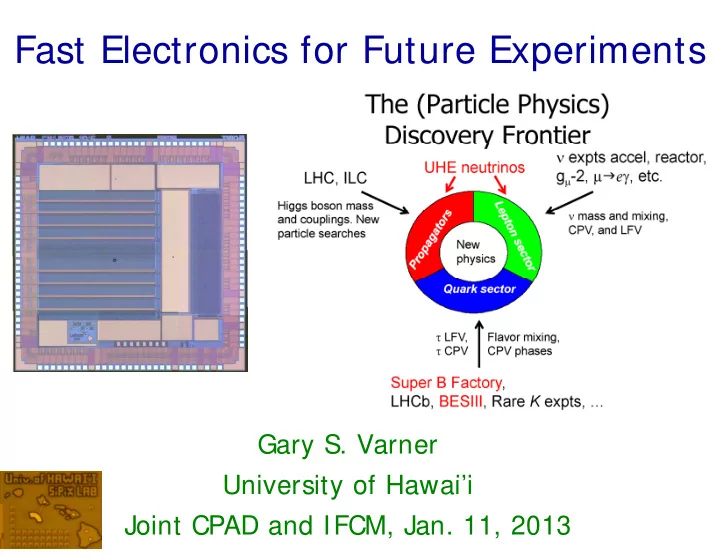

Overview • Further advances at the Discovery Frontier – Depends upon developing new instruments and techniques – Exploit commodity resources • The “easy” experiments are being completed y p g p – Can’t necessarily scale up ($$$, T>N*t gradstudent ) – Innovation fuels new opportunities Innovation fuels new opportunities • What I hope to convey: 1. A new “Giga” Era implies fast timing naturally 1 A “Gi ” E i li f t ti i t ll 2. Introduce key elements 3. An example where this has been fundamentally enabling 3 A l h hi h b f d ll bli 4. A notion toward future directions 2

Detector Instrumentation Evolution History • Traditional “crate based” electronics Q-ADC – Gated Analog-to-Digital Converters Det chan TDC TDC – Referenced “triggered” Time-to-Digital Converters Disc. Trigger • High-rate applications – “pipelined operation” – Low-speed, low-resolution sampling • High channel counts – Motivation to reduce cabling – Integrate electronics onto detector elements Det chan FADC Issues: cost, power, resolution, data volume 3

A “Giga” Overview (Modern Readout) 2. 100’s of Giga flops per 4. Commodity Servers Field-Programmable running at Giga -Hz rates, Gate Array Gate Array 1000’s of Giga flops 1000’ f Gi fl Physical Physical Measurement 1. Giga sample/s “digital oscilloscope 3. Inexpensive Giga -bit/s on a chip” fiber link interconnect; Giga -bit ethernet Technology advances high rate, high-precision experiments 4

Focus on the first of these 2. 100’s of Gigaflops per 4. Commodity Servers Field-Programmable running at Giga-Hz rates, Gate Array Gate Array 1000 s of Gigaflops 1000’s of Gigaflops Physical Physical Measurement 1. Gigasample/s “digital oscilloscope 3. Inexpensive Giga-bit/s on a chip” fiber link interconnect; Giga-bit ethernet • Defines limit of the physical measurement • What Instrumentation Physicists contribute 5

Underlying Technology • Track and Hold (T/ H) T/H Sampled Data Analog Input g p C • Pipelined storage = array of T/ H elements, with output buffering l t ith t t b ff i Top Read Bus Vout=A / (1+A) * Q/Cs Write Bus N capacitors =V1 * A/(1+A) Bottom Read Bottom Read v V1=V V1=V 2 BUS Q=Cs.V 1 4 1 Cs 3 Return Bus N caps 6

7 Tiny charge: 1mV ~ 100e - Switched Capacitor Array Sampling 20fF Channel 2 Channel 1 switches closed @ once tc es c osed @ o ce Write pointer is ~few s • Few 100ps delay Input Input

Basic Functional components On or off- chip ADC chip ADC Single storage Ch Channel l Sample timing S l ti i Control Few mm x Few mm in size Readout Control 8

The Giga Package • 2 GSa/s, 1GHz ABW T k Tektronics Scope i S • 2.56 GSa/s LAB WFS ASIC Commercial S Sampling li 0.1-6 GSa/s 2 GSa/s speed “oscilloscope on Bits/ENOBs 16/9-13+ 8/7.4 a chip” Power/Chan. < = 0.05W Few W Cost/Ch. < $10 (vol) > 100$ 9

10 Very broad Impact LAPPD LAPPD Fundamental enabling technology (smallest to largest) Neutrinos AMBER

To be explicit, a demanding Application ~320ps Measured Measured ~7m • RF Transient (impulsive) Events (200-1200 MHz) • 324 chan. @ 2.6GSa/s 32 h @ 2 6GS / • Completely solar powered (tight demands on power, (tight demands on po e few hundred W total) • • Need full waveforms Need full waveforms A t Antarctic Impulsive Transient Antenna ti I l i T i t A t (ANITA-I) 11

ANITA concept Typical balloon field of regard 12 ~4km deep ice! Ice RF Effective “telescope” aperture: p p clarity: clarity: • ~250 km 3 sr @ 10 18 eV ~1.2km(!) • ~10 4 @ km 3 sr 10 19 eV attenuation ( compare to ~1 km 3 at lower E) ( length 12

Large Analog Bandwidth Recorder and Digitizer with Ordered Readout [LABRADOR] ith O d d R d t [LABRADOR] • Common STOP acquisition • 3.2 x 2.9 mm Straight • Conversion in Shot 120 s (all RF inputs 2340 samples) • Data transfer takes 80 s • Ready for next • Switched 8+1 chan. * 256+4 samples event in Capacitor 200 s Array (SCA) • Massively parallel Wilkinson ADC array Random access: 13

LABRADOR performance 12-bit ADC 2.6GSa/s 1.3mV • 10 real bits (1.3V/1.3mV noise) • Excellent linearity, noise • Sampling rates up to 4 GSa/s with voltage overdrive 14

(SURF = Sampling Unit for RF) (TURF = Trigger Unit for RF) SURFv3 Board SURFv3 Board J4 to TURF J1 to CPU LAB3 RF Inputs Programming/ Monitor Header Monitor Header Trigger Inputs PCI bus: 64bits, 66MHz ~ 0.5 GigaByte/s (upgrading for 3 rd flight) 15

Logical segmentation (example Trigger Type = 1 shown) A “high rate” Experiment g p Top cluster L2 = 2 of 5 Phi = 0 (1 of 16) Raw Signals Bottom cluster L2 = 2 of 5 L2 = 2 of 5 Nadir cluster L2 = 2 of 3 Level-2 Level-1 Level-3 SS Prioritizer Prioritizer n TDRS Cluster Antenna (+compress) Phi ents/min 2-of-2 2 f 2 2-of-5 2 f 5 3-of-8 f Few eve Few kHz 5-10Hz @ 36kBy/evt @ 36kBy/evt = 36-72Mby/s = 180-360kBy/s F To disk T di k 100-200kHz 100 200kH @ 36kBy/evt 80 RF channels = 3.6-7.2Gby/s @ 1.5By * 2.6GSa/s = 312 Gbytes/s Permits thermal noise level operation 16

17

The “no free lunch” Theorem • Excellent results obtained 1. Made the ANITA project possible & highly successful 2. Similar architectures being studied for new and upgraded experiments 3. Minimize costs for large systems • Not a magic solution – Significant constraints – Technology in its infancy – will continue to improve • Limits and future directions The technology in a bit more detail The technology, in a bit more detail 18

Constraint 0: An Intrinsic Limitation No power (performance savings) for continuous digitization g Won’t displace Flash ADCs “d “down conversion” i ” For most “triggered” ‘event’ applications, not a serious drawback 19

Constraint 1: Analog Bandwidth Difficult to couple in Large BW (C is deadly) inside ASIC inside ASIC RFamp RFamp Z S Z S Vsig Vsig Vin Vin 50 C in Ω Z T f 3dB = 1/2 ZC 20

Bandwidth Limitations (LAB1 example) f 3dB = 1/2 ZC Would like smallest possible Cstore • • For 1 2GHz C < ~ 2pF (NB input protection diode ~ 10pF) For 1.2GHz, C < ~ 2pF (NB input protection diode ~ 10pF) • Minimize C, (C drain not negligible x260) 21

An Example Bandwidth Evaluation LAB3 LAB3 Transient 9 channels of 9 channels of Impulse 256 samples To do FFT better, Difference f 3dB ~> 1.2GHz reduce input and Frequency [GHz] storage C storage C 22

23 Constraint 2: kTC Noise Want small storage C, but…

Similar Constraint 2b: Leakage Current Increase C or reduce conversion time << 1mV Sample channel-channel variation Sample channel-channel variation ~ fA leakage typically 24

Constraint 3: Digitization • No missing codes • Linearity as good as 12-bit ADC can make ramp • Can bracket range of interest Run count during ramp Wilki Wilkinson ADC ADC • Excellent linearity • Basically as good as can make current source/comparator • Comparator ~ 0.4 – 2.1V; 133MHz GCC max (~ 31us) 25

Constraint 4: Sample Aperture Variance • Inverter chain has transistor variations i ti • t i between samples differ “Fixed pattern aperture jitter” • “Differential temporal nonlinearity” TD i = t i – t nominal i i nominal • “Integral temporal nonlinearity” TI i = t i – i t nominal • “Random aperture jitter” = variation of t i between measurements i t 1 t 2 t 3 t 4 t 5 TD TD 1 TI TI 5 26

Non-uniform sampling timebase SURF data SURF data Long-suffering ANITA collaborator Long suffering ANITA collaborator 27

28 10-15% of dT typical dT Spread 2.6 GSa/s [LABRADOR3]

Average aperture calibration • Fixed aperature offsets are Fixed aperature offsets are constant over time, can be measured and corrected • Several methods are commonly used (sine fit [left], zero-crossing) • Most use sine wave with random phase and correct for TD i on a statistical basis l b 29

Sine Curve Fit Method i 500 1024 2 2 2 ( ( sin( ) )) min y a i o ji j j i j f j j 0 i 0 j j y ji : i-th sample of measurement j a j f j j o j : sine wave parameters j j j j i : phase error fixed jitter “Iterative global fit”: Iterative global fit : • Determine rough sine wave parameters fo each meas for each measurement by fit ement b fit • Determine i using all measurements where sample “i” is near zero crossing • Make several iterations j S. Lehner, B. Keil, PSI 30

Option 1: Even Faster Sampling p p g 6 GSPS * 8 = 48 GSPS ) 8 = 25ps) (200ps/8 delays Possible with delay is implemented on PCB o b d ay p d o 31

32 Coupling between wire-bonds, Vref Constraint 5: Cross-talk

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.

![CRACKING GATE SANKET PURANDARE AIR 25 (CS) GATE 2016 WHY NOT GRE ? [MS IN USA] Except](https://c.sambuz.com/1025590/cracking-gate-s.webp)

![Decoders and Trees 2 n 1 2 n 1 AND (2 n 1 ) AND (2 n 1 ) y [2 n 1 : 2 n 1 ]](https://c.sambuz.com/1025595/decoders-and-trees-s.webp)