Design of an ASIP IDEA Crypto Processor Reza Faghih Mirzaee 1 and - PowerPoint PPT Presentation

Design of an ASIP IDEA Crypto Processor Reza Faghih Mirzaee 1 and Mohammad Eshghi 2 1 Department of Computer Engineering, Science and Research Branch, Islamic Azad University, Tehran, Iran. 2 Faculty of Electrical and Computer Engineering, Shahid

Design of an ASIP IDEA Crypto Processor Reza Faghih Mirzaee 1 and Mohammad Eshghi 2 1 Department of Computer Engineering, Science and Research Branch, Islamic Azad University, Tehran, Iran. 2 Faculty of Electrical and Computer Engineering, Shahid Beheshti University, G.C., Tehran, Iran.

ASIP vs. ASIC and General-Purpose Processor IDEA Crypto Algorithm Implementing Specific Instructions Testing Process and Results Design ¡of ¡an ¡ASIP ¡IDEA ¡Crypto ¡Processor, ¡ 2 ¡ R. ¡Faghih ¡Mirzaee ¡and ¡M. ¡Eshghi ¡

Application Specific Application Specific General-Purpose Integrated Circuit Instruction-set Programmable (ASIC) Processor (ASIP) Processor v Software Dominant v Hardware Dominant Hardware / Software Advantages : Advantages : Advantages : Ø High Throughput Ø Software Ø Programmability Ø Energy Efficiency Programmability Ø Simple Designing and Ø Fast Debugging Flexibility Ø Short Time to Market Ø Efficiency Design ¡of ¡an ¡ASIP ¡IDEA ¡Crypto ¡Processor, ¡ 3 ¡ R. ¡Faghih ¡Mirzaee ¡and ¡M. ¡Eshghi ¡

International Data Encryption Algorithm (IDEA) v Lai & Massey (1991) v 64-bit Plaintext v 128-bit Initial Key v 64-bit Ciphertext v 8 Identical Rounds + 1 Final Round Design ¡of ¡an ¡ASIP ¡IDEA ¡Crypto ¡Processor, ¡ 4 ¡ R. ¡Faghih ¡Mirzaee ¡and ¡M. ¡Eshghi ¡

Instruction-Set General-Purpose Specific Instructions Instructions CODER × 8 FINAL CODER × 1 Design ¡of ¡an ¡ASIP ¡IDEA ¡Crypto ¡Processor, ¡ 5 ¡ R. ¡Faghih ¡Mirzaee ¡and ¡M. ¡Eshghi ¡

Stage 1 Stage 2 CODER Stage 3 Specific Instruction Stage 4 Stage 5 v Only One ALU Stage 6 Stage 7 Ø 14 Stages : Stage 8 Stage 9 Ø Modulo 2 16 Adder : Stage 10 Ø Modulo 2 16 +1 Multiplier Stage 11 Stage 12 : Ø Bitwise Exclusive-OR Stage 13 Stage 14 Design ¡of ¡an ¡ASIP ¡IDEA ¡Crypto ¡Processor, ¡ 6 ¡ R. ¡Faghih ¡Mirzaee ¡and ¡M. ¡Eshghi ¡

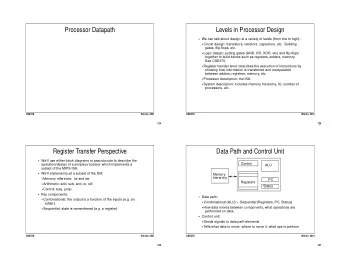

Proposed Register and ALSU Configuration v RTL Ø #Clock Cycles Specifications : Ø Address Bus : AR/PC Ø ACH / ACL Ø Specific X i Registers Ø Specific K i Registers Ø 17-bit Subtractor Design ¡of ¡an ¡ASIP ¡IDEA ¡Crypto ¡Processor, ¡ 7 ¡ R. ¡Faghih ¡Mirzaee ¡and ¡M. ¡Eshghi ¡

Bitwise Modulo 2 16 +1 Modulo 2 16 Exclusive-OR Multiplication Addition A A A B B B 16-bit Result Carry / 16-bit Sum 16-bit Result v Meier and Zimmermann unit16 mulmod(unit16 x, unit16 y) { F 21 D 0 T i : ACH/ACL ß ß DR × ACL , TR1 ß ß ACL x = (x - 1) & 0xFFFF; F 21 D 0 T i+1 : ACL ß ß DR+ACL , DR ß ß TR1 y = (y - 1) & 0xFFFF; F 21 D 0 CT i+2 : ACH ß ß ACH+1 unit32 t = (x × y) + x + y + 1; F 21 D 0 T i+2 : ACL ß ß DR+ACL x = t & 0xFFFF; F 21 D 0 CT i+3 : ACH ß ß ACH+1 y = t >> 16; F 21 D 0 T i+3 : ACL ß ß ACL+1 x = (x – y) + (1 if x ≤ y); F 21 D 0 CT i+4 : ACH ß ß ACH+1 return x; } Design ¡of ¡an ¡ASIP ¡IDEA ¡Crypto ¡Processor, ¡ 8 ¡ R. ¡Faghih ¡Mirzaee ¡and ¡M. ¡Eshghi ¡

ALSU Opcode Unit Operation Function 0 0 0 0 0 ADD A+B 0 0 0 0 1 SUB A-B Arithmetic Logic 0 0 0 1 0 DEC A-1 Shift Unit AU (ALSU) 0 0 0 1 1 INC A+1 0 0 1 × × MUL A × B Ø Carry Flag = C out when 0 1 0 0 0 AND A ˄ B ADD|SUB|DEC|INC|SHL|SHR 0 1 0 0 1 OR A ˅ B 0 1 0 1 0 NAND (A ˄ B)’ Ø Overflow Flag = ‘1’ when 0 1 0 1 1 NOR (A ˅ B)’ (ADD|INC|SHL & C out = ‘1’) | LU 0 1 1 0 0 XOR A ⊕ B (SUB|DEC & C out = ‘0’) | 0 1 1 0 1 XNOR (A ⊕ B)’ (MUL & ACH ≠ 0) 0 1 1 1 0 NOT B’ Ø Zero Flag = ‘1’ when ACL=0 0 1 1 1 1 PASS A Ø Sign Flag = ‘1’ when 1 × × 0 0 SHL SHL(B) (SUB|DEC & C out = ‘0’) 1 × × 0 1 SHR SHR(B) SU Ø Even Flag = ACL[0]’ 1 × × 1 0 ROL ROL(B) Design ¡of ¡an ¡ASIP ¡IDEA ¡Crypto ¡Processor, ¡ 1 × × 1 1 ROR ROR(B) 9 ¡ R. ¡Faghih ¡Mirzaee ¡and ¡M. ¡Eshghi ¡

D i I 1 I 0 Instruction Instruction Addressing Type Reference Mode Instruction Types D 0 0 0 2 Reg. | I/O - D 1 1 0 1 Memory Immediate D 2 0 1 1 Memory Direct D 3 1 1 1 Memory Indirect 15 14 13 9 8 0 I1 I0 Opcode No. of Iterations / Unused Type 1 : Address / Data 15 14 13 9 8 0 Type 2 : I1 I0 Opcode Unused Design ¡of ¡an ¡ASIP ¡IDEA ¡Crypto ¡Processor, ¡ 10 ¡ R. ¡Faghih ¡Mirzaee ¡and ¡M. ¡Eshghi ¡

Generating v 6 Subkeys per Round + 4 Subkeys for Final Round Encryption à à 8 × 6 + 4 = 52 Subkeys Subkeys Rotate Left 25 bits 128-bit Initial Private Key SK0 SK1 SK2 SK3 SK4 SK5 SK6 SK7 15-7 6-0 15-7 6-0 15-7 6-0 15-7 6-0 15-7 6-0 15-7 6-0 15-7 6-0 15-7 6-0 SK8 SK9 SK10 SK11 SK12 SK13 SK14 SK15 Ø K i [8-0] ß ß K (i+2) mod 8 [15-7] Ø K i [15-9] ß ß K (i+1) mod 8 [6-0] Design ¡of ¡an ¡ASIP ¡IDEA ¡Crypto ¡Processor, ¡ 11 ¡ R. ¡Faghih ¡Mirzaee ¡and ¡M. ¡Eshghi ¡

Round r r = 1 2 ≤ r ≤ 8 r = 9 Generating K’ 1 (r) (K 1 (10-r) ) -1 (K 1 (10-r) ) -1 (K 1 (10-r) ) -1 Decryption K’ 2 (r) -K 2 (10-r) -K 3 (10-r) -K 2 (10-r) Subkeys K’ 3 (r) -K 3 (10-r) -K 2 (10-r) -K 3 (10-r) K’ 4 (r) (K 4 (10-r) ) -1 (K 4 (10-r) ) -1 (K 4 (10-r) ) -1 v IDEA : Symmetric (r) (9-r) (9-r) K’ 5 K 5 K 5 - K’ 6 (r) K 6 (9-r) K 6 (9-r) - v K’ : Decryption Subkey v -K : 2 16 Additive Inversion Ø - K i = (2 16 – K i ) & 0xFFFF v Devider v K -1 : 2 16 +1 Multiplicative Inversion Ø Low Frequency & High Chip Area v Extended Euclidean Algorithm v Binary Extended GCD Algorithm Ø ax + by = GCD(a, b) , a ≥ b ≥ 0 Ø a = 2 16 +1 , b = K i , y = K i -1 Ø K -1 = y Design ¡of ¡an ¡ASIP ¡IDEA ¡Crypto ¡Processor, ¡ 12 ¡ R. ¡Faghih ¡Mirzaee ¡and ¡M. ¡Eshghi ¡

1 if (b = 0) then : y ß ß 0 , return y Simplified Version of 2 u ß ß a , v ß ß b , B ß ß 0 , D ß ß 1 Binary Extended 3 while (u is even) do : u ß ß u/2 GCD Algorithm if (B is even) then : B ß ß B/2 for IDEA else : B ß ß (B-a)/2 4 while (v is even) do : v u , v , B , D v ß ß v/2 if (D is even) then : D ß ß D/2 Ø X i Specific Registers else : D ß ß (D-a)/2 Ø B , D : Negative Values 5 if (u ≥ v) then : u ß ß u-v , B ß ß B-D else : v ß ß v-u , D ß ß D-B Ø Sign Bits 6 if (u = 0) then : Ø 17bit Subtractor if (D < 0 ) then : D ß ß D+2 16 +1 y ß ß D , return y F 19 (D 2 +D 3 )X 2 [0]’X 0 [0]’T i : else : goto step 3 X 0 ß ß SHR[X 0 ] , Selector Operation Function X 2 ß ß SHR[X 2 ] , 0 SUB A-B X 0 S ß ß 0 , SC ß ß i 1 SUB+SHR (A-B)/2 Design ¡of ¡an ¡ASIP ¡IDEA ¡Crypto ¡Processor, ¡ 13 ¡ R. ¡Faghih ¡Mirzaee ¡and ¡M. ¡Eshghi ¡

100 GEK Addr1 101 CLA Testing & 102 LDD Addr2,0 Synthesis Results 103 QLA 8 104 STA Addr4 105 LDK Addr1,8 106 COD v Structural VHDL Code 107 DSZ Addr4 v FPGA Family : Virtex5 108 JMP 105 109 LDK Addr1,8 v Max. Frequency = 110.713MHz 110 FCD v Throughput ≈ 9.4Mbps 111 CLA 112 STD Addr3,0 - #Slice Registers #Slice LUTs #Fully used Bit Slices #Bonded IOBs Used 346 1348 312 66 Utilization 1% 7% 22% 16% Design ¡of ¡an ¡ASIP ¡IDEA ¡Crypto ¡Processor, ¡ 14 ¡ R. ¡Faghih ¡Mirzaee ¡and ¡M. ¡Eshghi ¡

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.