UMBC A B M A L F T U M B C I O M Y O T R 1 - PowerPoint PPT Presentation

Advanced VLSI Design Subsystem Design CMSC 491C/691C Control Control is the hard part of design. The regularity found in arithmetic and memory structures usually not present in control structures. Finite-State machines provide an organized

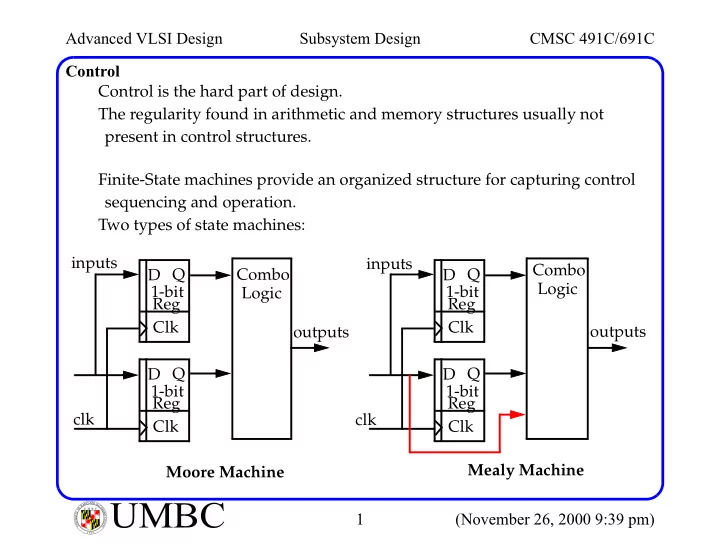

Advanced VLSI Design Subsystem Design CMSC 491C/691C Control Control is the hard part of design. The regularity found in arithmetic and memory structures usually not present in control structures. Finite-State machines provide an organized structure for capturing control sequencing and operation. Two types of state machines: inputs inputs Combo D Q Combo D Q Logic 1-bit 1-bit Logic Reg Reg Clk Clk outputs outputs D Q D Q 1-bit 1-bit Reg Reg clk clk Clk Clk Mealy Machine Moore Machine L A N R Y D UMBC A B M A L F T U M B C I O M Y O T R 1 (November 26, 2000 9:39 pm) I E S R C E O V U I N N U T Y 1 6 9 6

Advanced VLSI Design Subsystem Design CMSC 491C/691C Control State transition diagrams used to represent state machines. Toll-booth controller example: Idle Reset 00 A A A Wait-for-car-to-exit Wait-for-coin 10 01 C C A Inputs: Outputs: Reset Turn green-light on A (car in booth signal) C (Change OK) Write the state equations of the form: if (state == oldstate & condition) next-state = newstate. Rules for assigning state bits and output encoding method given in Weste and Eshraghian. L A N R Y D UMBC A B M A L F T U M B C I O M Y O T R 2 (November 26, 2000 9:39 pm) I E S R C E O V U I N N U T Y 1 6 9 6

Advanced VLSI Design Subsystem Design CMSC 491C/691C Control Control logic in CMOS is constructed in two main ways: • Two-level sum-of-products • Multilevel logic Two-level sum-of-products: PLA implementation: Regular structure for implementing combinational and sequential logic functions. We have examined how to construct combinational functions already. Sequential functions (finite-state machines) implementations are identical except that outputs are fed back to the inputs via registers. Pseudo n-MOS implementation main disadvantage is static power dissi- pation. Dynamic CMOS implementation involves suppling the AND plane and OR plane with clocks (see Weste and Eshraghian). L A N R Y D UMBC A B M A L F T U M B C I O M Y O T R 3 (November 26, 2000 9:39 pm) I E S R C E O V U I N N U T Y 1 6 9 6

Advanced VLSI Design Subsystem Design CMSC 491C/691C Control Multilevel Logic: Most commonly used method for implementing control logic in CMOS. Cascaded groups of regular gates such as INVERTERS, BUFFERS, NANDs, NORs, XORs and AOIs. CAD systems are highly effective at automatically minimizing the logic, making state assignments and synthesizing layouts as gate-arrays or stan- dard-cell layouts. L A N R Y D UMBC A B M A L F T U M B C I O M Y O T R 4 (November 26, 2000 9:39 pm) I E S R C E O V U I N N U T Y 1 6 9 6

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.