Processor Datapath Levels in Processor Design We can talk about - PowerPoint PPT Presentation

Processor Datapath Levels in Processor Design We can talk about design at a variety of levels (from low to high): Circuit design: transistors, resistors, capacitors, etc. Building gates, flip-flops, etc. Logic design: putting gates

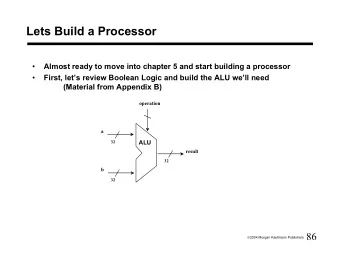

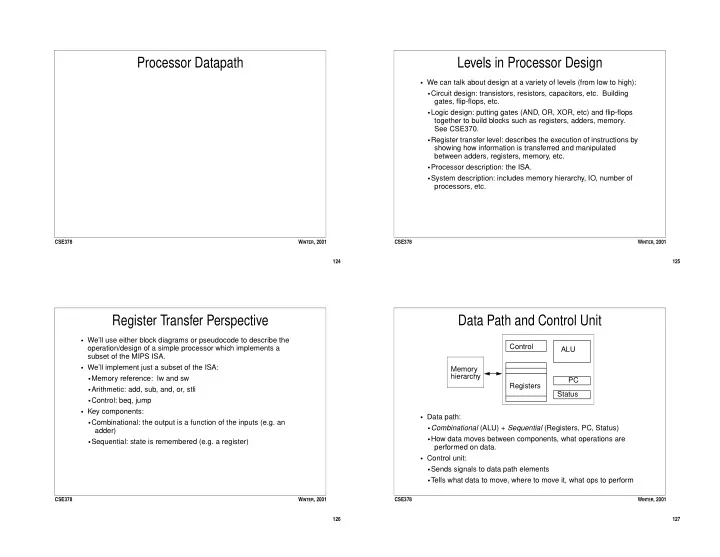

Processor Datapath Levels in Processor Design • We can talk about design at a variety of levels (from low to high): • Circuit design: transistors, resistors, capacitors, etc. Building gates, flip-flops, etc. • Logic design: putting gates (AND, OR, XOR, etc) and flip-flops together to build blocks such as registers, adders, memory. See CSE370. • Register transfer level: describes the execution of instructions by showing how information is transferred and manipulated between adders, registers, memory, etc. • Processor description: the ISA. • System description: includes memory hierarchy, IO, number of processors, etc. CSE378 W INTER , 2001 CSE378 W INTER , 2001 124 125 Register Transfer Perspective Data Path and Control Unit • We’ll use either block diagrams or pseudocode to describe the Control operation/design of a simple processor which implements a ALU subset of the MIPS ISA. • We’ll implement just a subset of the ISA: Memory hierarchy • Memory reference: lw and sw PC Registers • Arithmetic: add, sub, and, or, stli Status • Control: beq, jump • Key components: • Data path: • Combinational: the output is a function of the inputs (e.g. an • Combinational (ALU) + Sequential (Registers, PC, Status) adder) • How data moves between components, what operations are • Sequential: state is remembered (e.g. a register) performed on data. • Control unit: • Sends signals to data path elements • Tells what data to move, where to move it, what ops to perform CSE378 W INTER , 2001 CSE378 W INTER , 2001 126 127

Combinational Elements: ALU Synchronous Design • ALU computes (combinational) output from its two inputs. • Use a periodic clock, which controls when signals can be read and when they can be written. Values in storage elements can • Performs functions needed to execute arithmetic and logical only be updated on clock edges. instructions. • The clock determines when events occur, ie, when signals sent by • Combinational logic has a “critical path” which determines the control unit are obeyed in the datapath. length of time needed for the output to stabilize given stable inputs. (These days: ~1ns). Changes occur on every clock edge: Combinational State Element 1 State Element 2 ALU Logic operation Input 1 Output ALU Changes occur on clock edges when a write signal is asserted (this allows combinational logic to take several cycles): Input 2 Combinational State Element 1 State Element 2 Logic write write signal signal CSE378 W INTER , 2001 CSE378 W INTER , 2001 128 129 Building Blocks: Storage elements Building Blocks: Register File • The basic building block is the register. • Register file is an array of registers (32 in MIPS) • Our registers store 32 bits. • ISA tells us that we should be able to read 2 registers and write 1 register in a given instruction. • A register will only be written on the clock edge AND when the write control line is asserted. • We need to know which registers to read/write, and what data to write. • It can be read and written on the same clock, but the value read will be the OLD value. Read reg 1 Read data 1 Read reg 2 Registers Input Output Write Read bus bus reg data 2 Write data Write Write control control • Typical access time is around 1ns. CSE378 W INTER , 2001 CSE378 W INTER , 2001 130 131

Memory Instruction Fetch Datapath • Memory is like a register file, but much larger and slower. 4 • Can only read or write one location per cycle. Adder Read control Read PC address Read address Read Instruction data 1 Write Instruction address Memory Memory Write data • Our implementation will fully execute one instruction per clock Write control cycle: single cycle implementation. • The PC tells us the read address. • Typical access time (for primary memory) is around 50ns. For • On each clock edge, a new value for PC will be latched into the cache memory it is closer to 5ns. PC register. CSE378 W INTER , 2001 CSE378 W INTER , 2001 132 133 Datapath for R-type Instruction Datapath for Load/Store Read Read ALU control reg 1 operation Read Read data 1 Read Read ALU address Read operation reg 1 reg 2 Read Instruction ALU data 1 data 1 Registers Write Read address Write Instruction Read reg 2 ALU reg Registers data 2 Memory Write Write Read reg data 2 data Write Write Write data control data Write control Write Sign control 16 32 Ext. • The instruction bits name the read and write regs (rs, rt, rd). • On the clock edge, the data is read, which moves through the • The instruction bits tell us the registers to use (src/dest and base ALU, hopefully in time to be latched into the write port at the next register) and the 16 bit signed offset. clock edge. • We use the ALU to compute the effective address, which is passed along to the data memory. CSE378 W INTER , 2001 CSE378 W INTER , 2001 134 135

Datapath For Branch Combinational Elements: (De)Multiplexor • Multiplexor (mux) selects the value of one of its inputs to be PC + 4 routed to the output: Sum Adder Branch Target Shift Left M Output 2 or more 2 U inputs X Read ALU operation reg 1 Read data 1 Select Read To branch Instruction reg 2 ALU control signal Registers control logic Write Read reg data 2 • Demultiplexor routes its input to one of its outputs: Write data Write control Sign 16 32 D 2 or more Ext. input M outputs U X Select • Question: Why can’t we just use the ALU to compute the branch control signal target address? CSE378 W INTER , 2001 CSE378 W INTER , 2001 136 137 Combining Memory and R-type Adding Instruction Fetch Read Read ALU control operation reg 1 Read Read data 1 4 address Read Read Instruction m ALU data reg 2 Adder Registers Write u address Write x Read reg m data 2 Memory u Write Read data x Read ALU Write control operation data reg 1 Write Read Read Read control data 1 Write PC address address Read Read control m ALU reg 2 data Sign Registers Write u 16 32 Instruction Ext. address Write x Read reg data 2 m Instruction Memory u Memory Write data x Write Write data control Write control Sign 16 32 • Note that we add 2 muxes: Ext. • One to select the second ALU input • One to select the source for the register writeback (memory or ALU result) CSE378 W INTER , 2001 CSE378 W INTER , 2001 138 139

Full Datapath: Adding Branches Processor Control m u 4 x Adder Adder Shift Left 2 Read Read ALU control operation reg 1 Read Read Read data 1 PC address Read address Read m ALU reg 2 data Registers Write u Instruction address Write x Read reg data 2 m Instruction Memory u Memory Write data x Write data Write control Write control Sign 16 32 Ext. CSE378 W INTER , 2001 CSE378 W INTER , 2001 140 141 Adding Control Review of Instruction Format • Control Unit: • The opcode lives in bits 31-26 • Decodes instruciton opcode/function field • The two registers to read are always the rs (25-21) and rt (20-16) registers • Sends signals to the data path (muxes, reg file, memories) • For a load/store, we find the base register in the rs field (25-21) • Some controls come directly from the instruction: • The 16 bit offset (for branch or load/store) is in 15-0 • Register fields indicate which register to read/write • The destination register can be in one of two places: • Immediate field • Loads: rt field (20-16) • Building the control unit is not that complicated: • R-type: rd field (15-11) • Input signals (opcode/function) are specified by the ISA • This implies we’ll need a mux to select between these two fields. • Output signals can be identified easily from the opcode • We can use PLAs (see CSE370) to build hardwired control units CSE378 W INTER , 2001 CSE378 W INTER , 2001 142 143

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.