This Unit: Single-Cycle Datapath App App App Datapath storage - PowerPoint PPT Presentation

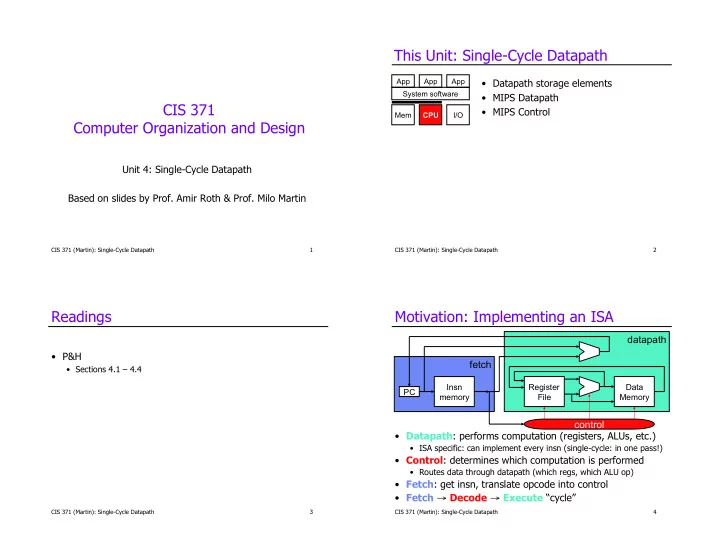

This Unit: Single-Cycle Datapath App App App Datapath storage elements System software MIPS Datapath CIS 371 MIPS Control Mem CPU I/O Computer Organization and Design Unit 4: Single-Cycle Datapath Based on slides by Prof. Amir

This Unit: Single-Cycle Datapath App App App • Datapath storage elements System software • MIPS Datapath CIS 371 • MIPS Control Mem CPU I/O Computer Organization and Design Unit 4: Single-Cycle Datapath Based on slides by Prof. Amir Roth & Prof. Milo Martin CIS 371 (Martin): Single-Cycle Datapath 1 CIS 371 (Martin): Single-Cycle Datapath 2 Readings Motivation: Implementing an ISA datapath • P&H fetch • Sections 4.1 – 4.4 Insn Register Data PC memory File Memory control • Datapath : performs computation (registers, ALUs, etc.) • ISA specific: can implement every insn (single-cycle: in one pass!) • Control : determines which computation is performed • Routes data through datapath (which regs, which ALU op) • Fetch : get insn, translate opcode into control • Fetch → Decode → Execute “cycle” CIS 371 (Martin): Single-Cycle Datapath 3 CIS 371 (Martin): Single-Cycle Datapath 4

Two Types of Components Example Datapath datapath fetch Insn Register Data PC memory File Memory control • Purely combinational : stateless computation • ALUs, muxes, control • Arbitrary Boolean functions • Combinational/sequential : storage • PC, insn/data memories, register file • Internally contain some combinational components CIS 371 (Martin): Single-Cycle Datapath 5 CIS 371 (Martin): Digital Logic & Hardware Description 6 Register File RegSource1Val RegDestVal Register File RegSource2Val WE RD RS1 RS2 • Register file : M N-bit storage words • Multiplexed input/output: data buses write/read “random” word • “Port” : set of buses for accessing a random word in array Datapath Storage Elements • Data bus (N-bits) + address bus (log 2 M-bits) + optional WE bit • P ports = P parallel and independent accesses • MIPS integer register file • 32 32-bit words, two read ports + one write port (why?) CIS 371 (Martin): Single-Cycle Datapath 7 CIS 371 (Martin): Single-Cycle Datapath 8

Decoder Decoder in Verilog (1 of 2) • Decoder : converts binary integer to “1-hot” representation module decoder_2_to_4 (binary_in, onehot_out); ! input [1:0] binary_in; ! • Binary representation of 0…2 N –1: N bits output [3:0] onehot_out; ! • 1 hot representation of 0…2 N –1: 2 N bits assign onehot_out[0] = (~binary_in[0] & ~binary_in[1]); ! • J represented as J th bit 1, all other bits zero assign onehot_out[1] = (~binary_in[0] & binary_in[1]); ! • Example below: 2-to-4 decoder assign onehot_out[2] = (binary_in[0] & ~binary_in[1]); ! B[0] assign onehot_out[3] = (binary_in[0] & binary_in[1]); ! 1H[0] endmodule ! B[1] 1H[1] • Is there a simpler way? B 1H 1H[2] 1H[3] CIS 371 (Martin): Single-Cycle Datapath 9 CIS 371 (Martin): Single-Cycle Datapath 10 Decoder in Verilog (2 of 2) Register File Interface module decoder_2_to_4 (binary_in, onehot_out); ! input [1:0] binary_in; ! output [3:0] onehot_out; ! RDestVal assign onehot_out[0] = (binary_in == 2’d0); ! RSrc2Val assign onehot_out[1] = (binary_in == 2’d1); ! assign onehot_out[2] = (binary_in == 2’d2); ! assign onehot_out[3] = (binary_in == 2’d3); ! RSrc1Val endmodule ! • How is “a == b“ implemented for vectors? RS1 WE RD RS2 • |(a ^ b) (this is an “and” reduction of bitwise “a xor b”) • Inputs: • When one of the inputs to “==“ is a constant • Simplifies to simpler inverter on bits with “one” in constant • RS1, RS2 (reg. sources to read), RD (reg. destination to write) • WE (write enable), RDestVal (value to write) • Exactly what was on previous slide! • Outputs: RSrc1Val, RSrc2Val (value of RS1 & RS2 registers) CIS 371 (Martin): Single-Cycle Datapath 11 CIS 371 (Martin): Single-Cycle Datapath 12

Register File: Four Registers Add a Read Port RSrc1Val RS1 • Output of each register into 4to1 mux (RSrc1Val) • Register file with four registers • RS1 is select input of RSrc1Val mux CIS 371 (Martin): Single-Cycle Datapath 13 CIS 371 (Martin): Single-Cycle Datapath 14 Add Another Read Port Add a Write Port RDestVal RSrc2Val RSrc2Val RSrc1Val RSrc1Val RS1 RS1 RS2 WE RD RS2 • Output of each register into another 4to1 mux (RSrc2Val) • Input RegDestVal into each register • RS2 is select input of RSrc2Val mux • Enable only one register’s WE: (Decoded RD) & (WE) • What if we needed two write ports? CIS 371 (Martin): Single-Cycle Datapath 15 CIS 371 (Martin): Single-Cycle Datapath 16

Register File Interface (Verilog) Register File Interface (Verilog) module regfile4(rs1, rs1val, rs2, rs2val, rd, rdval, we, rst, clk); ! module regfile4(rs1, rs1val, rs2, rs2val, rd, rdval, we, rst, clk); ! parameter n = 1; ! input [1:0] rs1, rs2, rd; ! input [1:0] rs1, rs2, rd; ! input we, rst, clk; ! input we, rst, clk; ! input [15:0] rdval; ! input [n-1:0] rdval; ! output [15:0] rs1val, rs2val; ! output [n-1:0] rs1val, rs2val; ! … ! endmodule ! • Building block modules: • module register (out, in, wen, rst, clk); ! • module decoder_2_to_4 (binary_in, onehot_out) ! • module Nbit_mux4to1 (sel, a, b, c, d, out); ! endmodule ! • Warning: this code not tested, may contain typos, do not blindly trust! CIS 371 (Martin): Single-Cycle Datapath 17 CIS 371 (Martin): Single-Cycle Datapath 18 [intentionally blank] [intentionally blank] CIS 371 (Martin): Single-Cycle Datapath 19 CIS 371 (Martin): Single-Cycle Datapath 20

Register File Interface (Verilog) Register File: Four Registers (Verilog) module regfile4(rs1, rs1val, rs2, rs2val, rd, rdval, we, rst, clk); ! module regfile4(rs1, rs1val, rs2, rs2val, rd, rdval, we, rst, clk); ! parameter n = 1; ! parameter n = 1; ! input [1:0] rs1, rs2, rd; ! input [1:0] rs1, rs2, rd; ! input we, rst, clk; ! input we, rst, clk; ! input [n-1:0] rdval; ! input [n-1:0] rdval; ! output [n-1:0] rs1val, rs2val; ! output [n-1:0] rs1val, rs2val; ! wire [n-1:0] r0v, r1v, r2v, r3v; ! Nbit_reg #(n) r0 (r0v, , , rst, clk); ! Nbit_reg #(n) r1 (r1v, , , rst, clk); ! Nbit_reg #(n) r2 (r2v, , , rst, clk); ! Nbit_reg #(n) r3 (r3v, , , rst, clk); ! endmodule ! endmodule ! • Warning: this code not tested, may contain typos, do not blindly trust! • Warning: this code not tested, may contain typos, do not blindly trust! CIS 371 (Martin): Single-Cycle Datapath 21 CIS 371 (Martin): Single-Cycle Datapath 22 Add a Read Port (Verilog) Add Another Read Port (Verilog) module regfile4(rs1, rs1val, rs2, rs2val, rd, rdval, we, rst, clk); ! module regfile4(rs1, rs1val, rs2, rs2val, rd, rdval, we, rst, clk); ! parameter n = 1; ! parameter n = 1; ! input [1:0] rs1, rs2, rd; ! input [1:0] rs1, rs2, rd; ! input we, rst, clk; ! input we, rst, clk; ! input [n-1:0] rdval; ! input [n-1:0] rdval; ! output [n-1:0] rs1val, rs2val; ! output [n-1:0] rs1val, rs2val; ! wire [n-1:0] r0v, r1v, r2v, r3v; ! wire [n-1:0] r0v, r1v, r2v, r3v; ! Nbit_reg #(n) r0 (r0v, , , rst, clk); ! Nbit_reg #(n) r0 (r0v, , , rst, clk); ! Nbit_reg #(n) r1 (r1v, , , rst, clk); ! Nbit_reg #(n) r1 (r1v, , , rst, clk); ! Nbit_reg #(n) r2 (r2v, , , rst, clk); ! Nbit_reg #(n) r2 (r2v, , , rst, clk); ! Nbit_reg #(n) r3 (r3v, , , rst, clk); ! Nbit_reg #(n) r3 (r3v, , , rst, clk); ! Nbit_mux4to1 #(n) mux1 (rs1, r0v, r1v, r2v, r3v, rs1val); ! Nbit_mux4to1 #(n) mux1 (rs1, r0v, r1v, r2v, r3v, rs1val); ! Nbit_mux4to1 #(n) mux2 (rs2, r0v, r1v, r2v, r3v, rs2val); ! endmodule endmodule ! • Warning: this code not tested, may contain typos, do not blindly trust! • Warning: this code not tested, may contain typos, do not blindly trust! CIS 371 (Martin): Single-Cycle Datapath 23 CIS 371 (Martin): Single-Cycle Datapath 24

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.

![Load/Store Instructions Address computation: RD := M(sext(imm)+RS1) means: RD M [ adr ]](https://c.sambuz.com/788801/load-store-instructions-s.webp)