Delay Test Virendra Singh Associate Professor C omputer A - PowerPoint PPT Presentation

Delay Test Virendra Singh Associate Professor C omputer A rchitecture and D ependable S ystems L ab Department of Electrical Engineering Indian Institute of Technology Bombay http://www.ee.iitb.ac.in/~viren/ E-mail: viren@ee.iitb.ac.in

Delay Test Virendra Singh Associate Professor C omputer A rchitecture and D ependable S ystems L ab Department of Electrical Engineering Indian Institute of Technology Bombay http://www.ee.iitb.ac.in/~viren/ E-mail: viren@ee.iitb.ac.in EE-709: Testing & Verification of VLSI Circuits Lecture 27 (26 March 2013) CADSL

Definitions Controlling value (cv) : An input of a gate is said to have a controlling value if it uniquely determines the output of the gate independent of other inputs For example, 0 for AND or NAND A path R in a circuit is a sequence (g 0 g 1 ……g r ), where g 0 is a PI, g 1 g 2 .. are gate outputs, g r is a PO CADSL 25 Mar 2013 EE-709@IITB 2

Definitions An on-input of path R is a connection between two gates along path R A side-input (off-input) of path R is any connection to a gate along path R other than its on-input A path that starts at a primary input and ends at a side-input of path R is called a side-path of R CADSL 25 Mar 2013 EE-709@IITB 3

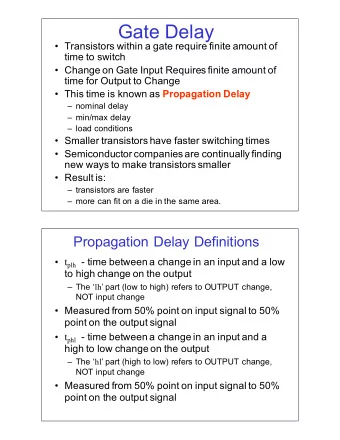

Transition Delay Fault Two faults per gate; slow-to-rise and slow-to-fall. Tests are similar to stuck-at fault tests. For example, a line is initialized to 0 and then tested for s-a-0 fault to detect slow-to-rise transition fault. Models spot (or gross) delay defects. CADSL 25 Mar 2013 EE-709@IITB 4

Transition Delay Test Path P1 1 1 D D P2 1 1 D’ D D 1 2 3 SA0 P3 1 CADSL 25 Mar 2013 EE-709@IITB 5

Transition Delay Test Single lumped inertial delay modeled for each gate PI transitions assumed to occur without time skew Path P1 0 1 D 0 D’ P2 1 D’ D D 1 2 3 SA0 P3 1 CADSL 25 Mar 2013 EE-709@IITB 6

Transition Delay Test Path P1 X0 1 0D 00 1D’ P2 1 1D’ 0D 01 0D 2 3 SA0 P3 01 CADSL 25 Mar 2013 EE-709@IITB 7

Path Delay Fault Cheng’s classification Robustly testable Non-robustly (NR) testable Functional sensitizable (FS) testable Functionally unsensitizable (functionally redundant ) CADSL 25 Mar 2013 EE-709@IITB 8

Path Delay Fault Robust testable : detect target PDF independent of delays in rest of the circuit. It must satisfies the following conditions It launches the desired transition at primary input All side inputs of target path settle to non- controlling values under V 2 Whenever the logic transition at an on-input is from non-controlling to controlling value (ncv to cv), each side-input should maintain steady non-controlling value (ncv) CADSL 25 Mar 2013 EE-709@IITB 9

Path Delay Fault Robust testable CADSL 25 Mar 2013 EE-709@IITB 10

Path Delay Fault Non-Robust (NR ) testable : It must satisfies the following conditions It launches the desired transition at primary input All side-inputs of target path settle to non- controlling values (ncv) under V 2 CADSL 25 Mar 2013 EE-709@IITB 11

Path Delay Fault Functional Sensitizable (FS) testable: Detection of faults on paths that are sensitizable under FS criterion depends on the delays on signals outside the target path It must satisfies the following conditions It launches the desired transition at primary input Whenever the logic transition at an on-input is non-controlling value (ncv) under vector V 2 , each side-input should have non- controlling value (ncv) under V 2 CADSL 25 Mar 2013 EE-709@IITB 12

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.